咱们接着上篇文章持续学习,前次提到了两种赋值句子,让咱们接着往下学。

1、块句子

块句子包含两种,一个是次序块,一个是并行块。

(1)次序快

次序快就比如C言语里的大括号“{ }”,在Verilog语法中,用begin…end替代。这儿只需要知道,在begin…end中心的句子是次序履行的就行了。

(2)并行块

并行块能够算是一个新的知识点,与次序块最大的不同便是并行块中的句子是一起开端履行的,要想操控句子的先后次序,能够加延时句子操控。这种并行块是用fork…join句子描绘。

2、条件句子

条件句子这儿不说,和C言语相同。就说一点主见事项。

在运用条件句子时,要注意句子的严整与封闭性。和C言语不同,举个比如

always @(al or d)

begin

if(al==1) q=d;

end

这个比如是说,当al上升沿到来时,d的值赋给q,那么当al=0时又是什么状况呢,事实上,在always块中,假如没有给变量赋值,这个变量就会坚持原值,也便是生成了一个锁存器。为了防止这种状况的产生,咱们一般这样写

always @(al or d)

begin

if(al==1) q=d;

else q=0;

end

同样在case句子中也要加上default句子防止锁存器的生成,这样能够使规划者愈加清晰的规划方针,也提高了程序的可读性。

3、case句子

case句子要注意几点,只挑几点重要的,其他的不说了

(1)case句子分项后的表达式的值有必要相同,不然就会出现问题,例如上面图片上的result。

(2)与C言语不同,与某一项case句子匹配后,就会跳出case句子,这儿没有break句子。

(3)case句子的一切表达式位宽有必要持平,例如上图都是16位整型,假如不加以阐明,体系会以默认值32位操控表达式位宽。

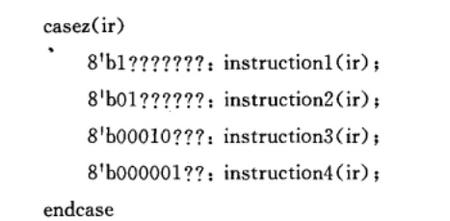

下面是case,casez,case句子的真值表

这个表其实仍是很好记的

case句子,只需匹配才出“1”

casez句子除了匹配出“1”之外,别的只需遇到“z”就出“1”

case句子除了匹配出“1”之外,别的只需遇到“z”或“x”就出“1”

上图就用到了casez句子来处理不必要考虑的值,这样就能够灵敏的设置对信号的默写位进行比较。

下面写了一个小比如来操练一下

运用case句子完成一个四选一多路选择器

module xiaomo(a1,a2,a3,a4,out,s1,s2);

input a1,a2,a3,a4;

input s1,s2;

reg out; //把输出变量声明为寄存器类型

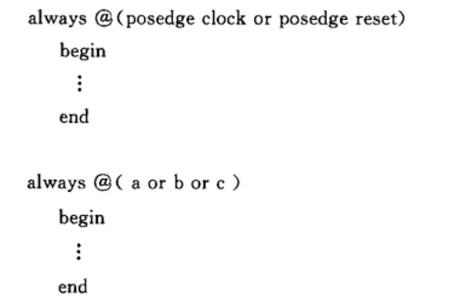

always @(s1 or s2 or a1 or a2 or a3 or a4 or out) //任何信号的改变都会引起输出变量的从头核算

begin

case ({s1,s2}) //位拼接运算

2’b00: out=a1;

2’b01: out=a2;

2’b10: out=a3;

2’b11: out=a4;

default: out=1’bx; //坚持句子的严整性

endcase

end

endmodule