Design and analysis of a high-performance lsolated amplifier

容浚源,李颂,张辽,周泽坤,罗萍,张波

(电子科技大学 电子科学与工程学院,四川 成都 610000)

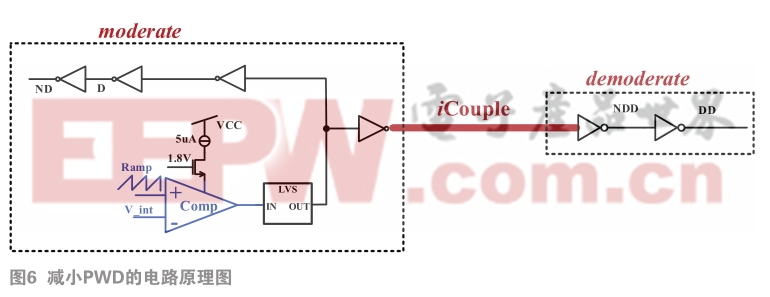

摘要:这款阻隔运算放大器分为调制部分和解调部分,调制部分把输入的模仿信号PWM调制为20MHz的方波信号,经过ADI公司的icouple®磁耦合模块传输到解调部分,解调部分将方波信号解调为模仿的电压信号。此款运放经过选用高速比较电路、离散采样网络和高精度基准源等优化计划,终究能够完结在0V~2.5V准确的1:1传输,频率呼应为3 MHz,输出纹波小于3 mV。

关键词:磁阻隔;PWM调制解调;高速调制;噪声消除

*竞赛荣誉:全国大学生集成电路立异创业大赛(ADI杯)全国特等奖

0 导言

本团队规划体系:在输入电压是0V~2.5V的模仿信号中,完结衬底阻隔的情况下能够传输增益为1的信号操作,且相位带广大,线性度好,噪声小,具有较小的温度系数,一起为了使芯片具有更好的带宽特性,规划体系时将作业频率进步到20 MHz。

本体系首要由以下三部分组成,别离是:

House keeping模块和基准模块,产生基准电压,供应电流偏置模块IBIAS别离产生尾电流偏置,作为其他电路的偏置电流,基准后边接LDO型的分压电路产生带驱动才能和抗搅扰才能的基准电压,用于完结调制解调,还有产生等腰三角纹波RAMP用于比较器。需求留意的是,在阻隔运放的两边别离都需求一个housekeeping电路。

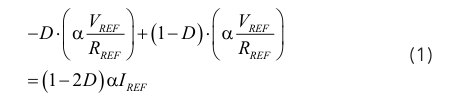

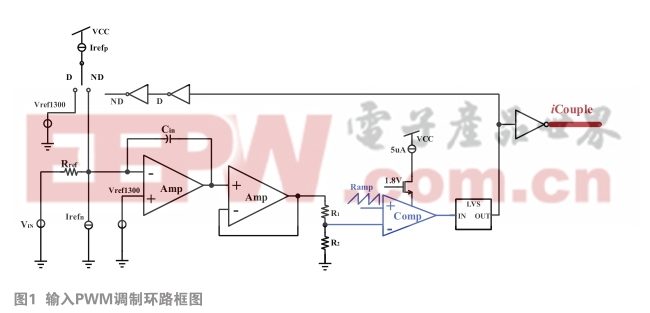

输入PWM调制环路,如图1所示,其功用是将输入电压V IN 转化为20 MHz的信息以占空比的办法输出至第三功用模块;

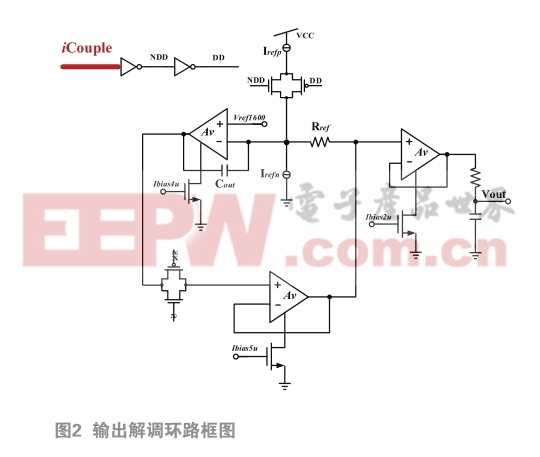

输出解调环路,如图 0-2所示,用于将频率为20MHz的占空比信息转化还原为模仿的输出电压

1 调制环路的直流作业点剖析

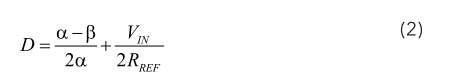

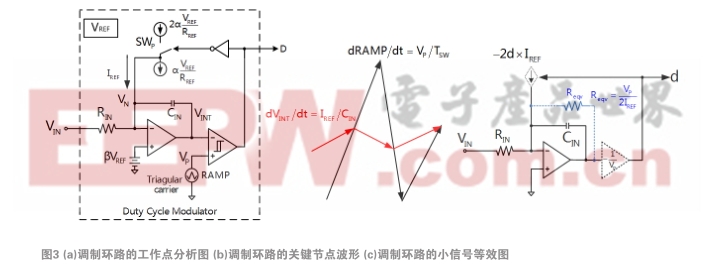

如图3(a)所示,安稳时刻在疏忽周期内的纹波时,运放负端电压V IN 应钳位到正端电压βV REF 。接下来剖析V IN 节点上的电流改动,在一个周期内D有用的时间段,开关SW P 断开,电流源抽走α(V REF /R REF );在一个周期内1-D的时间段,开关SW P 闭合,两个电流源叠加效果对V IN 节点充电流αV REF /R REF 。那么在一个周期内电流源对V IN 节点供给的电流为:

对上式化简可得:

为了便利核算,取V REF =1 V,并核算α和β的值。

依据使用条件别离代入V IN =0 V和V IN =2.5 V,再考虑非抱负要素将会影响占空比的产生和输出电压的复现,避开0%和100%占空比的呈现,留有10%的余量即D IN =10%和D MAX =90%,化简可得:α=1.56,β=1.25。为了便利基准电压的产生,取α=1.6,β=1.3,终究输入V IN =0 V时,占空比D IN =9.37%;输入V IN =2.5 V时,占空比D MAX =93.6%。

2 调制环路的沟通安稳性剖析

剖析调制环路的沟通安稳性能够从两方面下手,一种是从瞬态呼应的视点剖析,另一种是从环路增益的视点剖析。

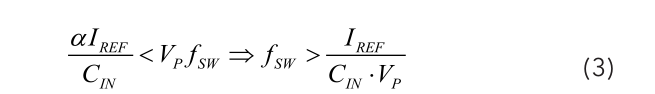

从瞬态呼应的视点剖析,需求V INT 的改动速度足够慢,确保每周期V INT 和纹波RAMP比较到。环路结构如图3(a)所示,在D和1-D的时间段内对V INT 节点充放电电流巨细都为αI REF ,则V INT 改动斜率为αI REF /C IN ;假定RAMP为抱负锯齿波,其峰峰值电压差为V P ,则RAMP斜率为V P /T SW =V P f SW ,则二者的斜率有必要满意如下联系,如图3(b)所示:

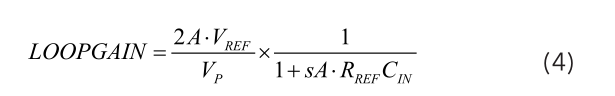

从环路增益视点剖析,如图 0-3(c)所示剖析环路增益有,

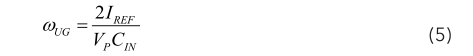

则环路增益下降为1时对应的角频率为

将式代入式有

另一方面,取运放AMP输出到V N 节点电流的增益如下:

依据图 0-3(c)的等效联系且有:

环路安稳即设法下降ω UG ,即增大R eq1 或许增大C IN 。可是C IN 不该成为首要增大的途径,由于C IN 一起也是运放AMP的密勒电容,强行增大C IN 将使其成为运放本身小环路的不行忽视极点,反而影响调制环路的相位裕度乃至环路的安稳性;

由R eq1 的公式可知:经过增大R REF 和V P 能够增大R eq1 ,可是R REF 不宜过大,原因是不简单匹配且简单引进各种寄生效应;V P 受限于比较器的共模输入规模,且V P 过大也难于产生高频纹波电路。

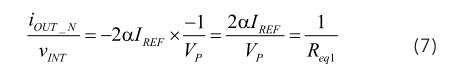

因而本体系将作业频率为20 MHz,为了进步比较器的呼应速度,选用在1.8 V电源电压构成的比较器,纹波值为0.6 V~1.2 V,一起选用了占空比50%的三角波替代传统使用中的锯齿波,一方面更简单产生高频纹波,另一方面纹波的斜率变为本来的2倍等效添加R eq1 。为此电路需求从5 V电源轨转换为1.8 V电源轨,电路规划选用1/3分压结构,而电路如图4所示。由于RAMP的 电 压 上 下 限 为 0 . 6V~1.2 V,Vint的动态规模为1.8 V~3.6 V,不会形成后续的低耐压比较器电路过压。

在每个作业周期内,当比较器取得比较成果后,经过快速的电平位移电路LVS将电源轨敏捷康复到5 V进行传输或许反应,终究V IN 转化为频率20 MHz的信息,并以占空比的办法传输。

3 解调环路的直流作业点剖析

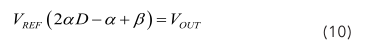

经过将运放的负输入端钳位到βV REF ,能够得到安稳态联系,有

因而输入等于输出,电压完结传输。

解调环路的沟通安稳性剖析与剖析调制环路的办法相同,依据图2,能够先从各部分的增益下手即算整个环路的环路增益。

本体系选用离散采样电压进行反应,首要效果是使用开关的效果用采样的办法按捺运放输出在周期内的纹波反应到真实的输出,关于采样模块的离散传输函数为1

在频率低于1/π倍的f SW 时(奈奎斯特定理,但这是有必要要完结的),在s域的等效增益也为1,因而对环路没有影响。值得阐明的是,两级采样的增益也为1,可是在s域是相当于引进相位滞后,会令环路的相位裕度变小乃至不安稳。采样成果到输出电压经过一个buffer添加带载才能,避免输出节点被电流镜的切换影响。

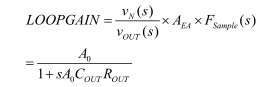

在本规划下,解调环路的环路增益LOOPGAIN为

为了调值环路和解调环路匹配,选取C OUT =C IN ,R OUT =R IN =R ref ,因而有f UG 为

因而采样体系对环路安稳性和连续性建模没有影响且环路安稳。

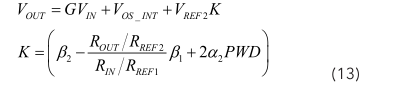

减小失配的战略剖析与实施计划考虑输出电压差错,输出电压与输入电压联系为

由式可得,引起差错的只要两项,即V OS_INT 和PWD,其间,V OS_INT 来源于调制环路和解调环路各自引进的差错;PWD来源于传输过程中占空比改动,因而导致调制端的反应占空比和解调端接纳的占空比信息不相同。

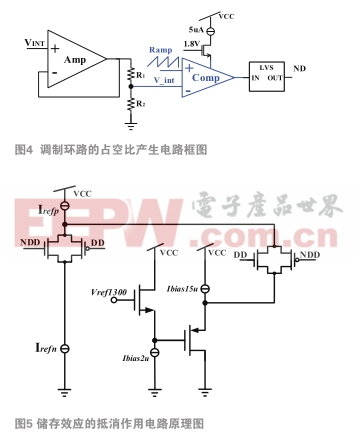

此文减小VOS_INT的首要办法除了进步环路增益还有削减开关动作的搅扰。如图5所示,当开关断开今后,图中节点Irefp将会被充电到5 V,鄙人周期开关从头闭合时,将会注入一股额定的电流对运放输入端进行充电,而这股电荷由于开关断开而不会被抽走,相当于引进很大的失配。为了消除这种影响,在开关断开的时分另一路的开关闭合,源随器将节点Irefp节点钳位至βV REF ,当开关从头再翻开时,额定注入的电流将会削减。

在削减PWD方面,本规划经过结构相同传输电路结构的办法,尽量确保从level-shifter别离到调制端和解调端电流镜的占空比信号的延时相同,尽可能确保两边的占空比信息持平以减小PWD从而减小体系失配。

别的,开关频率上的纹波也是值得消除的,因而输出电路选用滤波电路削减开关频率上的纹波巨细,取得更安稳的输出。

4 体系参数仿真与成果

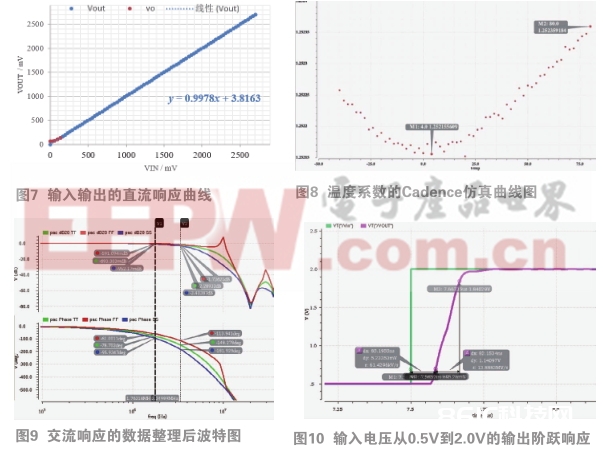

V IN 输入一个直流电压电平,仿真到安稳状况后的3us时间内用软件核算这3 us的输出均匀值(体系从启动到安稳只需求7 us),输入从0 V~2.9 V扫描90个点,cadence软件主动生成曲线如图7所示。

从图中能够看到输入低压(约0 mV~250 mV)的几个点输出有失配,首要原因在于解调端运放摆幅约束决议的,运放下摆幅为Vov约为250 mV,和仿真成果对应;能够得到增益差错为-0.22%,小于要求的0.25%;均匀输入输出失配电压是3.8163 mV,小于5 mV。

去 掉 图 中 过 度 偏 离 曲 线 的 M 2 点 , 取 最 小 值V O,MIN =1.25216 V,最大值V O,MAX =1.25235 V,均匀值AVG=1.25225。均匀温度改动速度为1.5 μV/℃,温度系数为1.278 ppm/℃。

图9是使用PAC仿真后得到的三个conner的波特图,从上图可得若以-3 dB处作为极点,则极点方位大概在3.3 MHz,若以90度相位滞后作为极点方位,则极点呈现在1.8 MHz左右。

图10 是输入电压从0.5 V到2.0 V阶跃跳变,输出电压进行相应的波形,跳变在0.01 ns内完结,从图中可得输入到输出产生10%改动的呼应延时是85.2 ns,输出10%到90%的上升延时是82.15 ns。

5 定论

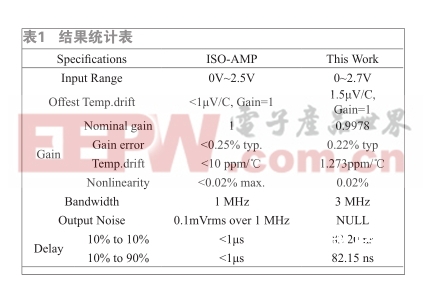

如表1为一切成果统计表。

参考文献

[1] Razavi, Behard. Design of analog CMOS integrated circuits= 模仿CMOS集成电路规划[M]. 清华大学出版社, 2005.

[2] Zhou Z K, Shi Y, Huang Z, et al. A 1.6V, 5-ppm/C, C Curvature-Compensated BandgapReference [J]. Circuit & Systems I Regular Papers IEEE Transactions, 2012, 59(4): 677-684.

[3] Zhou Z K, Zhu P S, Shi Y, et al. A CMOS Voltage Reference Based onMutual Compensation of Vtn and Vtp [J]. IEEE Transactions on Circuits &Systems II Express Briefs, 2012, 59(6): 341-345.

[4] Bult K, Geelen G J G M. A fast settling CMOS op amp for SC circuitswith 90-dB DC gain [J]. IEEE Journal of Solid-State Circuit, 2002:108-109.

[5] Razavi B. Rotary TravelingWave Oscillator Arrays: A New ClockTechnolgy [C]// Wiley-IEEE Press, 2009:318-329.

本文来源于科技期刊《电子产品世界》2019年第5期第56页,欢迎您写论文时引证,并注明出处