人们对宽带服务的带宽要求越来越高,促进芯片供货商运用更多的高速串行收发器。因而,下一代运用选用了多种数据速率,从几Mbps 到数百Gbps,在一种设备中集成了多种协议和服务。以太网等敏捷开展的标准以及对进步数据速率的需求使得高速收发器成为首要的功用断定依据。标准单元ASIC 和ASSP 不具有人们需求的灵敏性,其本钱和危险无法让用户及时完成技能立异。本文介绍带有收发器的全系列40–nmFPGA 和ASIC,发挥前沿技能优势,在前一代立异基础上,处理下一代体系难题。

导言

现代意义上的互联网尽管只阅历了十几年的时刻,却现已成为技能立异和带宽添加的首要推进力气。更新现有通讯体系以及新运用的呈现要求选用更大的宽带和更高的数据速率。今日,以视频为主的网络下载和点对点网络衔接( 文件同享) 占用了80% 的带宽。流媒体( 视频点播电影和电视)、IP 承载视频和互联网游戏等新运用占用的带宽不到10% 。考虑到这些要素,互联网仍处于开展初期,往后将持续微弱添加。

商场上最近推出的通讯设备现已开端向40 乃至100 千兆以太网(GbE) 端口过渡,以更低的本钱和功耗,在更紧凑的封装中完成更大的带宽。而且,摩尔定律还在不断推进着半导体职业开展,集成电路上的晶体管数量每两年就会加倍。新一代产品运用45-nm 或许40–nm 工艺来集成更多的功用,进步每一功用的作业功用和逻辑密度,下降功耗,而满意日益添加的带宽需求的要害则是更多、更快的高速串行收发器。

本文介绍高速串行收发器的开展趋势,以及体系规划人员和规划人员所面对的应战。文章还回忆了某些特别的商场需求,为满意这些需求,可编程逻辑器材(PLD) 供货商有必要供给带有收发器的多种产品组合。这些器材具有丰厚的逻辑、特性和I/O 功用,客户运用它们能够开宣布满意各种功用、功耗和本钱方针的产品。

高速收发器技能的开展趋势进步高速串行收发器的数据速率以及器材中收发器的数量能够完成更大的带宽和更高的数据速率。运用以

下技能能够获得带宽到达100G 的接口:

■ 10 个10.3-Gbps 收发器(CAUI 协议)

■ 20 个6.375-Gbps 收发器(Interlaken 协议)

■ 40 个3.125-Gbps 收发器(XAUI 协议)

■ 100 个1.25-Gbps 收发器(SGMII 协议,留意,这仅仅用于演示意图,并不有用)

考虑到每个器材一切输入和输出数据通道的两端口需求,假如收发器数据速率不能相应的进步,即使是选用最现代的工艺技能也难以满意收发器的数量要求。

许多体系混合了DSP 模块、操控处理器、ASSP、ASIC 和FPGA。体系规划人员面对的应战是对体系进行区分,把这些器材衔接起来,以满意运用功用和带宽要求。在许多情况下,因为ASSP 和ASIC 技能立异开展较慢,无法完成更快的接口。另一应战是这些器材所供给的各类协议,规划人员不得不献身功用,从头运用本来的接口。这一般通过桥接器材――传统的FPGA,衔接本来的协议和新协议。处理这些问题终究会下降体系本钱。

带有收发器的数据链路不光支撑更高的数据吞吐量,而且成效十分高,进一步进步了体系集成度,成为体系的要害组成部分。串化器/ 解串器(SERDES) 收发器是代替原有并行技能一切必要选用的技能。通过运用收

发器技能,规划人员能够处理当今高速数据链路规划中的要害问题:

■ 信号完好性:相关于并行接口,串行接口的延时和偏移都比较低。在串行协议运用,以及驱动背板方面,要求收发器具有优异的信号完好性,较低的颤动和误码率(BER)。

选用带有收发器的全系列40-nm FPGA 和ASIC 完成立异规划Altera 公司

2

■ 杂乱的电路板:运用串行接口能够减小电路板面积,削减所运用的电路板元件数量以及电路板层数。例如, PCI Express (PCIe) 接口将引脚和电路板面积削减了50%,而带宽进步了一倍。

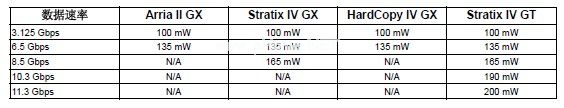

■ 功耗和散热:串行接口的功耗要低于并行接口。例如,Stratix IV GT FPGA 的10G 接口在10.3 Gbps 时的功耗为190 mW, Altera 40-nm 收发器上的收发器 PMA 功率。表1 具体列出了40-nm 工艺节点各种数据速率下的功耗。

总归,体系规划人员面对三种首要应战:

■ 在进步带宽和数据速率时,需求更多、更快的收发器。

■ 既有本来的高速协议,又有各种不断开展的新标准。

■ 契合背板和协议要求需求有优异的信号完好性。

收发器接口是体系规划人员首先要考虑的要害要素,而器材挑选取决于所能够供给的功用、功用、功耗和本钱方针。终究,必定的商场需求决议了收发器系列产品最适宜的功用。

商场需求

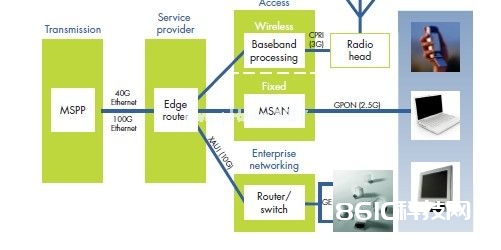

图1 显现了运用以太网协议的几个比如,现在的通讯基础设施中运用了收发器。网络中的每一部分都运用

了串行收发器技能,可是有不同的带宽要求。越接近用户侧,本钱和功耗就越灵敏,一起,带宽也在下降,

收发器速率和数量也在削减。此外,跟着实践运用中处理需求的改动,器材密度和特性的联系也在不断变

化。

图1. 通讯基础设施中的收发器

表1. PMA 收发器功耗/ 通道比照

3

固网接入、传输和网络设备

以太网现已开展成为当今运用最广泛的物理层和链路层协议。而作为IEEE 标准802.3ae 于2002 年发布的10GbE 是现在最快的标准, IEEE正在拟定40GbE和100GbE 以太网标准。网络现已向数据包传输和全以太网设备过渡,运用规模包含数据包处理和流量办理功用为主的桥接和全数据通道处理等(1)。依据网络中接近用户的程度以及方位,带宽从10 Gbps 至20 Gbps 开展到 40 Gbps 至80 Gbps,乃至是100 Gbps。并不存在能够满意一切需求的处理计划,因而,设备有必要能够支撑不同的密度、特性、功用、功耗和本钱方针。

要害需求推进了技能立异,包含对集成10G 收发器、高密度和高功用的需求,以及对以太网、GPON、CEI-6/Interlaken 和SONET/SDH 等协议标准的支撑。

无线设备

曩昔,无线标准( 空中接口) 在开展进程中选用了不同的技能和物理通道,可是,关于3.9G/4G,更大的载波带宽(20 MHz) 使得一切首要空中新接口运用OFDMA 技能。尽管正交频分复用多址接入/ 多输入多输出(OFMDA-MIMO) 办法有可能在不久的将来完成技能交融,但现在的标准仍在不断开展,持续得以施行。

首要的无线需求包含在同一体系中对多种标准的支撑,新一代体系结构中较强的信号处理才能,削减体系总延时等,一切这些需求都要求进一步进步集成度。而且,无线处理计划有必要能够灵敏的延伸到名为毫轻轻基站( 以及轻轻基站、微基站和宏基站等) 的家庭基站中。这些商场和技能要求推进了高度集成计划的开展,终究成为芯片体系(SoC)。而且,这些收发器PLD 所具有的长处和其他处理计划具有可比性,乃至优于其他计划:

■ 在用户数量或许每单元吞吐量上的本钱和功用

■ 每Mbps 和每mm2 功耗和面积

■ 不同空中接口和协议的芯片间、卡对卡以及机箱之间接口高速收发器的灵敏性和可更新才能

此外,很难有能够满意一切需求的通用处理计划。推进技能立异的要害需求包含更高的集成度,更低的本钱,更好的功用,集成了DSP 功用的信号处理才能,以及支撑CPRI/OBSAI 和Serial RapidIO® 等专用协议。

军事、播送、核算机和存储、测验和医疗,以及其他商场范畴

其他商场范畴对收发器的需求各有不同,需求归纳考虑密度、功用、特性和功耗要求。PCIe Gen1 和Gen2以及以太网等标准协议得到了广泛运用。某些商场对协议有特别的要求,例如,播送运用的SDI,以及核算机和存储的SATA/SAS、HyperTransport 和QPI 等。因为许多运用只需求选用支撑专用协议的收发器,因而, 10G 收发器在宽带衔接上敏捷得到了运用,成为许多产品的首要技能推进力气。

要害技能

带有收发器的FPGA 和ASIC 系列产品选用的技能包含工艺技能、支撑可编程功耗技能的功耗和功用优化办法、逻辑架构、I/O、PLL、外部存储器接口、高速串行收发器、时钟数据康复和时钟发生、预加剧和均衡,以及在PCIe 等协议上运用硬核知识产权(IP) 等。

工艺技能和40-nm 的优势和曾经的65-nm 节点以及最近的45-nm 节点比较, 40-nm 工艺有很大的优势。最明显的一点是更高的集成度,半导体生产商能够在更小的管芯中集成更多的功用,生产出密度更高的器材。

40-nm 工艺还进一步进步了功用。40 nm 最小的晶体管逻辑门长度比65 nm 逻辑门长度短38.5%,比45-nm 工艺的逻辑门长度短11%。40 nm 的阻抗进一步下降,然后进步了驱动才能,完成了功用更好的晶体管。应变硅技能使电子和空穴的移动才能进步了30%,晶体管功用进步了近40%。

选用带有收发器的全系列40-nm FPGA 和ASIC 完成立异规划Altera 公司

4

尽管密度和功用的进步十分明显,可是,当今体系开发人员在规划中需求侧重考虑的是功耗问题。40-nm节点在功耗上也有必定的优势,更小的工艺尺度减小了导致动态功耗的杂散电容。特别是,台积电(TSMC)的40-nm 工艺技能要比其45-nm 工艺技能的有功功耗低15%。(2)

可是,工艺尺度的下降却增大了待机功耗。Altera 运用多种办法来下降静态功耗,包含多阈值晶体管、长度不同的晶体管沟道、三重氧化等,而且在对功用要求不高的PLD 上归纳考虑功用和功耗,例如装备逻辑等。

可编程功耗技能和功用

除了常用的电路规划办法, Altera 还引入了65-nm Stratix® III FPGA 的可编程功耗技能(3) 来下降静态功耗。可编程功耗技能使静态功耗下降了70%,在规划中以最低的功耗完成最好的功用。这一立异技能运用了这一现实――在典型规划中,悉数逻辑中只要很少一部分用在要害时序通道上。基准测验标明,时序余度很小的高功用逻辑和时序余度较大的慢速逻辑比平均为30:70。

在任何规划中, Altera 的Quartus® II 开发软件主动确认规划中每一通道的松懈余度。这样,通过调整晶体管的反向偏置电压,将每一逻辑模块、存储器和DSP 模块的晶体管主动设置为适宜的形式――高功用或许低功耗:

■ 在低功耗形式中, Quartus II 软件减小反向偏置电压,使晶体管很难接通。这样,减小了时序不重要电路中的亚阈值走漏电流,以及无用的静态功耗( 图2 中的蓝色部分)。

■ 在高功用形式中, Quartus II 软件增大反向偏置电压,时序要害通路上的晶体管更简单接通,以满意规划中规则的时序束缚要求,完成最佳功用( 图2 中的黄色部分)。

图2. Quartus II 软件下降了功耗,进步了功用

逻辑架构和通用I/O

Altera 的40-nm 器材架构运用了包含自习惯逻辑模块(ALM)、TriMatrix 片内存储器模块和DSP模块的通用内核逻辑体系结构。ALM 含有一个可装备8 输入分段式查找表(LUT)、两个嵌入式加法器和两个寄存器,并选用了MultiTrack 互联结构进行布线,以支撑高速逻辑、算法和寄存器功用,器材运用率十分高。

TriMatrix 片内存储器供给三种不同的存储器模块容量,大大进步了功率和灵敏性,如图3 所示。

Power

High speed

Low power

Threshold voltage

Source

Substrate

Drain

Channel

Gnd

Gate

High Speed Logic Low Power Logic

High-speed logic Low-power logic

Altera 公司 选用带有收发器的全系列40-nm FPGA 和ASIC 完成立异规划

5

图3. TriMatrix 存储器结构

图4 中的DSP 模块是高功用芯片体系结构,其强壮的可编程才能能够在多种运用中完成最佳处理功用。每一模块含有8 个18×18 乘法器,以及寄存器、加法器、减法器、累加器和求和单元,这些都是典型DSP 算法中常用的功用。DSP 模块支撑可变位宽和各种取整饱满形式,有效地满意了运用需求。

图4. DSP 模块体系结构

通用PLLAltera 的通用锁相环(PLL) 包含闭环频率操控体系,该体系依据输入时钟信号和受控振荡器反应时钟信号之间的相位差。图5 显现了PLL 中首要组件的扼要结构。

6

图5. PLL 结构图

这些PLL 的模仿特性使其具有十分低的颤动,能够完成牢靠的时钟计划。许多可装备时钟输出能够十分灵敏的完成体系时钟,为存储器接口和I/O 接口输出时钟。

最佳通用I/O 和外部存储器接口

如图6 所示, I/O 结构的要害构建模块包含:

■ 单端I/O 支撑,供给可编程摆率和驱动才能,可变推迟链补偿电路板走线,以及串行和并行动态片内匹

配(OCT)。

■ 支撑差分片内匹配的高功用LVDS 传输和接纳差分信号

■ 为多通道LVDS 接口供给的硬核动态相位对齐(DPA) 模块,避免了时钟至通道和通道至通道偏移,以及

时钟转发功用,完成软核时钟数据康复(CDR)。

图6. DPA 结构图

Altera 的I/O 引脚支撑已有以及新式的外部存储器标准,例如,DDR、DDR2、DDR3、QDRII、QDRII+ 和RLDRAMII 等。它们包含自校准数据通路,对自己不断进行动态调整,在工艺、电压和温度改动时,供给最牢靠的作业频率。其他电路包含对齐和同步、通道去偏移、读/ 写调平,以及时钟域穿插功用等。

高速串行收发器

Altera的高速收发器模块在物理介质附加(PMA)和物理编码子层(PCS)运用通用体系结构(图7所示)。 依据规划人员的不同要求,能够旁路PCS 中的模块。

Altera 公司 选用带有收发器的全系列40-nm FPGA 和ASIC 完成立异规划

7

图7. PMA 和PCS 结构图

PMA 功用能够用在模仿电路中,包含:

■ CDR

■ SERDES

■ 可编程预加剧和均衡

■ I/O 缓冲,支撑动态可控设置( 输出差分电压和差分OCT)。

PCS 供给数字功用以习惯背板、芯片至芯片和芯片至模块运用的多种要害协议。这些数字模块为增强对协议的支撑而进行了优化,削减了完成物理层协议所需求的器材资源,一起下降了功耗。与特定的IP 和参阅规划相结合,这些模块能够供给完好的协议处理计划,缩短了规划周期,下降了危险。PCS 功用的比如包含8b/10b 编码器/ 解码器、相位补偿FIFO 缓冲、字对齐器和速率匹配器,在收发器模块中供给对协议的支撑。

此外,还供给专用状态机,支撑PCIe、GbE 和XAUI 协议。

时钟数据康复

如图8 所示, Altera 的高速CDR 电路运用混合体系结构,支撑两种作业形式,进一步开展了传统的数据驱动体系结构。能够主动或许手动设置这两种形式――确认至数据和确认至参阅。选用参阅时钟作为输入,将CDR 单元中的模仿PLL 确认到需求的频率上。然后,电路从参阅时钟输入切换到数据信号, CDR 和数据信号完成相位确认,然后康复数据中的时钟。这种体系结构的要害优势在于缩短了确认时刻,下降了功耗,能够接受较大的颤动。成果, Altera 的收发器在驱动背板时,具有最低的颤动和最好的BER 功用,BER 到达10EC12 以上,而且协议兼容性十分好。

8

图8. CDR 体系结构

时钟发生和PLL 技能

时钟发生是高速收发器的一项重要功用。时钟颤动会影响发射器和接纳器的功用,然后影响高速链路的BER 功用。PLL 的要害组成是振荡器,它是颤动的首要来历。抱负情况下,高速压控振荡器(VCO) 供给较宽的调谐规模,较高的频率(GHz),较低的噪声和功耗,体积很小,集成度较高。

Altera 的高速收发器支撑两类振荡器,环行振荡器(RO) 和LC谐振振荡器(LC谐振腔)。RO的集成度较高,功耗也比较低,管芯面积较小,在较宽的调谐规模内都具有优异的颤动功用,每一接纳通道都有独立的RO,作业规模在600 Mbps 至10.3 Gbps。可是,跟着频率的进步,相位噪声和颤动功用呈现劣化,当高频时需求优异的相位噪声和颤动功用时, LC 谐振振荡器则显现出很大的优势。LC 谐振振荡器的缺陷是其电感和可变电容( 变容),这些都是体积较大的元件。

■ 发送通道RO

● 在较宽的频率规模内具有优异的颤动功用

● 600 Mbps 至10.3 Gbps 的数据作业规模

■ 发送通道LC 谐振振荡器

● 技能完成了较好的颤动功用,较窄的作业规模。

● 4.9C6.375 Gbps LC 谐振振荡器,适用于PCIe/CEI-6。

● 9.9C11.3 Gbps LC 谐振振荡器 ,适用于XLAUI/CAUI/CEI-11G。

预加剧和均衡

一切传输介质普遍存在的一个问题是由频率引起的损耗,特别是趋肤效应和电介质损耗导致的印刷电路板(PCB) 规划损耗。这种损耗导致高频重量的衰减更大,然后下降了远端信号的接纳才能,缩短了驱动长度,增大了BER。预加剧和均衡用在Altera 的高速收发器中,以战胜传输损耗,驱动带有两个衔接器的40

FR-4 背板。

在数据信号发送至通道之前,高速收发器的发射器选用预加剧技能扩大数据信号的高频重量。因为所生成数据信号的前面和后续数据位在发射器中是确认的,因而,预加剧办法运用在相关于主脉冲的不同数据位上。Altera 的预加剧计划运用预抽头,这以后是主脉冲和两个后抽头。

在接纳器开端进行均衡,当数据进入接纳器时,均衡起到了高通滤波器的功用,成功地重建信号。Altera的高速收发器支撑各种均衡计划(4):

Altera 公司 选用带有收发器的全系列40-nm FPGA 和ASIC 完成立异规划

9

■ 接连时刻线性均衡(CTLE)

■ 自习惯散射补偿引擎(ADCE)(5)

■ 断定反应均衡(DFE)

因为不同的数据速率和背板特性,因而,很难从数千种设置中挑选最佳均衡设置。运用收发器HSPICE 模型和背板S 参数特性进行仿真能够简化这一进程。可是,某些运用在作业中需求插拔体系卡,当条件改动时,不得不敏捷更新均衡设置。运用即插即用信号完好性功用, Altera 引入了ADCE,热插拔收发器支撑在40 FR-4 背板上2.5 Gbps 至6.5 Gbps 的数据传输。

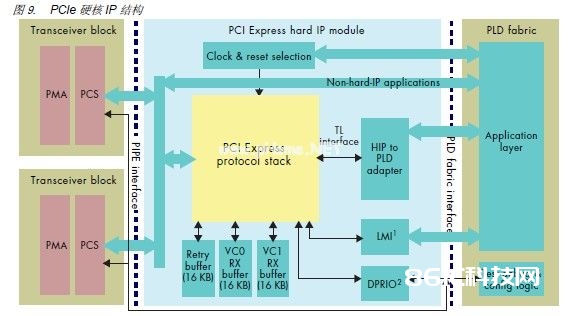

面向PCI Express 的硬核IP

PCIe 的广泛运用推进了集成PCIe 功用的开展,在实践中它作为预验证和契合标准的硬核IP 模块来完成。

PCIe 的重要优势是能够大大节约资源( 最大40K LE),下降功耗,其编译时刻更短,然后缩短了规划周期。

如图9 所示,硬核IP 模块嵌入在PCIe 协议栈的一切层中,包含收发器模块、物理层、数据链路层和协议层。PCIe 硬核IP 模块契合以下PCI-SIG 标准:

■ PCIe 根本标准, Rev 1.1 (2.5 Gbps)

■ PCIe 根本标准, Rev 2.0 (2.5 和5.0 Gbps)

图9. PCIe 硬核IP 结构

注释:

(1) LMI:本地办理接口

(2) DPRIO:动态部分可从头装备输入/ 输出

Altera 的收发器系列器材

新器材的开展契合摩尔定律――密度每两年加倍,开发新器材需求不同的办法,因为开发本钱随之添加,应尽量选用相关的技能。在开发全系列收发器FPGA 和ASIC 时, Altera 选用了以下办法:

■ 从头运用已有工艺所选用的技能

■ 通过技能进步,发挥每一新工艺节点的优势来逐渐改善。

10

■ 运用通用体系结构,归纳考虑不同的功用、功耗和本钱要求,优化构建模块。

■ 进行革命性的立异,以满意从头运用已有技能所不能处理的需求。

系列产品组成

依据TSMC 的40-nm 工艺, Altera 选用了相同的老练收发器体系结构来开发每一带有收发器的FPGA 和ASIC,这种结构十分合适宽带串行接口运用。在每个器材中,集成收发器模块针对方针运用进行了优化。

Arria II GX FPGA

Arria® II GX FPGA 满意了对本钱和功耗灵敏的运用,在低密度和中密度规模内供给丰厚的特性。最大收发器数据速率是3.75 Gbps,满意了GPON、IP DSLAM、长途射频前端、播送和桥接等中等功用运用范畴对高速协议和宽带的需求。收发器和I/O 通过优化,归纳考虑特性和功用,具有较高的性价比。尽管Arria IIGX FPGA 的固定功耗形式不具有可编程功耗技能的灵敏性,可是,它大大下降了静态功耗。Arria II GXFPGA 选用可编程预加剧和均衡技能,合适背板运用,而且具有优异的信号完好性。因为只要速率较高的背板运用才需求ADCE 和DFE 等功用,为下降本钱和功耗,该器材不支撑这类功用。

Stratix IV GX FPGA

Stratix IV GX FPGA 供给最大的密度,最好的功用以及最低的功耗,收发器速率高达8.5 Gbps, 48 个收发器进步了带宽,其丰厚的功用可支撑背板运用和高速协议。要害运用包含对功用要求较高的无线基站、40G/100G 运用、高端路由器和桥接运用。其优异的信号完好性确保了与PCIe Gen2 和CEI-6 等严厉协议的兼容性。可编程功耗技能进步了规划中要害时序通路的功用,一起优化了功用较低部分的功耗。

HardCopy IV GX ASIC

HardCopy® IV GX ASIC 满意了对本钱和功耗灵敏的大批量运用需求。其功用与用作原型开发器材的StratixIV GX FPGA 适当。这种共同的规划办法依据选用了Quartus II 开发软件的共同工具包, 完成了危险最低的ASIC,而且集成了6.5-Gbps 收发器。

Stratix IV GT FPGA

Stratix IV GX FPGA 满意了40G/100G 运用需求,是需求10G 收发器功用的最佳处理计划。Stratix IV GTFPGA 具有Stratix IV GX FPGA 的密度、特性和功用优势,一起集成了11.3-Gbps 收发器。这样,能够完成MAC/ 成帧器、数据包处理和流量办理功用的最佳体系集成,而且具有可编程架构的产品及时面市优势。需求很大带宽的桥接运用也能够获益于这些器材。Stratix IV GT 器材能够直接衔接至光模块,然后总体上完成了最低的体系本钱和体系功用,大大下降了电路板杂乱度。

通用IP 系列产品和开发环境

一切Altera 定制逻辑器材都具有效能优势,包含共同全面的规划软件,一组通用IP 内核,并供给各种参阅规划和规划实例。

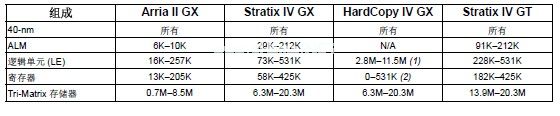

系列产品标准

本节比照收发器系列产品的要害标准技能标准,表2 杰出介绍了通用体系结构组成。一切器材均支撑悉数

专用组成功用。

表2. Altera 器材的体系结构组成 11

11

注释:

(1) 每LE 的ASIC 逻辑门数量以12 个进行核算;每个18×18 乘法器5000 个逻辑门。

(2) 选用HCell 进行构建。

(3) 全双工对,包含接纳和发送。

表3 在功耗和功用上比照了系列器材。

注释:

(1) 低功耗(LP)/ 高功用(HP)

(2) 支撑-2 内核和-3 I/O 速率等级。支撑PCIe Gen1 和Gen2 x8。

(3) 不决的特性

M144K 0 16C64 16C64 22C64

M9K 87C950 462C1,280 462C1,280 936C1,280

MLAB 存储器0.2MC3.2M 0.8MC6.5M 0C1.625M (2) 2.8MC6.4M

DSP 模块56C736 384C1288 0C1,288 (2) 832C1,288

模仿PLL 4C6 3C12 2C8 8C12

I/O 150C610 368C904 368C736 636C754

真LVDS (3) 32C144 28C98 28C88 44

仿真LVDS TBD 128C256 128C256 192C256

收发器4C16 8C48 8C36 36C48

抗SEU 是是是是

规划安全性是是硬线衔接是

表3. Altera 器材功耗和功用

功耗和功用Arria II GX Stratix IV GX HardCopy IV GX Stratix IV GT

可编程功耗技能(1) 仅LP LP/HP 不需求LP/HP

功用

速率等级-4, -5, -6 -2/-2x (2), -3, -4 N/A -1, -2, -3

时钟500 MHz 600 MHz 600 MHz 600 MHz

DSP 350 MHz 550 MHz 495 MHz 550 MHz

内部存储器390 MHz 550 MHz 500 MHz 550 MHz

LVDS

I/O 1 Gbps 1.6 Gbps 1.25 Gbps 1.6 Gbps

DPA 是是是是

存储器

DDR 200 MHz 200 MHz 200 MHz 200 MHz

DDR2 300 MHz 400 MHz 400 MHz 400 MHz

DDR3 300 MHz 533 MHz 533 MHz (3) 533 MHz

QDRII 250 MHz 350 MHz 350 MHz 350 MHz

QDRII+ TBD 350 MHz 350 MHz 350 MHz

RLDRAMII TBD 400 MHz 400 MHz 400 MHz

表2. Altera 器材的体系结构组成

组成Arria II GX Stratix IV GX HardCopy IV GX Stratix IV GT

选用带有收发器的全系列40-nm FPGA 和ASIC 完成立异规划Altera 公司

12

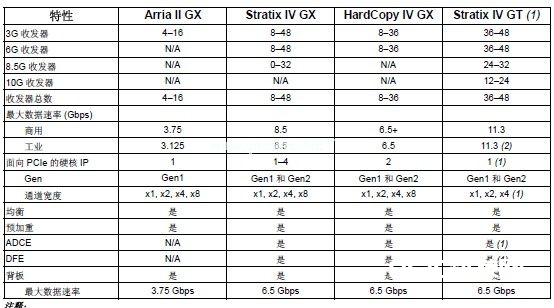

表4 首要介绍了高速收发器特性和功用。

注释:

(1) 开始数据,有可能会改动。

(2) 0°C – 100°C

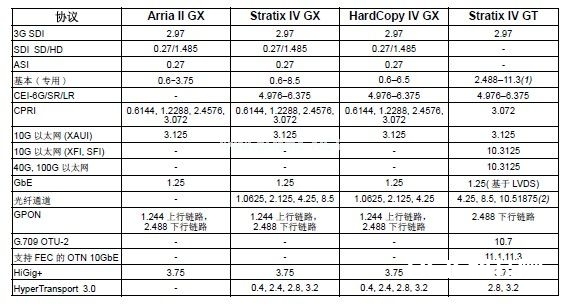

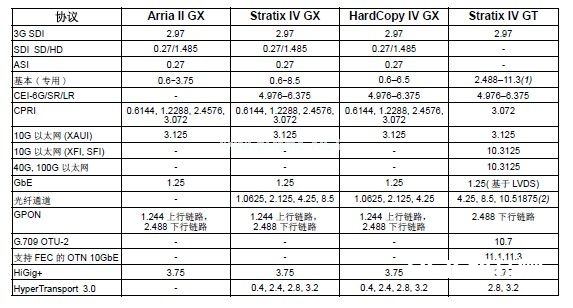

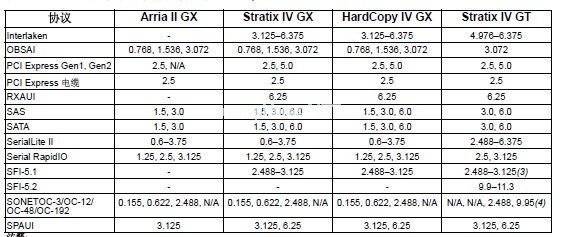

表5 列出了每一产品系列支撑的协议和数据速率。

表4. Altera 的高速收发器特性和功用

特性Arria II GX Stratix IV GX HardCopy IV GX Stratix IV GT (1)

3G 收发器4C16 8C48 8C36 36C48

6G 收发器N/A 8C48 8C36 36C48

8.5G 收发器N/A 0C32 N/A 24C32

10G 收发器N/A N/A N/A 12C24

收发器总数4C16 8C48 8C36 36C48

最大数据速率(Gbps)

商用3.75 8.5 6.5+ 11.3

工业3.125 6.5 6.5 11.3 (2)

面向PCIe 的硬核IP 1 1C4 2 1 (1)

Gen Gen1 Gen1 和Gen2 Gen1 和Gen2 Gen1 和Gen2

通道宽度x1, x2, x4, x8 x1, x2, x4, x8 x1, x2, x4, x8 x1, x2, x4 (1)

均衡是是是是

预加剧是是是是

ADCE N/A 是是是(1)

DFE N/A 是是是(1)

背板是是是是

最大数据速率3.75 Gbps 6.5 Gbps 6.5 Gbps 6.5 Gbps

表5. Altera 的高速协议和数据速率( 每通道Gbps)

协议Arria II GX Stratix IV GX HardCopy IV GX Stratix IV GT

3G SDI 2.97 2.97 2.97 2.97

SDI SD/HD 0.27/1.485 0.27/1.485 0.27/1.485 –

ASI 0.27 0.27 0.27 –

根本( 专用) 0.6-3.75 0.6-8.5 0.6C6.5 2.488C11.3(1)

CEI-6G/SR/LR – 4.976C6.375 4.976C6.375 4.976C6.375

CPRI 0.6144, 1.2288, 2.4576,

3.072

0.6144, 1.2288, 2.4576,

3.072

0.6144, 1.2288, 2.4576,

3.072

3.072

10G 以太网(XAUI) 3.125 3.125 3.125 3.125

10G 以太网(XFI, SFI) – – – 10.3125

40G,100G 以太网- – – 10.3125

GbE 1.25 1.25 1.25 1.25( 依据LVDS)

光纤通道- 1.0625, 2.125, 4.25, 8.5 1.0625, 2.125, 4.25 4.25, 8.5, 10.51875(2)

GPON 1.244 上行链路,

2.488 下行链路

1.244 上行链路,

2.488 下行链路

1.244 上行链路,

2.488 下行链路

2.488 下行链路

G.709 OTU-2 – – – 10.7

支撑FEC 的OTN 10GbE – – – 11.1,11.3

HiGig+ 3.75 3.75 3.75 3.75

HyperTransport 3.0 – 0.4, 2.4, 2.8, 3.2 0.4, 2.4, 2.8, 3.2 2.8, 3.2

Altera 公司 选用带有收发器的全系列40-nm FPGA 和ASIC 完成立异规划

13

注释:

(1) 10G 根本( 专用)

(2) 10G 光纤通道

(3) 包含SFI-4.2 和SFI-5.1

(4) 10G SONET/SDH OC-192/STM-64

定论

进步带宽和数据速率需求更多、更快的收发器。各种标准、优异的背板信号完好性和协议要求推进了数字器材的收发器立异开展。为满意不同商场和运用的各类需求,数字器材有必要在密度和特性上到达最佳组合,一起满意功用、功耗和本钱方针。Altera 的40-nm 收发器FPGA 和ASIC 技能立异以及从头运用已有技能满意了这些需求,供给了最全面的收发器定制逻辑系列产品。

选用了相同的老练收发器体系结构来开发Altera 一切的40-nm 收发器FPGA 和ASIC,这种体系结构合适宽带串行接口运用。在每一器材中,针对方针运用优化了集成收发器模块。Arria II GX FPGA 是低功耗、高性价比FPGA 系列,大大简化了3.75-Gbps 收发器处理计划的完成。Stratix IV GX FPGA 是高功用器材,具有530K LE 和高档收发器,供给较大的存储器带宽。Stratix IV GT FPGA 是仅有集成了11.3-Gbps 收发器的FPGA,合适40G 和100G 运用。HardCopy IV GX ASIC 是封装和引脚与Stratix IV GX FPGA 相匹配的ASIC,有助于下降带有嵌入式收发器ASIC 规划的危险和总本钱。此外,一切Altera 的定制逻辑器材都具有效能优势,包含共同全面的规划软件,一组通用知识产权(IP) 内核,并供给各种参阅规划和规划实例。

表5. Altera 的高速协议和数据速率( 每通道Gbps)

协议Arria II GX Stratix IV GX HardCopy IV GX Stratix IV GT

14

版权 2009 Altera 公司。保存一切版权。Altera、可编程处理计划公司、程式化Altera 标识、专用器材称号和一切其他专有商标或许服务符号,除非特别声明,均为Altera 公司在美国和其他国家的商标和服务符号。一切其他产品或许服务称号的一切权归于其各自持有人。Altera 产品受美国和其他国家多种专利、未决运用、掩模著作权和版权的维护。Altera 确保当时标准下的半导体产品功用与Altera 标准质保共同,可是保存对产品和服务在没有事前告诉时的改变权力。除非与Altera 公司的书面条款完全共同,不然Altera 不承当由运用或许运用此处所述信息、产品或许服务导致的职责。Altera 主张客户在决议购买产品或许服务,以及坚信任何揭露信息之前,阅览Altera 最新版的器材标准阐明。

101 Innovation Drive

San Jose, CA 95134

具体信息

称谢

■ Bernhard Friebe,产品营销司理, Altera 公司。

■ Rishi Chugh,产品营销司理,低本钱FPGA, Altera 公司。

■ Kevin Cackovic,战略营销高档司理,通讯业务部, Altera 公司。

■ Martin Lee,战略营销高档司理,通讯业务部, Altera 公司。

■ Martin Won,技能组资深成员,产品营销, Altera 公司。

■ Mike Peng Li,博士,首席规划师/ 高档工程师,产品工程, Altera 公司。

■ Sergey Shumarayev,工程主管,模仿规划组, Altera 公司。