跟着电子技术的飞速发展, 存储器的品种日益繁复,每一种存储器都有其独有的操作时序,为了进步存储器芯片的测验功率,一种多功用存储器芯片的测验体系应运而生。本文提出了一种多功用存储器芯片的测验体系硬件规划与完结,对各种数据位宽的多种存储器芯片(SRAM、MRAM、NOR FALSH、NAND FLASH、EEPROM等)进行了详细的结口电路规划(怎么挂载到NIOSII的总线上),终究处理了不同数据位宽的多种存储器的同渠道测验处理计划,并详细地规划了各结口的硬件完结办法。

导言

跟着电子技术的飞速发展,存储器类芯片的品种越来越多,其操作方法彻底不相同,因而要测验其间一类存储器类芯片就会有一种专用的存储器芯片测验仪。本文规划的多种存储器芯片测验体系是能够对SRAM、Nand FLASH、Nor FLASH、MRAM、EEPROM等多种存储器芯片进行功用测验,并且每一类又可兼容8位、16位、32位、40位等不同宽度的数据总线,假如针对每一种产品都单独规划一个测验渠道,其测验操作的杂乱程度是可想而知的。为到达简化测验过程、减小测验的杂乱度、进步测验功率、下降测验本钱,特规划一种多功用的存储器类芯片测验体系,完结在同一渠道下完结一切上述存储器芯片的方便快捷地测验。

规划原理

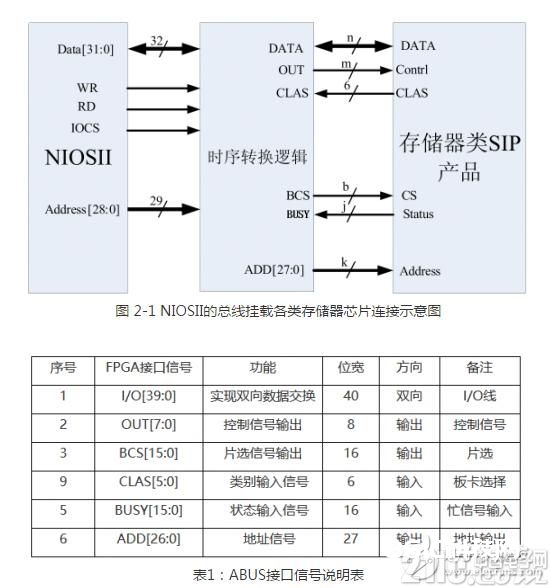

此规划计划依据上述各种存储器单独的读写时序拜访特性,经过FPGA的灵敏编程特性,适当地调整NIOSII的外部总线时序,终究完结依据NIOSII的外部总线拜访各种存储器读写时序的精确操作。如图2-1。经过FPGA自定义一个能够挂载一切存储器芯片的总线接口-ABUS,如表1。并且在同一个接口上能够自动辨认各种接入的被测验存储器芯片,它们经过类别输入信号(CLAS)来区别,每一种存储器芯片对应一种共同的操作时序。下面是几种存储器芯片的接口衔接方法及信号描绘。其它的存储器芯片都能够用相似的接法挂载到ABUS总线上,终究完结测验。

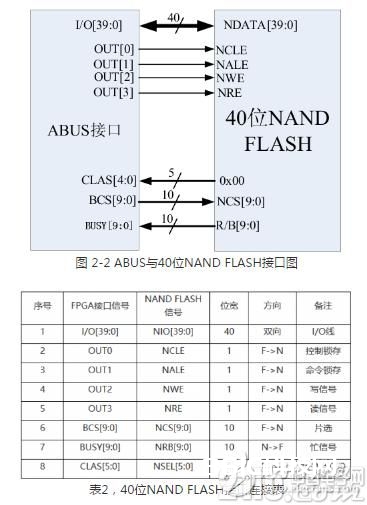

40位NAND FLASH衔接规划

如图2-2所示,40位NAND FLASH与NIOSII 经过ABUS(FPGA)桥接,把外部总线的时序彻底转化成NAND FLASH的操作时序。40位NAND FLASH芯片品由五个独立的8位NAND FLASH芯片拼接构成。5个8位器材的外部IO口拼接成40位的外部IO口,而各自的操控线(NCLE,NALE,NRE,NWE)衔接在一起构成一组操控线(NCLE,NALE,NRE,NWE),片选彼此独立引出成NCS0-NCS9,忙信号独立引出为R/B0-R/B9。

如表2,胪陈了40位NAND FLASH与ABUS的衔接联系。

40位SRAM与NIOSII衔接

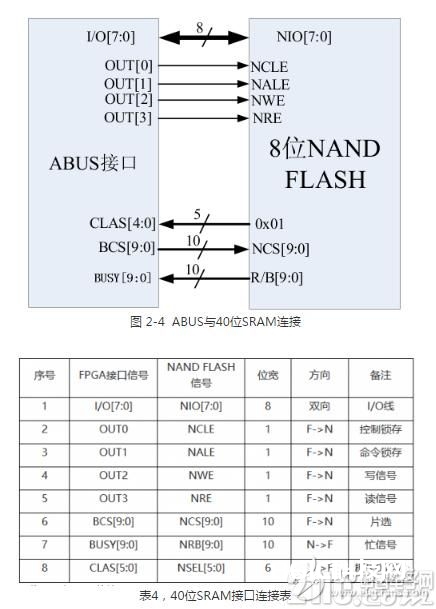

40位SRM模块与NIOSII经过ABUS衔接,完结正确的时序读写操作。测验时,一次只测验8位,分5次完结一切空间的测验。如图2-4。表4是详细的信号衔接阐明。

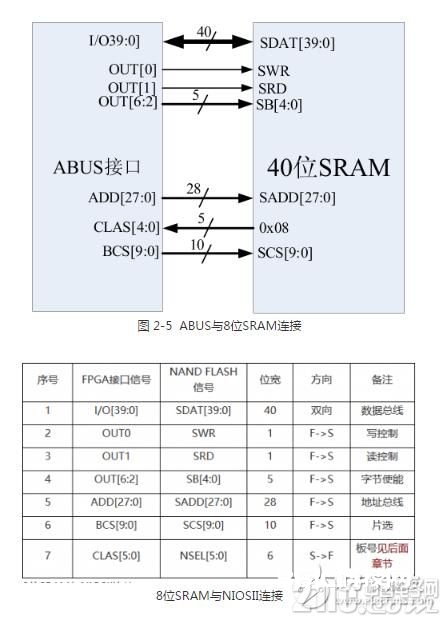

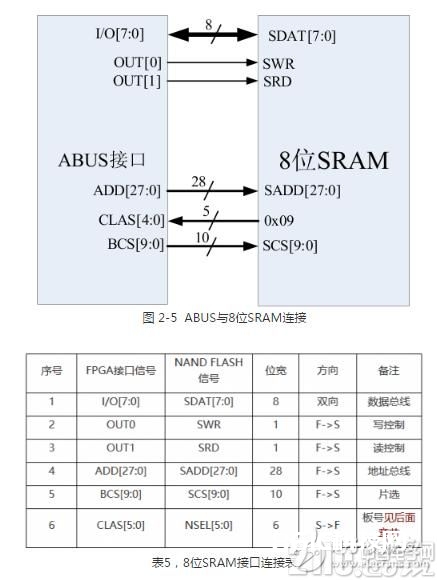

8位SRAM与NIOSII衔接

8位SRM模块与NIOSII经过ABUS(FPGA)衔接,完结正确的时序读写操作。如图2-5。表5是信号衔接阐明。

8位SRM模块与NIOSII经过ABUS(FPGA)衔接,完结正确的时序读写操作。如图2-5。表5是信号衔接阐明。

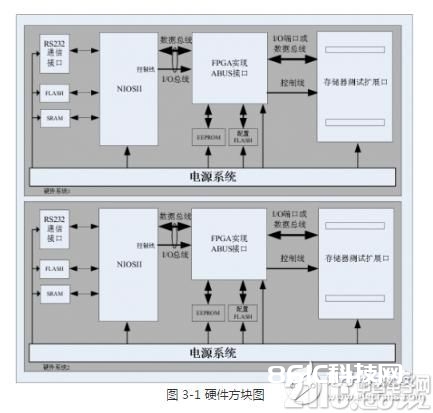

硬件电路规划

在测验NAND FLASH时,测验时刻长达十个小时不等。在此为进步测验功率,添加测验速度,本规划选用两套彻底相同且独立的硬件体系构成。可一起最多测验2片NAND FLASH器材。每一个硬件体系由一个微处理器(NIOSII)加一个大容量FPGA及一个存储器测验扩展接口(即ABUS接口)三大模块构成。如图3-1。RS232通讯接口完结测验体系与上位机的数据交换,完结人机交互操作。电源体系发生各种适宜的电压,满意各芯片的电源供应。

处理器模块电路

处理器模块电路由FPGA内嵌的NIOSII软核(CPU)、两路RS232通讯、一个FLASH芯和一个SRAM芯片组成。CPU是整个体系的中心管理者,向下担任各种存储器芯片的读写测验,向上担任与上位机通讯,完结人机交互。通讯由其间一个RS232电路完结,另一个RS232电路用来完结体系调试和软件固化。FLASH芯片用来存储程序代码及重要的数据。而SRAM芯片在CPU上电作业今后,经过CPU加载FLASH的程序,终究给CPU的程序代码供给快速的运转环境。

依据FPGA的ABUS接口模块

ABUS接口模块由FPGA芯片、装备FLASH及数据存储EEPROM芯片构成。ABUS要完结NIOSII的外部总线与多种存储器模块的接口对接,每一种特定的存储器有一个特定的时序逻辑,而每一种时序逻辑能够经过FPGA的硬件代码(IP核)来完结,详细的每一个存储器模块在测验时会给ABUS接口一个固定的类别信号CLAS,ABUS接口依据这个类别信号辨认出各种SIP存储器模块,终究切换出正确的对应特定产品的时序逻辑,来完结NIOSII经过外部总线来对存储器芯片的读写测验。而装备FLASH完结FPGA在上电时硬件程序的加载作业及掉电数据维护。EEPROM用来存储一些重要的体系参数。

SIP存储器测验扩展接口

存储器测验扩展接口在硬件上由两排双排座构成。一共是120个管脚。ABUS接口与测验扩展接口相衔接:40个管脚与双向的数据或I/O线相连、8个管脚与8根信号输入操控线相连、16个管脚与16根片选信号输出线相连、5个管脚与5根类别输入信号相连、16个管脚与16根状况输入信号线相连、27个管脚与27根地址线相连。其它的管脚可分配成电源和地线,以及信号指示等。

ABUS接口IP核的规划

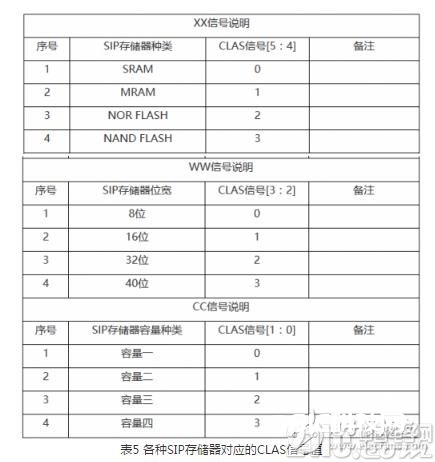

每一种SIP存储器对应于一个特定的ABUS接口IP核,以完结正确的时序读写操作。这个IP核有一个共同的接口约好,都是由两个固定的接口构成,其间与NIOSII衔接的是外部总线接口,其操作依照NIOSII的外部总线时序标准来完结,另一个接口便是上文提及的ABUS接口,在相应的CLAS信号有用的情况下,它担任把NIOSII的外部总线读写时序转化成对应存储器芯片的时序。IP核的作业便是完结这些读写操作的转化。表5是各种SIP存储器对应的类别信(CLAS)号输入值,在规划接口转接板时要按这个值设定,ABUS才会切换出正确的读写时序。

七位类别示别信号意义:T_XX_WW_CC,T为1表明凹凸测验测验,为0表明常温下的功用测验。XX表明存储器品种,WW表明总线宽度,CC表明容量品种。

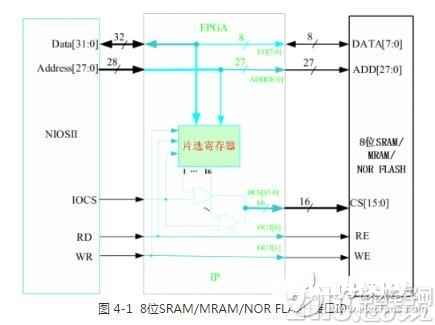

8位SRAM/MRAM/NOR FLASH接口IP核规划

如图4-1,SRAM、MRAM和NOR FLASH的接口操作根本共同,NIOSII的总线时序彻底满意。故在FPGA内部只需简略地把相应的操控线和数据线相连就能够了,唯一只需规划一个片选寄存器,用来区别存储器芯片的16个片选。每一个片选能够拜访的空间为128MByte。片选寄存器的地址为(基址+0x0FFFFFFC),基地址设在NIOSII外部总线的最高地址位。

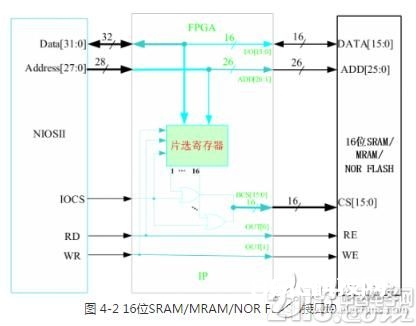

16位SRAM/MRAM/NOR FLASH接口IP核规划

如图4-2,SRAM、MRAM和NOR FLASH的接口操作根本共同,NIOSII的总线时序彻底满意。故在FPGA内部只需简略的把相应的操控线和数据线相连就能够了,唯一只需规划一个片选寄存器,用来区别SIP的16个片选。每一个片选能够拜访的空间为128MByte。片选寄存器的地址为(基址+0x0FFFFFFC),基地址设在NIOSII 外部总线的最高地址位。

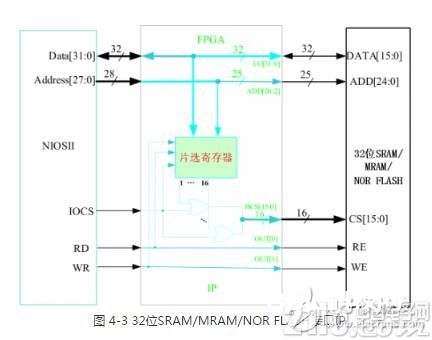

32位SRAM/MRAM/NOR FLASH接口IP核规划

如图4-3,SRAM、MRAM和NOR FLASH的接口操作根本共同,NIOSII的总线时序彻底满意。故在FPGA内部只需简略的把相应的操控线和数据线相连就能够了,唯一只需规划一个片选寄存器,用来区别SIP的16个片选。每一个片选能够拜访的空间为128MByte。片选寄存器的地址为(基址+0x0FFFFFFC),基地睛设在NIOSII 外部总线的最高地址位。

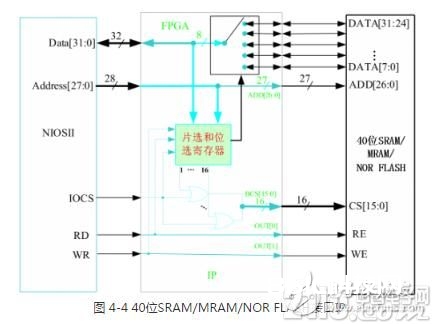

40位SRAM/MRAM/NOR FLASH接口IP核规划

如图4-4,40位的数据宽度有点特别。在此咱们把40位的数据分红5个8位的区域,用8位宽度的总线去别离拜访每一个区域。IP核中的位选寄存器便是用来完结切换8位数据总线到40位总线的5个区域的其间一个。片选寄存器的地址为(基址+0x0FFFFFFC),位选寄存器的地址为(基址+0x0FFFFFF8)。最大能够测验128MTImes;40位TImes;16片的存储器SRAM/MRAM/NOR FLASH模块。

8位NAND FLASH的ABUS接口IP规划

如图4-5,经过写片选寄存器来选中模块的16个片选的其间一个。咱们约好其地址为(基址+0x0FFFFFFC)。读状况寄存器回来的是16个NAND FLASH芯片的忙信号,其地址为(基址+0x0FFFFFF8)。向地址(基址+0x00)写入数据便是对NAND FLASH数据寄存器的写操作。向地址(基址+0x00)单元读数据便是对NAND FLASH数据寄存器的读操作。向地址(基址+0x01)写入数据便是对NAND FLASH指令寄存器的写操作。向地址(基址+0x02)写入数据便是对NAND FLASH地址寄存器的写操作。

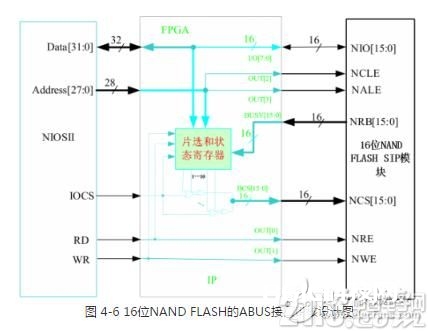

16位NAND FLASH的ABUS接口IP规划

16位的NAND FLASH存储器芯片能够有多种组合方法,能够用多个16位的NAND FLASH组合,也能够用多个8位的NAND FLASH组合。这儿咱们假定16位的SIP NAND FLASH产品是由多个16位的NAND FLASH组合而成,下面的IP核是依据它的结构来规划的。

如图4-6,经过写片选寄存器来选中模块的16个片选的其间一个。咱们约好其地址为(基址+0x0FFFFFFC)。读状况寄存器回来的是16个NAND FLASH芯片的忙信号,其地址为(基址+0x0FFFFFF8)。向地址(基址+0x00)写入数据便是对NAND FLASH数据寄存器的写操作。向地址(基址+0x00)单元读数据便是对NAND FLASH数据寄存器的读操作。向地址(基址+0x01)写入数据便是对NAND FLASH指令寄存器的写操作。向地址(基址+0x02)写入数据便是对NAND FLASH地址寄存器的写操作。

验证与总结

将写好的FPGA程序和调试的C代码写入FLASH后,掉电重装备FPGA,串口的输出能正常辨认一切设置好的存储器芯片,并能够进行精确地读写功用测验。到达了规划意图。

本文介绍了一种低本钱、简略、灵敏的多种存储器芯片测验体系的硬件规划,并选用FPGA、FLASH、SDRAM、RS232电路等完结。选用这种计划,用户可依据市场需求,灵敏的添加测验体系功用,完结更多的存储器芯片测验。