现如今处理器到摄像机传感器(processor-to-camera sensor)间的接口带宽,在更高分辨率图画,更深色彩深度和更快的帧率推进下,现已抵达了它们的极限。但关于规划人员来说,简略的添加带宽并不能满意跨越多代产品的功能方针的。

移动工业需求一个标准的,强壮的,可扩展的,低功耗,且支撑移动设备的多种成像处理方案的摄像机接口。

MIPI联盟(MIPI Alliance)摄像机工作组(Camera Working Group)现已发明晰一个清晰的规划路线图,它不但能够灵敏的处理今日的带宽应战,而且能够应对工业化大规模出产超越每年10亿部手机关于广泛用户,运用,本钱点的“特征和功能性”应战。

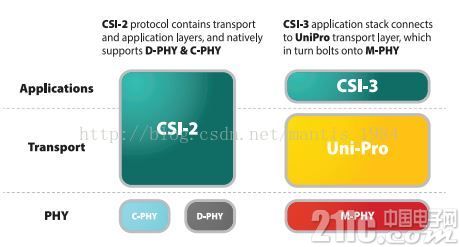

MIPI CSI-2 和 MIPI CSI-3 是MIPI 摄像机接口开始标准的晋级版别,这两个版别都在持续演进中。两个版别都具有高档的架构规划,为开发人员,制作商和终究的顾客供给更多挑选和更大的价值,一起坚持标准接口的优势。

技能概要

相关于之前的版别,最新的摄像机串行接口2标准(CSI-2 v1.3)供给了更高的接口带宽和更好的通道布局灵敏性。它引入了C-PHY 1.0(C-PHY 1.0是MIPI联盟于2014年9月发布的新物理接口),能够兼容之前的D-PHY v1.2版别。

C-PHY 和D-PHY都挑选的改进了差错容忍度和供给了更高的数据速率。两中接口都是串行接口,它们处理了并行的接口的许多问题,比方降低了接口功耗,改进了并行难以扩展的问题。

运用D-PHY坚持的对之前版别标准的兼容性,而且出产厂商能够持续运用当时的制作设备出产新的芯片。C-PHY运用最少3针来替代4针,以满意关于D-PHY的后向管脚兼容性。规划师能够完成独立的C-PHY,D-PHY或组合C / D-PHY选项保证长时间规划的可行性。

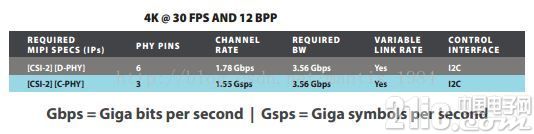

CSI-2 协议包括传输层和运用层,而且原生支撑C-PHY, D-PHY 或许组合C/D-PHY。关于物理层挑选摄像机操控(camera control interface)接口是双向的,兼容I2C标准。CSI-2标准在摄像机(作为一个外围设备)和主处理器(一般是一个基带运用引擎)之间界说了标准的数据传输和操控接口。下面的表格展现了关于当时盛行的4K图画格式的MIPI CSI 和PHY的最佳装备。

CSI-2在D-PHY和C-PHY的运用

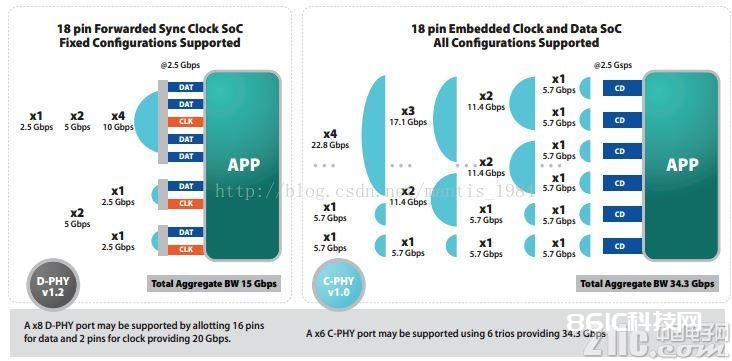

D-PHY在CSI-2运用时作为一个单向的差分接口,由2条前向时钟线和一个或许多于2个的数据线组成。D-PHY的晋级版别v1.2,在接纳端引入了根据通道的(lane-based)数据误差操控机制,使得单通道(lane)传输速率到达2.5Gbps(2.5Gbps/lane),4通道(4 lanes)传输超越10Gbps,比照v1.1峰值速率1.5Gbps/lane或6Gbps/4 lanes,v1.2现已明显提高了传输速率。

C-PHY由1个或多个单向3线(3-wire)串行数据通道组成,可称为为“trios”,每个“trios”都有自己独立的嵌入式时钟。C-PHY的物理层接口由MIPI联联盟C-PHY标准界说的。MIPI C-PHY 选用3相位(3-phase)符号编码,每个相位符号约由2.28bit表明,一个“trio”(3-wire)可到达2.5Gsps(2.5G符号每秒),相当于5.7Gbps/lane。在v1.0版别C-PHY中,三个“trios”(9-wire)能够到达2.5Gsps的符号速率,相当于供给17.1Gbps比特率,如有需求这9-wire也能够与MIPI D-PHY接口进行同享。

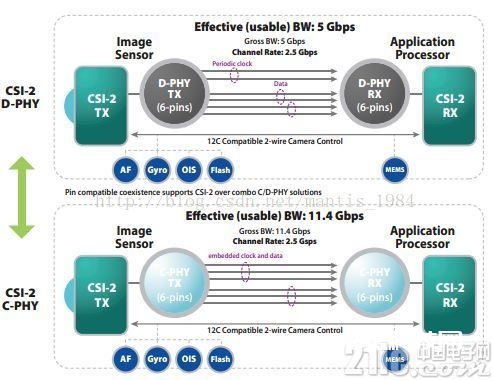

根据C/D-PHY的CSI-2图画接口没有约束每个衔接的lanes数量。C/D-PHY的传输速率与lane的数量成线性比例关系。下面的图表展现了运用6-pin C/D-PHY衔接图画传感器和运用处理器之间的CSI-2接口的衔接办法,这个办法是移动渠道的典型用法。

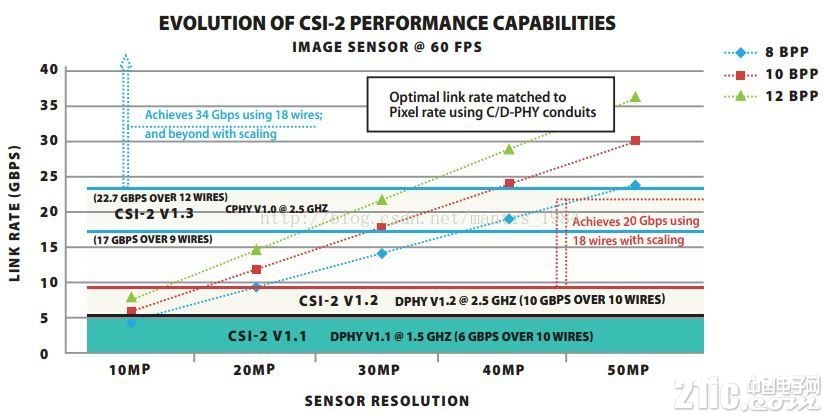

下面的图片图片展现了CSI-2功能演进状况。

下图说明晰CSI-2逻辑端口装备嵌入式时钟和数据的优点。很多的图画运用状况都能够在多通道装备中找到一种映射,也就是说能够满意绝大多数的图画运用需求。在CSI-2渠道上,嵌入式的时钟和数据(CD)通道供给了可装备的逻辑端口完成办法。