5.6 大规模规划的调试经历

在大规模规划的调试应该依照和规划理念相反的次序,从底层测验,首要依托ChipScope Pro 东西。下面首要介绍ChipScope Pro、FPGA Editor 组件的使用方法。

5.6.1 ChipScope Pro组件使用实例

在赛灵思软件规划东西中,ISE 可集成赛灵思公司的一切东西和程序。ChipScope Pro 也不破例,在ISE 中将其作为一类源文件,和HDL 源文件、IP Core 以及嵌入式体系的方位是同等的。本节在Xilinx Spartan3E-D开发板上完结一个计数器模块,依据该模块具体介绍如安在ISE 中新建ChipScope 使用以及调查、剖析数据的具体操作。

例5.6.1 :在ISE 中完结一个8 比特计数器,使用ChipScope 剖析其逻辑输出。

(1) 新建用户工程,增加mycounter.v 的源文件,其内容如下所列:

module mycounter(clk, reset, dout);

input clk;

input reset;

output [7:0] dout;

reg [7:0] dout;

always @(posedge clk) begin

if (reset == 0)

dout = 0;

else

dout = dout + 1;

end

endmodule

然后依据电路衔接,增加相应的管脚束缚。

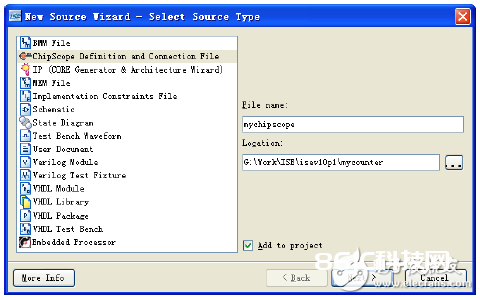

(2) 归纳工程,然后在ISE 工程管理区,单击右键,挑选“Add New Source”指令,在弹出的对话框中挑选“ChipScope DefiniTIon and ConnecTIon File” 类型, 并在“File Name” 栏输入ChipScope 规划称号mychipscope,如图5-41所示。

图5-41 增加ChipScope规划示意图

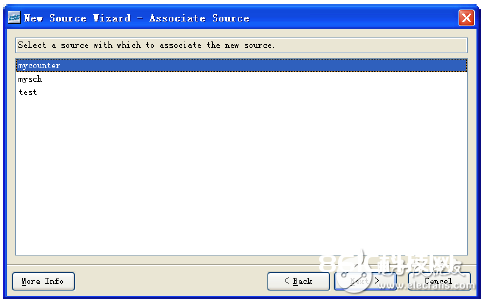

图5-42 测验模块挑选界面

单击“Next”按键,进入剖析文件挑选界面,这里会将该文件夹里一切的HDL 规划、原理图规划都罗列出来( 包含顶层模块和悉数底层模块),供用户挑选,用鼠标单击即可选中,本例挑选mycounter,如图5-42 所示。单击“Next”按键进入小结页面,单击“Finish”按键完结增加。

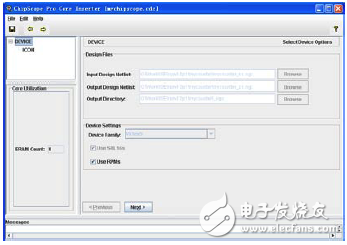

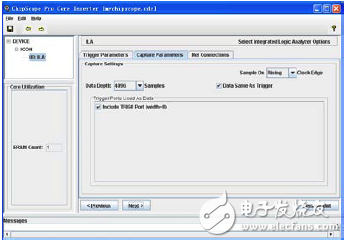

(3) 双击工程区mycounter.v 下的子模块mychipscope.cdc,可主动翻开Chipscope Pro Core Insterser软件,增加触发单元和触发位宽。其间触发类型选为Basic,位宽为8比特;设置采样深度为4096,各进程如图5-43到图5-46所示。

图5-43 调试工程装备界面

图5-44 %&&&&&%ON核装备界面

图5-45 触发信号装备界面

图5-46 收集深度装备界面

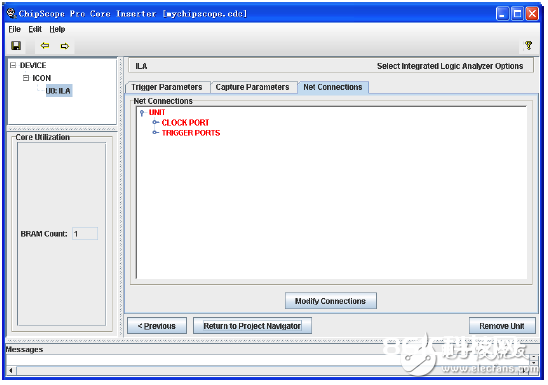

(4) 点击“Next”进入网表衔接显现页面,如图5-47 所示。其间假如用户界说的触发和时钟信号线有未衔接的状况,则图中“UNIT”、“CLOCKPORT”以及“TRIGGERPORTS”等字样以赤色显现;正确完结衔接后则变成黑色。

图5-47网表衔接提示界面

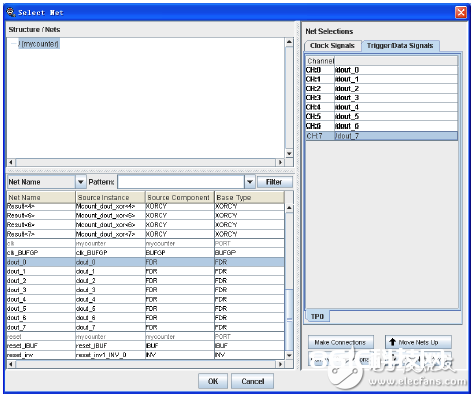

点击图5-47 中“Modify ConnecTIon”的按键,进入衔接页面,时钟和数据的衔接如图5-48、图5-49所示。需求留意的是,ChipScope Pro 只能剖析FPGA 规划的内部信号,因而不能直接衔接输入信号的网表,所以输入信号网表悉数以灰色显现。假如要采样输入信号,可通过衔接其输入缓冲信号来完结,时钟信号挑选相应的BUFGP,一般信号挑选相应的IBUF。如图5-48 中所示,挑选采样时钟时,挑选了CLK_BUFGP。

图5-48 时钟网表衔接界面

图5-49 触发网表衔接界面

衔接完结后,单击“OK”按键回来衔接显现界面,发现一切提示字符“UNIT”、“CLOCKPORT”以及“TRIGGERPORTS”没有赤色,则单击“Return Project Navigator”,退出Chipscope,回来到ISE 中。不然需求再次点击“Modify ConnecTIon”按键从头衔接。

(5) 在工程中参加UCF 文件,束缚时钟、数据管脚方位。为了简化也能够只增加clk 和reset 这两个操控信号的管脚束缚,其内容如下:

NET clk LOC = C9 | IOSTANDARD = LVCMOS33 ;

# Define clock period for 50 MHz oscillator (40%/60% duty-cycle)

NET clk PERIOD = 20.0ns HIGH 40%;

NET reset LOC = H13 | IOSTANDARD = LVTTL | PULLDOWN ;

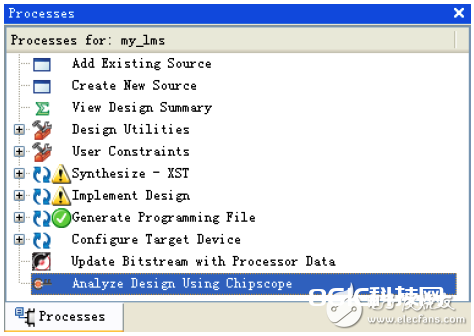

(6) 在ISE 进程操控区中双击“Implement Design”和“Generate Programming File”, 能够完结完结以及生成可编程文件,并将规划人员刺进的各类核也将被包含在比特文件中。生成装备文件后,双击图5-50所示的“Analyze Design Using Chipscope”图标,可主动翻开Chipscope Pro Analyzer 软件。

图5-50 Chipscope Pro Analyzer发动操作示意图

(7) 在Chipscope Analyzer 用户界面上点击东西栏上图标“ ”,初始化鸿沟扫描链。等扫描完结后,单击“Device”菜单下“DEV: 0 My Device0(XC3S500E) → Configure”指令挑选.bit 文件装备FPGA。

(8) 芯片装备完结后,挑选“File”菜单的“Import”指令,可弹出CDC 文件加载页面,挑选相应的CDC 文件,将会把一切以“Dataport”的称号修改为归纳后的线网称号。

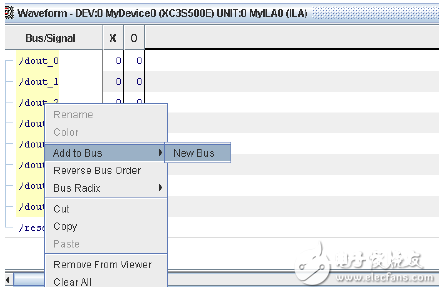

(9) 组合cnt 总线信号。可按住“Ctrl”键,挑选多个总线信号,单击右键,挑选“Add to Bus”指令,将其组合成相应的总线信号,如图5-51 所示。

图5-51 增加总线操作示意图

(10) 不设定触发条件收集数据。点击东西栏的“ ”图标,开端收集数据。全体成果如图5-52 所示,单击东西栏的“ ”按键,可扩大信号,部分成果如图5-53 所示。从剖析成果能够看出,本规划在FPGA中成功地完结了8 比特计数器的功用。

图5-52 Analyzer剖析成果全体示意图

(11) 设定触发条件收集数据。在“Trigger Setup”栏Match 区域的“M0: Trigger Port0”行的Value 列输入触发条件“0000_0000”,如图5-54 所示。

点击东西栏的“ ”图标,开端收集数据,能够看到,收集成果的榜首个数为0,如图5-55 所示。当然,

用户能够依据需求设置更杂乱的触发条件。

(12) 使用Bus Plot 功用制作输出信号波形。在工程区双击“Bus Plot”指令,然后在弹出窗口的“Bus Selection”区域选中“dout”,则会将收集数据以图形方法显现出来,如图5-56 所示。因为本规划是8 比特加1 计数器,因而其波形便是起伏为0 到255 的锯齿波。

图5-56 8计数器的波形示意图