0 引 言

在频谱分析仪中,传统的FFT完结办法首先是对低中频信号进行ADC低采样率采样,然后将采样数据保存在RAM中;当数据满足后,进行FFT运算,将取得的频谱数据显现在屏幕上。这种FFT办法可以说是简单易行,但在处理宽带高中频信号方面,因为受Nyquist采样定理的束缚,需求运用高采样率。此刻完结窄的分辨率带宽将需求许多的采样数据,这就使得体系不只需求进步存储空间,并且添加了运算量,一起有许多冗余输出数据,导致算法的功率十分低下。

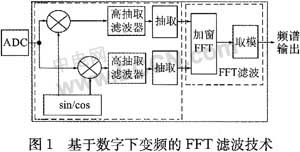

跟着高速A/D改换和DSP技能的开展,软件无线电规划思维也被应用到频谱分析仪中,根据软件无线电数字下变频的FFT技能可以有用削减上述传统FFT技能存在的问题。在高中频、高采样率体系中,能完结信号频谱的高分辨率、低存储量和低运算量,然后极大地进步了体系的实时性。

1 频率分辨率

在频谱分析仪的FFT谱分析中,信号的频率分辨率RBW界说为:

|

式中:fs为采样率;N为FFT点数。

假如考虑选用窗函数,则分辨率带宽RBW界说为:

|

式中:K为窗函数-3 dB带宽因子。

因为fs是ADC的采样频率,是常数,K也是一个定值,因而要减小RBW值,只能添加N。但添加N会添加处理时刻,还要添加存储器容量,所以N的添加受到限制。在频谱分析仪中一般N不大于64K。

2 数字下变频FFT技能

根据数字下变频的FFT技能的完结原理框图如图1所示。

|

假定期望对整个频带中频率为fIF的两头±B/2的一段频率范围内进行FFT,整个处理进程可分为数字下变频和FFT滤波2个模块。

数字下变频模块的处理进程包含以下3个进程:

(1) 数字变频,将感兴趣部分的频谱下变频到零频邻近。先以fs对信号进行采样,得到N点序列x(n),然后与数字本振复信号cos(2πfIFnT)+jsin(2πfIFnT)(T=fIF/fs)进行数字混频,取得I/Q两路信号,将x(n)的频谱x(k)平移了fIF,此刻原信号频率fIF的重量被移至零频处。

(2) 高抽取滤波,用一个带宽等于B的高抽取滤波器(如5级CIC抽取滤波器)对变频至零频的信号滤波,则输出信号含有x(n)在fIF±B/2范围内的频率成分。

(3) 抽取,完结对滤波后信号的抽取。若fs/B=D,得D为抽取因子,此刻输出数据的采样频率缩小了D倍;又因为运用了高抽取抗混叠滤波器,此刻的信号频谱是不会产生混叠的。

FFT滤波模块的处理进程则包含以下2个进程:

(1) 加窗FFT,对经过数字下变频的I/Q两路信号先乘上窗函数,然后进行复数FFT。此刻FFT的点数为M=N/D,其频谱便是fIF±B/2内的频谱,但却有传统N点FFT的分辨率作用。

(2) 取模,便是获取复信号的起伏信息,因为FFT输出值的每个点对应一个频率点,所以输出的便是信号的频谱。

高抽取滤波的运算量和存储量一般都比较小,比方C%&&&&&%抽取滤波器的滤波系数都是1,不需求乘法运算,所需的存储空间等于抽取比D;而后续的FFT只需对M=N/D点数据进行FFT改换,数据存储量和运算量都远低于传统的N点FFT,数据存储量和运算量的大起伏下降必将导致大起伏削减处理时刻。上述内容均阐明,根据数字下变频的FFT技能比传统的FFT技能在进步体系的实时性方面具有更大的优越性。

3 数字下变频FFT在频谱分析仪中的完结

在某新式频谱分析仪中,根据数字下变频的FFT技能得到成功完结,该技能是在根据TI公司DSP芯片TMS320C6701的数字信号处理体系中经过软件处理得以完结的。

图2是该数字信号处理体系的硬件结构框图。在该体系中,模仿中频信号由同轴电缆输入,经中频预滤波和ADC采样后,数据经过FIFO送给TMS320C6701。TMS320C6701主要是做根据数字下变频的FFT,其完结根据前面描绘的完结原理来规划的。大局操控器FPGA主要是完结整个体系的扫描操控。当FPGA在收到采样指令后发动ADC收集,收集的数据直接缓存在FIFO中。当FIFO数半满时,将触发TMS320C6701外部中止和内部DMA中止,DMA处理程序将FIFO数据送入DSP的外部SDRAM数据存储器。当数据满足时,TMS320C6701对采样数据进行数字下变频和FFT处理,把成果转化成主机能接纳的数据格式送人双口RAM,主-机则实时从双口RAM读取频谱数据,转换成数据显现在屏幕上。此外,主机则把操控指令送到双口RAM,经过HPI中止告诉DSP接0收。