导言

当今许多工业和仪器仪表运用都涉及到传感器丈量技能。传感器的功用是监测体系的改动,然后将数据反馈给主控制单元。关于简略的电压或电流丈量,传感器能够呈阻性。但在某些传感器体系中它却呈理性或容性,这意味着传感器在其作业规模内的阻抗改动呈非线性。

这种复数传感器的典型比如是挨近传感器——用来确认相对移动物体的间隔;以及容性传感器或理性传感器——在医学职业中用来丈量血液流速以及剖析血压或血质。

丈量这些“复数传感器”的阻抗需求一个在传感器频率规模内扫描的鼓励源。本规划思维标明怎么能够方便地运用单芯片数字波形发生器供给这种大于10 MHz的频率扫描。本文也将介绍一种集成鼓励源、模数转换器(ADC)和信号处理的完好单芯片阻抗转换器(IDC),然后使它合适需求高达约达50 kHz鼓励频率的运用。

传感器:作业原理

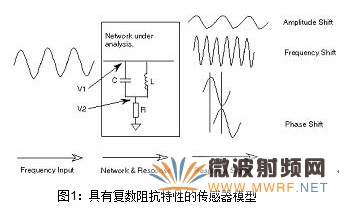

图1示出一种具有理性阻抗或容性阻抗特性的传感器模型。

经过传感器的鼓励频率依据其电感(L)或电容(C)的瞬态值改动将表现出一种起伏、频率或相移改动。例如,超声波液体流量计一般表现为相移改动,而挨近传感器则是起伏改动。

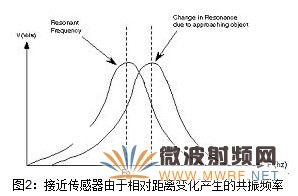

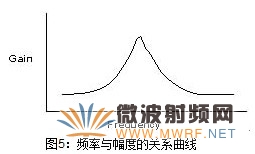

盯梢这种阻抗改动的最常用的办法便是监测电路的共振频率。共振频率是指%&&&&&%值等于电感值时对应的频点,这也是频率曲线上的最大阻抗处对应的频点。例如,考虑图2所示的挨近传感器的状况。在正常作业方式下,即静态条件下,传感器的L、R和C具有仅有的值,这种状况在共振频点将具有最大阻抗。当移动物体挨近传感器时,传感器的L和C值会发生改动,然后发生了新的共振频率。假如监测共振频率的改动(然后监测阻抗)能够猜测移动物体相对传感器的间隔。

核算共振频率

核算电路的共振频率需求一个沟通(AC)鼓励信号源,它在一段频率规模内扫描以绘出如图2所示的频率与阻抗联系曲线。AD9833单芯片数字波形发生器可供给一种发生这种扫描输出的简略、低本钱办法。咱们经过写入代表所需频率的数字码字来改动输出频率。AD9833具有两个频率寄存器,然后答运用户在对一个频率寄存器编程的一起输出第二个频率寄存器。

AD9833具有许多长处:输出频率的分辨率是28 bit,所以用户能够以小于0.1 Hz的步幅添加输出频率。其输出频率规模是0~12.5 MHz,然后供给很宽的传感器挑选灵活性。例如,有些传感器具有很低的频率规模,但在该频率规模内需求很高的分辨率;而别的一些传感器则需求以较低的分辨率调理很宽的频率规模。

运用频率扫描办法,能够很容易地核算出传感器的共振频率,而且能够运用该数据供给许多运用的传感器检测信息。

体系框图

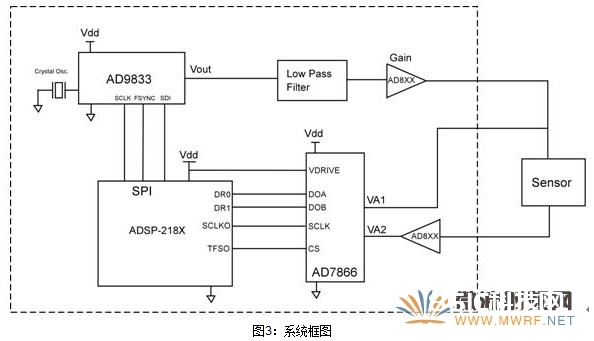

图3示出完结这种丈量的体系框图。AD9833数字波形发生器可经过ADSP-218x数字信号处理器(DSP)对其设置。首要有必要对AD9833的正弦输出电压波形进行低通滤波以去除来自主时钟(MCLK)、镜像频率和高阶频率的馈通。然后将经过滤波的信号用作传感器的鼓励信号。依据传感器的阻抗改动,将呼应信号扩大以使其合适ADC的动态规模。传感器的输出和鼓励频率都馈送到AD7866 12 bit 1 Msps同步采样双ADC。在将ADC的输出数据馈送到DSP,以便经过核算传感器的起伏和相位改动做进一步的剖析。

完好的集成传感器解决方案

图3所示的分立解决方案尽管有助于各种通用传感器的阻抗丈量,但运用的宽带元件使该其本钱贵重。单个分立元件会添加其本身的差错源,而且有源元件会添加相位差错,所以有必要经过校正将这些差错消除去。必定需求DSP处理杂乱的数学运算,而且还或许需求外部存储器来存储ADC的原始数据,这样会进一步添加本钱。

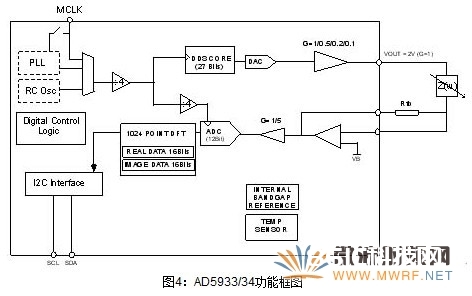

假如仅需低频传感器剖析,咱们可供给一种低本钱的解决方案。AD5933/34 12 bit IDC和网络剖析器将上述首要处理框图集成到一颗单芯片%&&&&&%(%&&&&&%)。图4示出其功用框图。

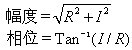

频率发生器答应运用高达50 kHz的已知频率鼓励100 Ω~20 MΩ规模的复数阻抗。呼应信号由内置ADC采样。内置DSP引擎完结ADC输出的离散傅立叶改换(DFT)。然后DFT算法回来实部(R)和虚部(I)数据字,然后答应方便地核算其阻抗。运用以下公式能够方便地核算阻抗的起伏和相位。

咱们运用频率扫描来确认实践的实部阻抗值Z(ω)。咱们能够在每一个频点核算阻抗,而且能够树立频率与起伏的联系曲线。

用户能够设置2 V、1 V、500 mV或200 mV的峰峰值正弦信号作为外部负载的鼓励源,而且可到达27 bit(小于0.1 Hz)的频率分辨率。

为了完结频率扫描,用户首要有必要设置扫描所需的作业条件:开端频率、频率步幅以及步数,然后需求一个发动指令开端扫描。在每一点扫描频率处ADC都完结1024点采样而且核算DFT认为波形供给实部和虚部数据。将该实部和虚部数据经过I2C接口以两个16 bit字的方式供给给用户。假如其内置DSP有处理引擎,则意味着用户不用处理杂乱的数学核算。它也无需存储ADC原始数据,仅需回来两个16 bit的字。还能够选用下降功用和下降本钱的DSP解决方案,由于现已显著地下降了对处理才能的要求。阶跃呼应的增益可设置为1或5倍。其ADC是一款3 V电源供电的低噪声、250 ksps或1 Msps采样率的高速ADC。体系时钟经过MCLK端的参阅时钟从外部供给,MCLK可从外部晶体振荡器或经过内部PLL单元供给。