在学习单片机的进程中,我常有这样的烦恼:马马虎虎一个芯片,少则占用三五个IO口,一般的就占用8个,略微想用多一点芯片吧,老觉得IO口不够用。学串口的时分觉得串口是个好东西,连两条线就够了,现在学到I2C,觉得这也是一个非常好的东西,也是两条线,还能给每个总线上的设备建立地址,几乎便是一个小网络了。

I2C总线运用两条线,一条是时钟线,称为SCL,一条是数据线,称为SDA,各个设备就并在总线上,每一个总线上的设备都有一个自己的地址,主机在操作设备的时分,都会先发送一个地址码,告知被操作机,接下来的指令由它接纳。

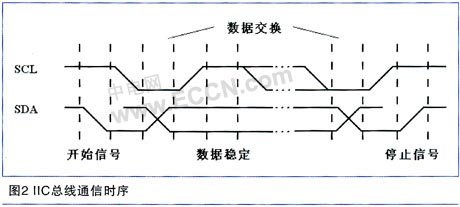

接下来说一下I2C总线的数据有效性。I2C总线进行数据传送时,要求SCL为高电平时,SDA上的数据必需坚持稳定,换言之,当SCL为高电平时,SDA的电平不能改换,只要当SCL为低电平时,SDA的电平才干变。

I2C总线通讯时,需求遵循必定的协议,以下为一次通讯进程:

- 由主机发送开端信号,发动I2C总线。时序为,在SCL为高电平期间,SDA呈现一个下降沿。

- 主机发送寻址信号,即告知特定的设备,接下来的指令是发给它的。地址分为7位和10位,以7位为例,高7位为设备地址,最低位一共读或写,1一共读,0一共写。

- 应对信号,I2C协议规则,每传送一个字节数据(包含地址及指令)后,都要有一个接纳设备回来的应对信号,以确认信号是否被接纳设备正确接纳到了。其时序为,在SCL信号为高电平期间,接纳设备把SDA电平拉低。

- 数据传输,当主机发送发址并收到应对后,就可以发送数据了,可是发送数据只能每次发送一位,而且每发送一位后都需求收到接纳机的应对。或主机为接纳设备时,主机对最终一个字节不应对,一共向发送设备说,数据传送完毕。

- 发送中止信号,在悉数数据传送完毕后,主机发送中止信号,时序为,在SCL为高电平期间,SDA上发生一个上升沿。

前面讲到,I2C协议要求数据的发送,要求SCL为低电平时,SDA才干改换,看一下上面的时序,可以看到,指令都是SCL为高电平时对SDA的操作,而发送数据则是SCL为低电平时对SDA操作。

这次拿来做实验的是AT24C02存储芯片,在Proteus晒干,它叫24C02C(或许24C02B),是一个2K bit的I2C总线的EEPROM存储器,换成电脑上常用的KB也便是256KB,EEPROM一共它保存了今后不必加电池,也能坚持数据无缺。实验的做法是,先把数据保存到芯片中,然后再读出来,显现到1602液晶上。

上面介绍了I2C总线的协议格局,即发送一个指令的格局,可是关于每一个设备来说,要操作它,是需求许多指令的,AT24C02的操作则主要是读和写,它分为页读写(即一次读写一大片)和字读写(一次读写一个字节)两种方法,初学么,只运用字读写方法,下面记载一下读写的时序。

首先是写数据,时序如下:

1.发送发动信号

2.发送一个操控字(即芯片的地址)——等候应对

3.发送要写的芯片内存储单元地址——等候应对

4.发送要写入的数据——等候应对

5.中止信号

接下来是读数据的时序:

1.发送发动信号

2.发送一个操控字(即芯片的地址,最低位为0即写操作)——等候应对

3.发送要读取的芯片内存储单元地址——等候应对

4.再发送一个地址信号(同第2步,可是最低位为1,即读操作)——等候应对

5.按每次一位,读取数据

6.中止信号

I2C协议看起来相对杂乱,可是在单片机晒干完成,其实便是用两个IO口,来模仿SCL和SDA的电平改动。以发动I2C为例(在SCL为高电平时,SDA发送一个下降沿),代码如下:

SDA = 1;//把SDA先置高电平,待会好呈现下降沿

delay();

SCL = 1;//SCL要晚于SDA设置,不然简略和其他指令混杂

delay();

SDA=0;//电平从1到0,呈现一个下降沿

delay();

———————————————————————

Proteus电路图如下,记住要在总线的两条线上,接上拉电阻(10K即可)

成果如下:

这儿还得说一下I2C DEBUGGER这个虚拟仪器,真的是挺好用的,把它接在总线上后,它会把每一个指令都显现出来,并把操作归于哪一种操作都标识出来,以我往芯片存一个字符“H”为例:

它把每一步都标的清清楚楚,特别阐明一下的是,几个字符是有特别含义的,如:

S表是I2C总线-“开端”

A—应对

p—中止

Sr–重发动

所以榜首行S A0 A 01 A 48 A p一共的意思是:发动I2C总线,发送数据A0(其实是芯片的地址),芯片应对,发送数据01(便是写入的地址),芯片应对,发送数据48(便是保存的数据),芯片应对,完毕。看看,是否和前面说的流程共同?

程序这儿不贴了,下载里都有,晒干有具体的注释。

PS:在调试时遇到的一个问题,或许我们也会碰到,记载一下。

我本来是循环着往芯片晒干写数据,然后读出来,显现到液晶上,这时读写都正常,方法如下:

for(i=0;i<字符串长度;i++)

{

save(‘a’)

read(‘a’)

}

后来我为了实验多显现几个字符,换了种方法,换成一次把一切数据都保存进去,再读出来,变成下面的方法(伪代码):

save(‘a’)

save(‘b’)

save(‘c’)

read(1)

read(2)

read(3)

这时呈现了一个问题,榜首个能正常保存,第2个就不能保存,第3个又能保存,让我很是头疼。

后来剖析了一下,前后两种代码的差异,就在于,榜首种方法,保存后,又进行读取,相当于保存后进行了必定的延时,而第二种方法一直在保存,保存后没有延时,后来在第二种方法的save后,加上了延时,就一切正常了。

源代码下载:点击下载

IIC总线技能

IIC总线是微电子通讯操控范畴中被广泛选用的一种总线规范,具有接口线少,操控方法简略、器材封装外形小、通讯速率高级特色。它仅经过两根线SDA和SCL即可完成完善的全双工同步数据传送,可以非常方便地构成多主机体系和外同器材扩展体系。

IIC总线数据传输只要任总线处于闲暇状况时(SCL和SDA有必要确保为高电平)才发动。IIC总线协议界说数据传输时序如图2所示,开端条件为当SCL为高电平时,SDA由高电平向低电平跳变,数据开端传输;完毕条件为当SCL为低电平时,SDA由低电平向高电平跳变,数据传输完毕。传输进程中,当SCL高时,SDA有必要一直坚持稳定状况,此刻呈现任何跳变都被以为是开端或中止条件,只要当SCL为低电平的时分才答应SDA上的数据改动。

I%&&&&&%总线上的数据格局如图3所示,由开端位(S)、从机地址码、读写操控位(R/W)、应对位(A)、数据和中止位(P)等组成。通讯发动时,主器材先发送发动信号和从机地址,总线上每个器材都有自己的仅有地址,与地址与某一从器材相匹配时,该从器材发一应对位,主器材则以为寻址成功,然后依据R/W位确认的数据传送方向进行数据传输。若主器材长期收不到应对位,则以为超时,抛弃本次数据传输。通讯中止时,主机发送一个中止信号。