一.概述

本文首要协助咱们了解运用ISE进行Xilinx 公司FPGA 代码开发的根本流程。首要是协助初学者了解和开端把握 ISE 的运用,不需求 FPGA 的开发根底,所以对每个进程并不进行深化的评论。

本文介绍的内容从新建 project 一直到下载到硬件调查现象停止,包括整个开发进程。考虑到咱们的开发一般以 Verilog HDL 或 VHDL 为主,在本文中未介绍原理图输入东西和 IP 核运用东西等。这一起是出于为了使文章头绪更明晰,让咱们更快地学会 ISE 的考虑。关于这些专用东西,能够参看 HELP 或许其他文档。

为了更直观的了解,咱们需求一个试验渠道,在本文中,选用的是 Digital Power Studio 工作组 FPGA SPARK1.1 归纳开发渠道的 Xilinx 规范型开发体系。如图 1 所示(图中为 Altera 子板,只需改成 Xilinx 的即可)。在该开发体系中,所选用的芯片是SPARTANII系列的XC2S200 。

图1 FPGA SPARK1.1 外观图

二.完结功用

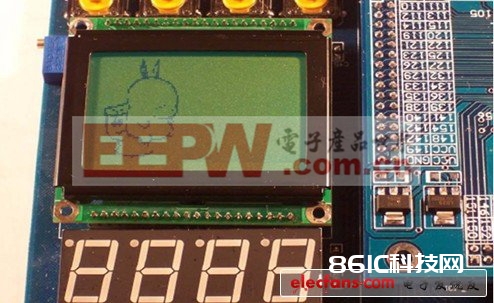

在如上体系中右边有一个 128×64 带背光的点阵型液晶。咱们的试验便是用Verilog HDL 编写一段代码驱动液晶显现一个流氓兔。其作用如图 2 所示:

图2 点阵液晶上显现流氓兔的作用图

三.软件预备

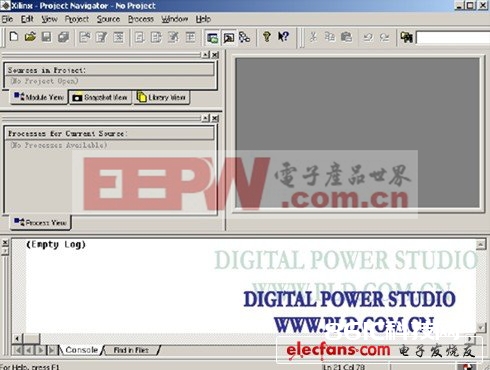

本文介绍的是 Xilinx 公司的 ISE 开发环境。现在最新的版本是 ISE7.1,其界与 ISE5.x/ISE6.x 共同。为了更好地进行仿真,还需求装置 Modsim。可是 ISE本身能够进行仿真,也能够不装置 Modsim。流程介绍:

1.新建项目

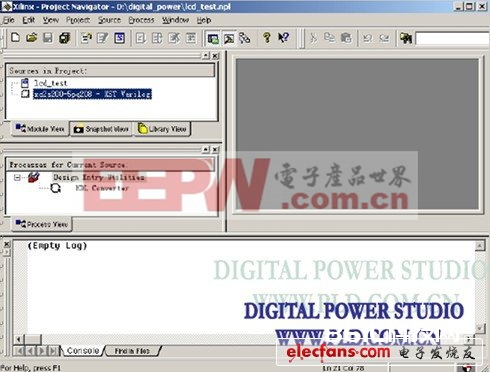

在开端—〉程序—〉Xilinx ISE 中找到 Project Navigator,点击翻开。也能够经过双击桌面上 Project Navigator 的快捷方法翻开。ISE 开发环境如图 3 所示:

图3 ISE 开发环境

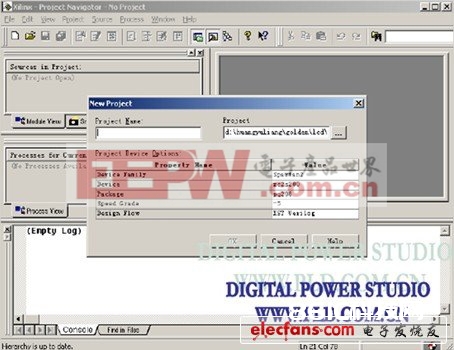

图3 中挑选 File—〉New Project,进入图 4;

图4 新建 project 界面

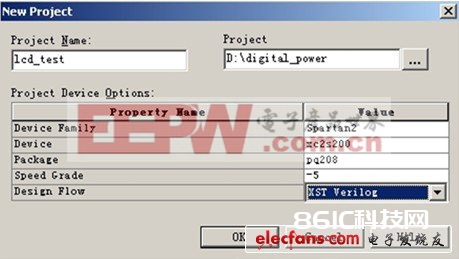

在 Project Name 栏输入项目名称,Project 中填入该项意图目录,Project Device Options 中,Device Family 为所用芯片地点系列,Device 为所用芯片,Package为所用芯片的封装方法(每个芯片可能有不同封装的几种,如 XC2S200 有 3 种封装的),Speed Grade 为速度等级,Design Flow 为所选用归纳方法(归纳东西

和代码言语)。因为选用的是 FPGA SPARK1.1,选用如图 5 的设置。

图5 新建项意图信息输入

其间 XST Verilog 表明选用 ISE 自带的归纳器,代码言语为 Verilog HDL,ISE支撑其他归纳东西的调用,也支撑规范 edif 文件的输入。XST 是 ISE 自带的归纳东西,因为 Xilinx 对本身的硬件了解程度比任何第三方软件开发商都更深,故XST 的归纳性能有本身共同的长处。

点击 ok,新建项目完结。能够在相应目录下看到生成的文件。作用如图 6。假如要更改硬件的设置,能够双击图 6 中模块视窗内蓝色选中的所示对应选单,即可进入 project properties 界面从头进行设置。

图6 作用图