0 导言

跟着半导体技能的高速开展,大规模集成电路变得愈加杂乱,开发周期变得更长。FPGA因为具有可编程性,其广泛运用能够下降电路的开发本钱。但是,单粒子翻转(SEU)会使FPGA内部的很多的存储器变得不牢靠,尤其是Static RAM(SRAM)型FPGA的装备存储器遭到重离子轰击时,会导致器材逻辑布线犯错,然后引起模块毛病,乃至导致整个体系的功用中止。关于SRAM型FPGA,装备存储器的单粒子翻转占整个器材翻转总数的90%以上的份额[1],因而对装备存储器的单粒子翻转防护十分重要。

现在也有一些办法能够对立SEU。三模冗余(Triple Modular Redundancy,TMR)是一种常用的有用加固规划,能够有用进步牢靠性。TMR的每一个冗余支路能够屏蔽一个过错,但无法处理多比特翻转,尤其是3倍资源的耗费也会影响整个器材的运转功耗。为了削减资源的耗费,文献[2]提出了一种依据双模冗余(Double Modular Redundancy,DMR)的检错电路,它以较小的资源价值来处理多比特翻转;文献[3]提出了一种星载信号处理渠道结构,运用高牢靠性的反熔丝Actel FPGA对Xilinx V4系列 FPGA进行监控和改写;文献[4]介绍了FPGA的改写规划要处理Half-latch,来防止回读无法发现的过错;文献[5]介绍了一种高效的加固测验的办法;文献[6]提出了依据ZYNQ加固的技能。

跟着技能的开展,功用模块的集成度逐步进步,Xilinx公司Kintex-7系列FPGA是当下较为遍及的处理器,而对其的单粒子防护变得更为火急。为了进步牢靠性,有用对立空间辐射引起的毛病,本文提出了一种依据高牢靠性反熔丝Actel FPGA对Xilinx Kintex-7 FPGA进行回读、校验和改写的处理渠道。

1 空间辐射

空间中的电子器材,会遭到空间中很多高能辐射粒子(质子、电子、α粒子、重离子、γ射线等)的效果,高能粒子对半导体器材PN结的磕碰,在重粒子的运动轨道周围构成电荷被PN节活络电极搜集构成瞬态电流,当瞬态电流超越必定值就会触发逻辑电路,将形成半导体存储器或触发器的翻转、逻辑功用的瞬时反常或中止,即单粒子效应。

依据单粒子效应的产生机理,能够对航天运用中的集成电路芯片进行加固,以削减单粒子效应对体系功用的影响。关于单粒子效应的加固,从加固办法上可将其分为工艺上加固和功用上加固两大类。

工艺上的加固指的是选用抗辐射才能强的工艺和资料,制作出具有较高抗辐射才能的器材,例如宇航级的器材,它自身就进行了辐射加固规划。功用上的加固是指经过复位或许重写操刁难器材进行修正,将单粒子效应引起的过错逻辑进行纠正,然后到达抗辐射的意图。

2 研讨现状

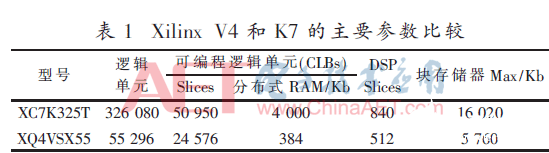

美国的猎奇号探测器、金星快车探测器均运用Xilinx公司的宇航级FPGA,现在该公司的抗辐射FPGA产品如Virtex-4QV(以下简称V4)被认为是用于空间运用的老练处理器。但其昂扬的价格和较长的收购周期进步了国内相关范畴的研讨本钱。Xilinx制作的Kintex-7(以下简称K7) FPGA具有低功耗高性价比的长处,而且可用资源比抗辐射的V4有较大优势,表1比较了V4(具体型号为XQ4VSX55)和K7(具体型号为XC7K32ST)两款芯片的首要参数[7]。

XC7K325T的逻辑单元是XQ4VSX55的5.9倍,DSP资源是它的1.6倍,丰厚的资源供给了杂乱信号处理的处理才能,一起为体系的小型化规划供给了牢靠的处理方案。

XC7K325T和XQ4VSX55均选用SRAM型结构,其首要硬件组成为:可装备存储器(Configurable Memory)、可编程逻辑单元(Configurable Logic Block)、可编程输入输出口(Programmable IO)、块存储器(BlockRAM)、乘法器(MulTIplier)、数字时钟办理模块(Digital Clock Manager)、装备状况机(ConfiguraTIon State Machine)、上电复位状况机(Power On Reset State Machine)、布线资源(RouTIng Resource)。

因为选用SRAM型结构,经过相关试验标明,FPGA毛病多数是由可装备存储器产生单粒子翻转(SEU)引起的[8]。可装备存储器操控着FPGA规划中的操控位(Control Bit)、查找表(Look Up Table)、开关矩阵(MulTIplexiers)、可编程互连点(Programmable Interconnect Points)和布线缓存器(Routing Buffer)。依据可装备存储器中各类功用位所占的份额,能够判别可装备存储器单粒子翻转首要引起布线资源的过错。单粒子翻转影响它地点功用模块的功用,但并不必定引起整个器材信号处理功用的失效,而且此类毛病能够经过改写来修正。

3 加固渠道规划

3.1 总体规划

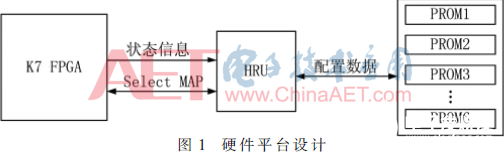

本单粒子加固渠道首要由高牢靠性单元(High Reliability Unit,HRU)、XC7K325T和PROM组成。其间,信号处理部分由一片FPGA完结,高牢靠单元完结对FPGA的装备、监控、回读校验和改写功用。依据XC7K325T的抗SEU渠道规划框图如图1所示。

图中K7 FPGA和反熔丝HRU直接交互,一起HRU直接与存储芯片衔接,程序选用帧校验的办法来比对K7 FPGA中的装备位,存储芯片17V16的巨细为16 Mb,经过核算共需求6片17V16。

3.2 K7的上电装备

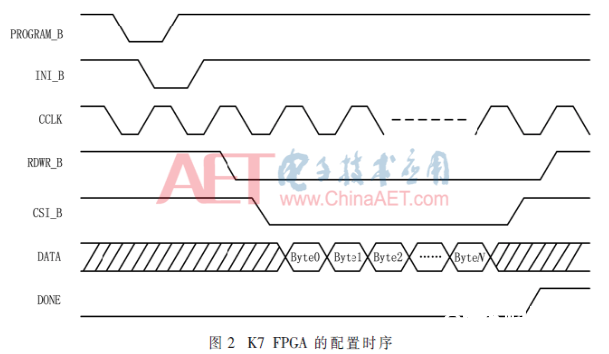

该渠道作业流程是,体系加电后,HRU首要装备K7,依据K7的装备时序图(如图2所示),首要置低PROGRAM_B引脚,初始化K7的装备寄存器,当INIT_B引脚变高后,这时再将PROM中的程序下载到K7中,当装备完结后,K7的DONE引脚会变高,意味着装备成功,此刻K7开端作业;这时HRU首要检测装备是否成功,假如未成功,则重新装备;假如装备K7成功后,它的看门狗电路开端作业,这时HRU进入监测状况,实时地检测K7的作业状况。

其间K7的各个装备引脚的界说如表2所示。

3.3 K7的回读校验与改写

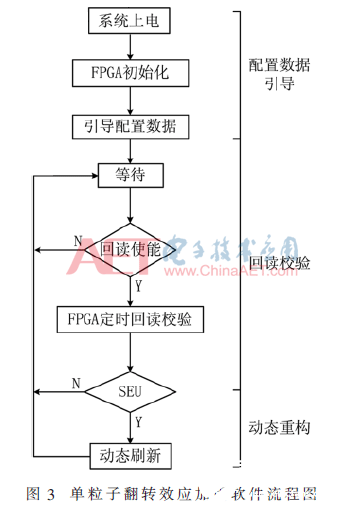

当K7装备完结后,等候回读校验指令对器材进行回读测验。K7的回读校验选用按帧编码校验的办法。在回读进程中,对犯错的帧进行记载和数传。当K7的回读校验都完结今后,进行过错判定。假如检测犯过错,则对相应的器材进行动态重构处理,使其康复到原始规划状况。完好的K7抗SEU加固软件履行流程如图3所示。

其间检测K7的状况是经过回读操作完结的,回读是经过SelectMAP接口将K7内部装备存储器中的数据读出的进程。回读进程能够读出K7存储器的当时状况以及布线资源的装备状况等,然后经过检测回读数据来判别当时装备数据的正确性。回读校验是K7单粒子效应毛病检测的重要办法。回读进程分为写操作指令、读取数据和康复现场三部分。FPGA每一帧回读数据的内容都决议着与其相对应的功用模块的逻辑功用。经过对装备存储器的回读和校验,HRU能够决议是否需求对该功用模块进行部分重装备。

4 运用验证

本规划选用的动态回读是在不中止正在运转的电路逻辑功用的状况下对装备存储器的回读。当回读发现K7的装备数据反常时,则进行改写操作。改写操作是在对方针器材K7的过错装备数据进行重构修正,经过以上流程HRU能够完结对XC7K325T的SEU加固。

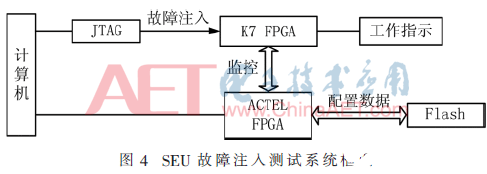

为经过模仿XC7K325T空间环境运用时产生SEU,对加固软件的回读校验和改写功用进行测验。测验体系组成如图4所示。

测验体系首要由毛病生成核算机、XC7K325T和HRU组成。为了调试便利,用Flash存储K7的装备文件,核算机经过JTAG口将过错的装备信息烧录到FPGA中,HRU经过与Flash存储的装备文件比对,检测出SEU后施行改写操作。经过作业指示能够监测当注入过错的装备信息后K7的作业状况,随后当回读校验改写时,FPGA的原有的装备程序功用康复。

测验首要分为以下几个过程:

(1)以存储在Flash中的装备文件为根底,修正其间的一位或几位,并生成校验正确的装备文件;

(2)将两种装备文件的作业指示加以差异以便监测改写操作;

(3)模仿SEU注入修正过的装备文件,并调查作业指示;

(4)等候程序中设定的校验时刻后,经过作业指示判别HRU是否检测到了翻转并施行改写操作;

(5)改动翻转的数目和毛病注入的方位,重复试验。

测验标明,HRU加固软件能够正常完结对单片XC7K325T的上电装备,检测XC7K325T装备存储区的SEU和修正功用。

5 后续作业

FPGA单粒子效应毛病加固规划,针对程序代码自身还需求添加以下几项作业,来添加全体渠道对立SEU的才能:

(1)关于FPGA中的要害逻辑模块,要采纳三模冗余[9]规划TMR(Triple Modular Redundancy);

(2)假如FPGA对信号的运算速度要求宽余,能够运用检错算法来判别FPGA的逻辑运转是否正确[10];

(3)能够在程序中添加逻辑探针,用区域束缚布线的办法固定在FPGA重要模块的邻近,实时对该区域的单粒子效应进行检测。

6 结束语

本文经过剖析空间辐射的特色,结合SRAM型FPGA的硬件结构,论述了单粒子翻转引起SRAM型FPGA的毛病机理,结合工程实践提出了一种运用高牢靠单元对XC7K325T进行装备、监控、回读校验和改写功用的抗单粒子翻转的加固渠道规划。模仿了毛病注入对加固规划进行了测验,测验标明该加固渠道规划能够完结对FPGA监控和修正,为Kintex-7 系列大容量的FPGA在空间环境中运用供给了规划参阅。试验标明该渠道能够有用修正单粒子效应引起的位翻转和功用毛病。

参阅文献

[1] 王跃科,邢克飞,杨俊,等。空间电子仪器单粒子效应防护技能[M]。北京:国防工业出版社,2010.

[2] AMAGASAKI M,NAKAMURA Y,TERAOKA T,et al.An area compact soft error resident circuit for FPGA[C].IC Design and Technology 2016 International Conference(ICICDT),2016.

[3] 邢克飞,杨俊,王跃科,等.Xilinx SRAM型FPGA抗辐射规划技能研讨[J]。宇航学报,2007,28(1):123-129.

[4] 邢克飞,杨俊,周永彬,等。星用SRAM型FPGA加固规划办法研讨[J]。电子器材,2007,30(1):202-205.

[5] 王鹏,张道阳,芦浩,等。依据分区测验的翻转毛病注入办法研讨[J]。电子技能运用,2017,43(8):88-91.

[6] 张小林,丁磊,顾拂晓。依据三层级低开支的FPGA多比特翻转缓解技能[J]。电子技能运用,2018,44(4):61-64.

[7] Virtex-7 FPGA user guide[Z].UG470(v1.4),Xilinx,2012.

[8] 林金茂.SDR渠道抗SEU功能点评要害技能研讨[D]。长沙:国防科学技能大学,2009.

[9] 黄锦杰,孙鹏,沈鸣杰,等。依据TMR的FPGA单粒子加固试验探求[J]。复旦学报(自然科学版),2011,50(4):477-484.

[10] 李梦良,乐立鹏,张建军,等。星载65 nm抗辐射GNSS接收机ASIC的SEFI试验办法[J]。电子技能运用,2017,43(1):53-56.