本文介绍了一种根据FPGA的视频、音频、反向数据的长途传输体系的研讨与规划,该体系在实践中得到了使用,具有杰出的稳定性、实用性和可靠性。

导言

现在在高速公路、交通、电子警察、监控、安防、工业自动化、电力、海关、水利、银行等范畴视频图画、音频、数据、以太网、电话等光端机开端广泛很多使用。

因为数字光端机具有传输信号质量高,没有模仿调频、调相、调幅光端机多路信号同传时交调搅扰严峻、简单受环境搅扰影响、传输质量低质、长时刻作业稳定性差的缺陷,因而许多大型重点工程已广泛选用数字光端机。

体系结构与作业原理

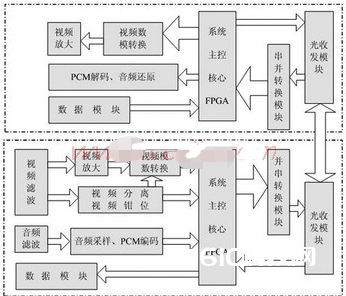

整个体系由中心操控模块FPGA、音频采样编解码模块、视频别离模块、视频扩大模块、视频A/D和D/A转化模块、并串/串并转化模块、光纤调制收发模块、电源操控模块和485数据传输模块。图1是该体系的体系框图。

图1 体系结构框图

体系的作业原理为:光端机体系分为两部分,分别为:发射机和接纳机。在发射端,来自监视器或其他视频源的视频信号首要经过发射板上的视频滤波网络去除噪声搅扰信号,然后对该视频信号进行视频别离和视频扩大。视频别离模块得到视频信号的行、场同步信号以及奇偶场信号、视频钳位等重要的视频信息。接下来,对扩大后的视频信号进行A/D转化,得到的数字化的视频信号送入体系主控中心FPGA中。与此一起,假如体系检测到了有音频信号的存在,则对其进行音频滤波、音频数字化采样以及音频PCM编码。经过PCM编码后的音频信号,送入体系主控中心FPGA中。反向数据传输首要是485信号,该信号也送入到FPGA。这样,体系主控中心FPGA对来自不同模块的视频、音频、数据等信号整合,时分复用地将各个信号编码成8位并行信号流送入到并串转化模块。信号流经过并串转化后变成高速的LVDS信号驱动光纤收发模块以波分复用的方法完结了电/光改变和光发射。在光端机的接纳端,经过以上的逆进程,完结对原始信号的康复。

体系硬件组成

1、FPGA中心操控器

体系的中心操控部分是整个体系的心脏,为了满意对高速、多路数据流的实时处理,要求体系中心操控器有必要有较高的作业频率和反响才能。其次,关于体系时分复用部分,为了信号的同步化,需求体系中心操控器内嵌RAM和FIFO等功用块。此外,一起作为嵌入式体系,处理器有必要有着低功耗的要求。现在,FPGA处理器现已广泛工业操控、消费电子产品、通讯体系等各类产品商场。依照低成本、低功耗、小体积、多功用及较为强壮的数据处理才能,Altera公司CycloneII系列的EP1C3144是一个非常好的挑选。

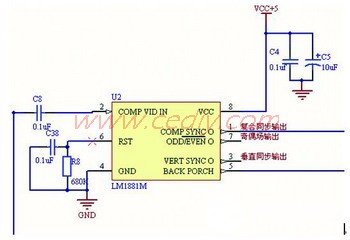

图2 视频别离硬件电路

2、视频别离模块

视频信号中除了包含图画信号之外,还包含了行同步信号、行消隐信号、场同步信号、场消隐信号以及槽脉冲信号、前均衡脉冲、后均衡脉冲等,因而,若要对视频信号进行收集,就有必要精确地掌握各种信号间的逻辑关系。LM1881便是针对视频信号的同步别离而出产的,它为视频信号的处理供给了极大的便利。此处电路规划如图2所示。

LM1881能够从0.5~2V的规范负极性NTSC制、PAL制、SECAM制视频信号中提取复合同步场同步、奇偶场辨认等信号,这些信号都是图画数字收集所需求的同步信号,有了它们,便可确认收集点在哪一场,哪一行。LM1881也能对非规范的视频信号进行同步别离,经过固定的时刻延迟发生默许的输出作为场同步输出。

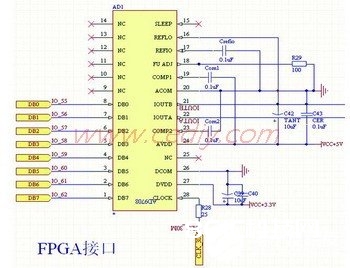

图3 A/D转化硬件电路

3、A/D和D/A转化模块

此处的A/D转化电路首要用来对视频滤波,扩大后的视频信号进行数字化改换。电视图画信号的带宽理论核算值为7.37MHz,实践取5.5275MHz。由香农定理知,ADC的采样频率应该大于2倍的图画最高频率,所以ADC选用ADI公司的AD9280,作业频率为32MHz。该ADC具有杰出的差分非线性度、模仿输入超出转化量程提示、内建自流电平回复和可调片内电压基准源等优势。

此处A/D转化电路规划如图3所示。

接纳端A/D转化电路首要完结对数字化后的视频信号的模仿改换,复原出规范的视频信号。此处选用的DAC为ADI公司的高速AD9708。

AD9708选用+3V或+5V单电源供电,两路电流输出,转化速率高达125MHz,树立时刻不大于35ns,转化精度为1/4 LSB。在+5V电源供电的情况下,其功耗为175mW;在+3V电源供电的情况下,其功耗为45mW。

为了特别的需求,AD9708还兼容8位、10位和12位并行数据输入。当AD9708被设置成8位数据输入时,只要把管脚1设为最高输入有用数据位(MSB),管脚8设为最低输入有用数据位(LSB)即可。引脚1(DB13):最高输入有用数据位;引脚2~13(DB12~DB1):数据输入端;引脚14(DB0):最低输入有用。

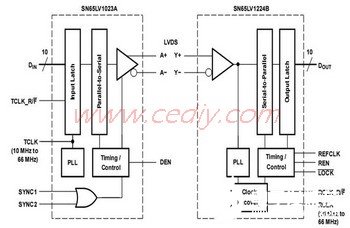

4、并串/串并模块

低压差分信号是由ANSI/TIA/EIA-644-1995界说的用于高速数据传输的物理层接口规范(LVDS)。它具有超高速(速率可达1.4Gb/s)、超低功耗和低电磁辐射等特性,因而是在铜介质上完结千兆位速率通讯的优选计划。而总线形低压差分信号LVDS是LVDS技能在多点通讯范畴的扩展,它要求有更大的驱动电流(10mA)和更好的阻抗匹配规划。

SN65LV1023和SN65LV1224是TI公司推出的10位总线型低压差分信号的使用芯片组。其间SN65LV1023是可将10位并行CMOS或TTL数据转化为具有内嵌时钟的高速串行差分数据流的串化器;而SN65LV1224则是接纳该差分数据流并将它们转化为并行数据的解串器,它一起又能够重建并行时钟。选用该器材组进行数据串化时选用的是内嵌时钟,这样可有用地处理因为时钟与数据的不严厉同步而限制高速传输的瓶颈问题。此处的硬件电路规划如图4所示。

图4 并串转化硬件示意图

体系软件规划

体系软件首要是对体系操控中心的FPGA的编程。整个程序根据模块化、结构化的软件开发思维编写。所用的开发工具是Altera公司出品的FPGA集成开发环境QuartusII,开发言语选用当今比较盛行的大规模集成电路Verilog开发言语。

体系软件功用完结了A/D操控模块、语音编码操控模块、并串转化操控模块、串并转化操控模块、D/A操控模块、语音解码操控模块和反向数据的收发操控模块。

1、A/D操控模块

A/D操控模块以FPGA为主控中心,为AD9280供给采样时钟;一起收集AD9280A/D转化后的数字量。

FPGA体系时钟频率为32MHz,关于AD9280的采样时钟为16MHz,对体系时钟进行二分频后供给给AD9280。一起,在分频后的输出时钟的上升沿对A/D转化的成果进行读取,读取的成果存入FPGA中进行下一步使用。程序如下所示。

module AdControl(clk_in,reset,ad_data,clk_out,data_reg);

input clk_in,reset;

input [0:7]ad_data;

output clk_out;

output [0:7]data_reg;

reg [0:7]data_reg;

reg clk_out;

always@(posedge clk_in)

begin

if(reset)

clk_out《=0;

else

clk_out《=~clk_out;

end

always@(posedge clk_out)

begin

data_reg《=ad_data;

end

endmodule

其间,clk_in为FPGA体系输入时钟;clk_out为分频后供给给ADC的采样时钟;reset为复位端,高电平复位;ad_data是A/D转化后得到的数字量;data_reg

用来存储A/D转化后的数字量。

2、语音编码操控模块

语音编码操控模块首要完结对PCM编码芯片供给数据编码时钟、数据使能操控以及编码后的数据接纳。

此处程序如下所示。

module PcmControl(clk_in,reset,tdd,tdc,tde,pcm_data);

……

always@(posedge clk_in)

begin

if(reset)

begintdc《=0; end

elsebegin

if(cnt0==7)

begin

tdc《=~tdc;

cnt0《=0;

end

else

cnt0《=cnt0+1;

end

end

always@(posedge tdc)

begin

if(cnt1==140)

begin

tde《=~tde;

cnt1《=0;

end

else

cnt1《=cnt1+1;

end

always@(posedge tdc)

begin

pcm_data《=tdd;

end

endmodule

其间,clk_in是FPGA体系时钟,reset为体系复位信号。信号tdd是PCM编码芯片的输出;信号pcm_data用来寄存PCM编码数据;信号tdc是PCM编码时钟信号;信号tde是PCM编码使能时钟。

3、并串转化操控模块

体系主控中心FPGA对数字化的视频、语音信号进行时分复用后,将视频语音混合信号送给并串转化器。并串转化模块首要完结对并串转化器的时序操控,使能操控和数据输入操控。此处的部分程序如下所示。

moduleSnControl (clk_in,fpga_data,sn_clk,sn_data,sncontrol);

input clk_in;

input [0:9]fpga_data;

output [0:9]sn_data;

output sn_clk,sncontrol;

reg sn_clk,sncontrol;

reg [0:9]sn_data;

always@(posedge clk_in)

begin

sn_clk《=~sn_clk;

end

always

begin

sncontrol《=1;

end

always@(posedge sn_clk)

begin

sn_data《=fpga_data;

end

endmodule

其间,clk_in是FPGA体系时钟,信号sn_clk是并串转化器的转化时钟;信号fpga_data是FPGA对视频、语音时分复用编码后的数据;信号sn_data是并串转化器的输入数据;信号sncontrol是并串转化器的编码使能时钟。

4 D/A操控模块

D/A操控模块首要用来操控AD9708,对来自串并转化后的数据,FPGA首要进行时分化复用,然后将视频信号部分发送给AD9708,一起合作DAC的转化时钟,该时钟信号是经过并串转化器康复出来的发射端体系的发射时钟。

结语

此套数字式光端机体系,完结了各个监控点和总监控室的信号长途传输。各监控点的摄像头传回视频信号,总监控室经过485数据接口线对各个摄像头进行长途操控。长途两头之间还能够进行话音通讯。具有必定的使用价值和工程含义。

责任编辑:gt