摘要

有限脉冲响应(FIR)和无限脉冲响应(IIR)滤波器都是常用的数字信号处理算法—特别适用于音频处理运用。因而,在典型的音频体系中,处理器内核的很大一部分时刻用于FIR和IIR滤波。数字信号处理器上的片内FIR和IIR硬件加速器也别离称为FIRA和IIRA,咱们可以运用这些硬件加速器来分管FIR和IIR处理使命,让内核去履行其他处理使命。在本文中,咱们将凭借不同的运用模型以及实时测验示例来评论怎么在实践中运用这些加速器。

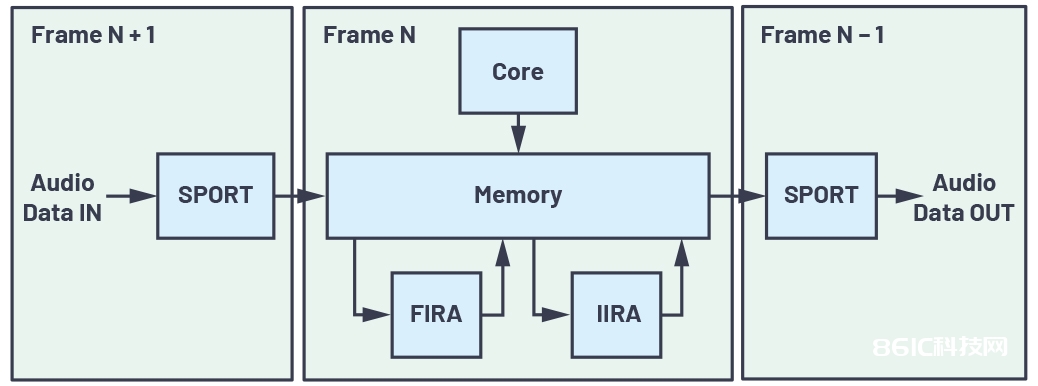

图1.FIRA和IIRA体系方框图

简介

图1显现了FIRA和IIRA的简化方框图,以及它们与其他处理器体系和资源的交互办法。

● FIRA和IIRA模块均首要包括一个核算引擎(乘累加(MAC)单元)以及一个小的本地数据和系数RAM。

● u 为开端进行FIRA/IIRA处理,内核运用通道特定信息初始化处理器存储器中的DMA传输操控块(TCB)链。然后将该TCB链的开始地址写入FIRA/IIRA链指针寄存器,随后装备FIRA/IIRA操控寄存器以发动加速器处理。一旦一切通道的装备完结,就会向内核发送一个中止,以便内核将处理后的输出用于后续操作。

● u 从理论上讲,最好的办法是将一切FIR和/或IIR使命从内核搬运给加速器,并答应内核一起履行其他操作。但在实践中,这并非一直可行,特别是当内核需求运用加速器输出进一步处理,而且没有其他独立的使命需求一起完结时。在这种情况下,咱们需求挑选适宜的加速器运用模型来到达最佳作用。.

在本文中,咱们将评论针对不同运用场景充分运用这些加速器的各种模型。

图2.典型实时音频数据流

实时运用FIRA和IIRA

图2显现了典型实时PCM音频数据流图。一帧数字化PCM音频数据经过同步串行端口(SPORT)接纳,并经过直接存储器拜访(DMA)发送至存储器。在持续接纳帧N+1时,帧N由内核和/或加速器处理,之前处理的帧(N-1)的输出经过SPORT发送至DAC进行数模转化。

加速器运用模型

如前所述,依据运用的不同,或许需求以不同的办法运用加速器,以最大极限分管FIR和/或IIR处理使命,并尽或许节约内核周期以用于其他操作。从高层次视点来看,加速器运用模型可分为三类:直接代替、拆分使命和数据流水线。

直接代替

● 内核FIR和/或IIR处理直接被加速器代替,内核只需等候加速器完结此使命。

● 此模型仅在加速器的处理速度比内核快时才有用;即,运用FIRA模块。

拆分使命

● FIR和/或IIR处理使命在内核和加速器之间分配。

● 当多个通道可并行处理时,此模型特别有用。

● 依据大略的时序预算,在内核和加速器之间分配通道总数,使二者大致可以一起完结使命。

● 如图3所示,与直接代替模型比较,此运用模型可节约更多的内核周期。