因为串行时钟同步数据传输是不杂乱而通用的,它们就被用的比较频频。运用I2C(Inte-Integrated Circuit)总线的元件首要由Philips开发,从1990年就能够运用了。这个总线立足于一根串行的双向数据引 线和一根串行的时钟引线,Pc总线的规则包含了硬件(两条引线)和软件两方面,具有数据传输格式化的意 义。每个在总线上的器材能够获得对总线的操控并能对在总线上的其他器材宣布恳求。

因为存储卡也是被同步时钟操控的,Pc总线很快就得以立足于芯片卡职业之中,很多的存储器能够在卡中 运用。下面的比如是根据SGS-ThornsON ST 24C04存储器芯片的,它有512字节的可自在读出或写人的EPROM 。对EEPROM编程的时闻组织由芯片内部处理,所以这方面不受外部操控。

I2C总线的硬件包含了在终端和卡之间的两条线,串行时钟SCL(Serial Clock)线传送时钟,其规模可达 100kHz,它发生的数据传输率高达100kb/s,对智能卡来说是比较高的,另一条线,串行数据SDA(Serial Data)线,用来双向交换卡和终端之间的数据。SDA线经一上拉电阻连接到终端的供电电源(Voc)。通讯的 两边只能把这条线下拉至地。所以送出一高电平就毫无作用,这包含发送方把它的输出转换为高阻状况(三 态),而上拉电阻把SDA线拉至供电电压电平。

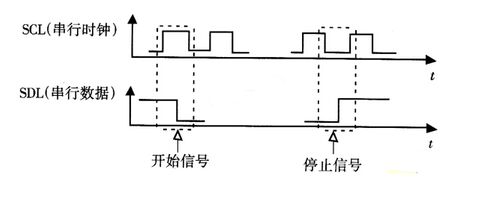

在智能卡的环境中,终端总是Pc总线为主而卡是从。数据传送总是按单字节打包,字节的最高位(第8位) 首要发送,每次在SDA线上的传送由开端信号发动并由中止信号完毕,开端信号包含了在SDA线上的下降边而 此刻在SCL线上的信号为高。相反,SDA线上的上升边而SCL线上的信号为低则指示出中止信号,参见图1。接 收方有必要使SDA线接地一个时钟周期以便对每1字节的接纳处以承认。

图1 I2C总线上的开端与中止信号

通讯开端后,第1字节的头7位为接纳方的地址。在咱们的比如中,为了简略起见,咱们假定地址的二进制 之值为1010000X。当然这或许随芯片的类型而改动,对某些存储器可在某极限内挑选改动。地址中的最终一 位(x)向接纳方指示是读出仍是写入数据,1为读出而0则是写人。

下面的比如阐明Pc总线用于智能卡时的一般功用。

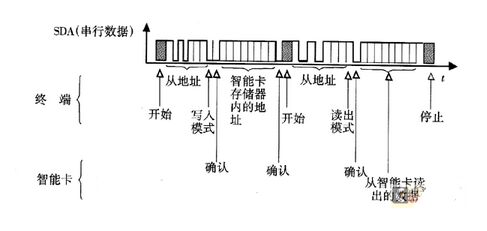

1)从一地址读出

关于从智能卡EEPROM的读出有几种类型的拜访,此处所述类型为一次读出一字节,但是,也有或许从一列 中读出几个字节,如图2所示。

图2 用I2C总线从存储器读出一个字节

读序列由开端信号发动,接着各位含有卡的地址以及规则的写操控位。这向卡标明它有必要立即把紧接的数据存储在内部缓存器中。这个缓冲器不过是EEPROM的面向字节的地址指针。卡接纳到第1字节后,它把SDA线接地一个周期以示承认。然后,终端把EEPROM地址传送给卡,再一次,卡承认收到的数据。终端所以送出一个开端信号和卡的地址以及规则的读出位。接纳到了这些,卡从指针给出的地址处取出数据送给终端。终端不需求对收到数据予以承认,它只是给卡一个中止信号,然后完毕读出一字节的序列。

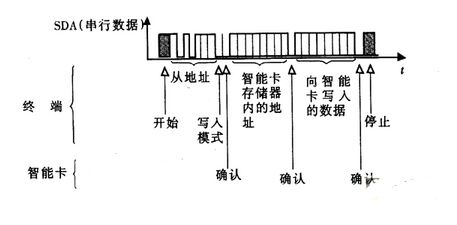

2)写人一地址

像从卡的EEPROM读出数据那样,写入数据也有不同的形式,它们中最简略的阐明如下,用它能够在存储器中的任何地方写人独自的一个字节。

再一次,序列由终端的开端信号发动,紧接着卡的地址以及规则的写人位。卡承认收到后,从终端接纳要写人数据的EEPROM的地址。

卡承认所有这些,所以接纳数据。当终端收到第3次的承认,它表明卡已接纳到了数据,便送出一个中止信号。接着,卡开端把收到的数据写人EEPROM,它不需求外部的守时信号。这样就完毕了写入序列,而此字节已存人EEPROM,如图3所示。

图3 用I2C总线向存储器写人一个字节