1、前语

单片机以其高可靠性,高性能价格比,在工业操控体系、数据收集体系、智能化仪器仪表、办公自动化等许多范畴得到极为广泛的运用。在单片机宗族的很多成员中,MSC一51系列单片机占据了宽广的商场,成为国内单片机运用范畴的干流。

可是因为8013硬件结构和指令体系的约束,当需求高速率大批量数据传送时,数据吞吐速率往往不能满意规划要求。即便选用进步振动器频率的办法,成果仍不尽善尽美,所以寻觅一种新的数据传输办法显得很有必要,这不只使人想到通用计算机的DMA数据传输技能。

2、DMA简介

DMA数据传送是由DMA操控器完结的。进行数据传输时,DMA操控器从CPU彻底接收对总线的操控,数据交换不经过CPU,而直接在内存和FO设备之间进行。DMA操控器将向内存宣布地址和操控信号,修正地址,对传送字的个数计数,而且以中止方法向CPU陈述传送操作的完毕。

DMA方法的首要长处是速度快。因为CPU不参加数据传送操作,因而就省去了CPU取指令、取数、送数等操作。在数据传送进程中,没有保存现场、康复现场之类的作业。内存地址修正、传送字个数的计数等等,也不是由软件完结,而是用硬件线路直接完结的。所以DMA方法能满意高速FO设备的要求,也有利于CPU功率的发挥。

3、规范8031数据传输与DMA数据传输比照

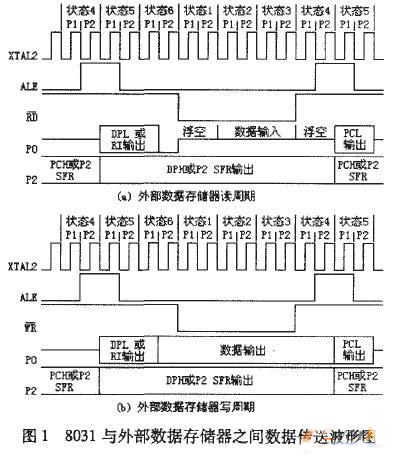

MCS一15单片机读写外部数据存储器的时序如图1所示。

在图(1)a的外部数据存储器读周期中,P2口输出外部RAM单元的高八位地址,P0口分时传送低八位地址及数据。当地址锁存信号ALE为高电平常,印口输出的地址信息有用,A比的下降沿将此地址打人外部地址锁存器,接着即口变为输人方法,读信号RD有用,选通外部RAM,相应存储单元的内容送到印口上,由CPU读人累加器。

外部数据存储器的写周期波形如图(1)b所示,其操作进程与读周期相似。写操作时,在A比下降为低电平今后,WR信号才有用,PO口上呈现的数据写人相应的RAM单元。

CPU把数据从存储器传输到FO口,需求以下进程:

·MovxA,@DPrR;从存储器读取一字节数据(24个振动周期)

·MOVX@DPrR,A;将数据写人到FO口(24个振动周期)

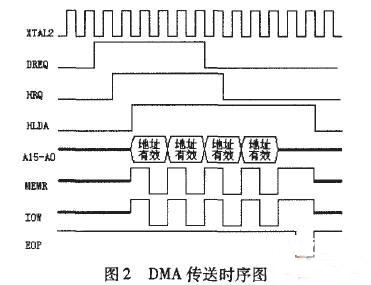

DMA操控器把数据从存储器传输到FO设备称为读传送,在这个周期里,发生存储器地址,并输出存储器读(MEMR)和10口写(row)信号。其时序如图2所示。

当数据预备好今后,设备向DMA操控器宣布DMA恳求DREQ信号,DMA操控器接到恳求后向CPU宣布总线恳求信号HRQ,CPU在现行的机器周期完毕后,宣布总线坚持信号HLDA,所以DMA操控器就接收总线,向地址总线宣布地址信号,给出存储器读和ro口写的指令,就可把存储器中的数据送到FO口上。然后修正地址指针,增或减数据宽度计数器,查看传送是否完毕,若未完毕则循环至整个数据传送完。

整个数据传送完后,DMA操控器吊销总线恳求信号HRQ,一起输出传送完毕信号EOP。CPU接收到EOP信号后,鄙人一个周期就可以从头操控总线。

从以上比照剖析可以看出,从存储器往FO口传送一字节数据,运用规范8031至少需求48个振动周期,而用DMA操控器仅需2个振动周期,功率大大高于前者,尤其是在做块传送时,效果更为明显。

4、用CPLD完结DMA传输在显现屏扫描卡上的运用

显现屏扫描卡的功用是将存储在RAM中的图画数据依照预订的显现方法进行处理,再发送到比D显现屏上。其间绝大部分时刻,CPU的作业是将处理好的数据以很高的速率发送到LED显现屏上,来确保杰出的视觉效果。

考虑到体系的简化、灵敏、高集成度,这儿挑选用CPLD完结CPU停机方法DMA读传输功用来完结数据从存储器到LED显现屏的传送作业。

整个数据传输作业分以下几个进程:①CPu预备数据;②CPU装备DMA操控器。例如数据传送首地址,传送字节数;③CPU向DMA操控器提出DMA恳求(DREQ)。因为数据预备作业是由CPU完结的,所以传送恳求也由CPU提出;④DMA接到恳求后,向CPU提出总线恳求(HRQ);⑤CPU开释总线,一起向DMA宣布总线坚持信号(HLDA);⑥DMA接收总线,进行数据传输。

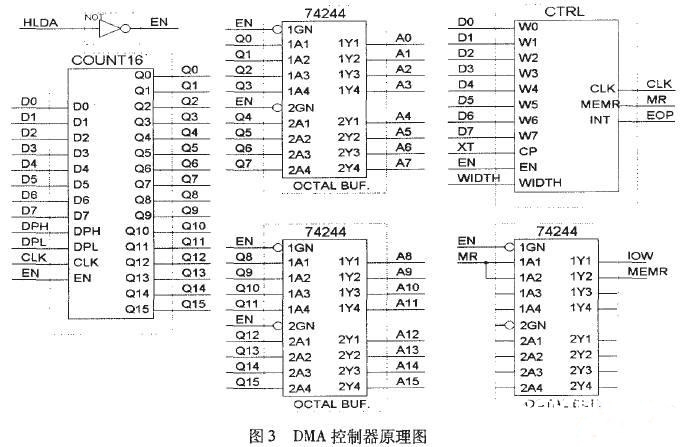

因为本体系中预备数据是由CPU完结的,也就是说CPU彻底清楚何时需求开释总线进行DMA传送,所以可将进程3、4省掉,即DREQ和HRQ信号省掉。其原理图如图3所示。

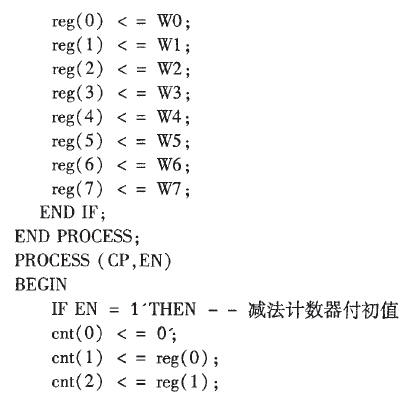

图3中,CTRL为中心操控核,它依照设定的传输字节数发生地址计数脉冲CLK,读信号MR(该信号经742科驱动后成为存储器读和FO口写信号),传输完毕信号EOP。CTRL内部界说了一个8位锁存器和一个9位减法计数器。WIDTH为置数操控端,当饥DTH为低电平常,数据总线上的传送字节数送入CTRL中,WID仪为高电平常数据锁存。EN为计数使能,为高时传送字节数送人9位减法计数器的高8位中,减法计数器的最低方位0,一起CTRL将EOP脚(传送完毕信号)置高,EN变低后,减法计数器在时钟XT下降沿效果下做减1计数,计数值减到0时CTRL中止减计数并将EOP信号置低,告诉CPU传送完毕。其操控时序如图4所示。

cTRL的vHDL程序

BEGIN

cKL=cnt(0);一地址计数脉冲输出

MEMR=NOTcnt(0);一RAM读信号输出

PROCESS(WIDTH)

BEGIN

FIiwDTH=0’THEN一置人传送字节数

图3中,COUNT16是16位加法计数器。DPH、DPL是地址高8位和低8方位数操控端,低电平有用。EN为计数使能,为低时,在由CTRL发生的脉冲效果下做加1计数。

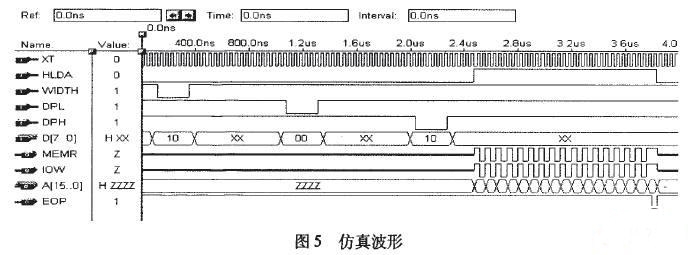

平常CPU具有地址总线的操控权,DMA操控器的地址线A15一AO、存储器读MEMR、FO口写IOW输出均为高阻。当需求做DMA数据传送时,首要CPu将传送的数据宽度、被传送数据在存储器的首地址写人DMA操控器,然后将HDLA置高,让出地址总线操控权。DMA操控器检测到HLDA变高后,cTRL依照预订的传送数据宽度,输出地址计数脉冲和数据存储器读信号MEMR,couN1T6在地址计数脉冲效果下,在首地址基础上做加1计数,输出16位地址。当数据传送完毕,EOP输出低电平,告诉CPU数据传送完毕。CPU经过查询或中止方法检测到EOP的低电平信号后,将HLDA拉低,DMA操控器接到HDLA变低的信号后将EOP信号置高,开释地址总线操控权,完毕整个DMA传送进程。图5是DMA操控器的仿真波形图。

8031操作DMA操控器的5C1程序

void DMA(unsigned int address,unsignedcha

len){

WIDTH

ADDL

=len;/*设置传送数据宽度*/

=(unsi卯edchar)address%256;/*设置传送数据首地址*/

ADDH=(unsignedchar)address/256;

EN=0;/*发动DMA传送*/

while(IN功==1);/*等候传输完毕*/

EN=1;

5、完毕语

以上所论述的仅仅DMA操控器的一种运用特例,真实的DMA操控器功用要更为强壮,但关于显现屏扫描卡来说,这些现已彻底可以完结体系要求了,而且使数据传输速率有了明显的进步。