RS-485是一种根据差分信号传送的串行通讯链路层协议。它处理了RS-232协议传输间隔太近(15m)的缺点,是工业上广泛选用的较长间隔数据通讯链路层协议。

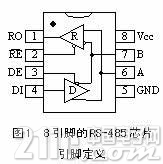

因为它运用一对双绞线传送差分信号,属半双工通讯,所以需求进行接纳和发送状况的转化。一般的8脚TTL电平到RS-485电平转化芯片的引脚界说如图1所示。

其间,引脚含义如下:

RO——接纳数据的 TTL电平输出;

——低电平有用的接纳答应;

DE——高电平有用的发送答应;

DI——发送数据的TTL电平输入;

A——485差分信号的正向端;

B——485差分信号的反向端。

在RS-485电路规划中,一般将和DE短接,用1根信号线来操控,这样能够做到收发的切换。

RS-485芯片一般处于接纳状况。当要发送数据时,由程序操控/DE 变为高电平,然后UART单元发送数据,程序要等待发送结束后,再将RS-485芯片转化到接纳状况。发送结束的标志一般由UART的特定寄存器供给状况指示,程序需求去查询。

在单片机电路中,一般用1根I/O线来操控RS-485芯片的接纳和发送状况的转化。这样需求由软件来操控 I/O引脚的电平,以到达操控RS-485收发转化的意图。

这样的操控办法形成RS-485通讯存在以下问题:

在想要发送数据和真实的能发送数据之间,存在必定的转化延时;

假如发送到接纳的转化机遇不妥,则会形成数据丢掉;

在接纳和发送数据转化期间,简单引进搅扰,使UART单元收到剩余的凌乱数据。

鉴于以上状况,笔者通过探究和参照其它相关电路,规划了一种能够完结RS-485接纳和发送零延时转化的电路,如图2所示。

当不发送数据时,TTL电平的Tx信号为高电平,经V1反向为低电平,RS-485芯片处于接纳状况。

当发送数据时,① 若Tx为低电平,经V1反向后,DE/为高电平,发送答应。此刻因为DI 接地,所以RS-485芯片的输出端A、B发生表明低电平的差分信号,低电平的Tx被送出。② 若Tx为高电平,经V1反向后,DE/为低电平,RS-485芯片的A、B端处于高阻态。此刻靠电阻R1和R2的下拉和上拉效果,使总线上发生正的差分信号,从而将Tx的高电平信号送出。

由以上剖析看出,在运用这个电路时,只需程序能确保不一起进行接纳和发送的操作,即确保是半双工传送数据,程序不用用指令操控DE/进行接纳和发送的转化。转化由硬件自身完结。

发送高电平的过程中,因为RS-485芯片处于接纳状况,此刻的发送信号有必要是在总线上其它节点发送数据时,才能将高电平信号送出。所以,仍需求软件规划中做好总线裁定。

通过在没有严峻搅扰的试验室中的试验,在运用0.5mm2屏蔽平行线时,此电路的传送间隔可达1200m。