第三章数据收集体系规划

数据收集体系是数字存储示波表的中心部分,它完结由模仿信号到数字信号的转化,即模仿信号经调度通道后进入A/D转化成数字量,再将这些数字量存入缓存器FIFO,由DSP读回进行核算处理,最终送去显现。

3.1 A/D的挑选

数字存储示波表要显现信号波形首要要对模仿信号进行采样。所谓采样便是对模仿信号进行量化的进程。而量化进程实践上存在着许多约束。首要,它要遭到量化规模的约束。因为A/D总有必定的输入量程,超出了该量程,转化成果就会呈现很大的差错。例如,信号假如超出了上限,那么A/D只能给出最大码值;反之,假如超出了下限,只能给出最小码值。这样,采样成果就会相关于模仿信号发生很大的畸变,不能有用的反映实在的信号信息。别的,A/D对量化值进行编码的位数决议了采样模仿信号的准确性。编码位数越多,对模仿信号的分辨率也就越高,采样出来的信号电压值也就更准确。在实践运用中咱们挑选的模仿/数字改换器(ADC)是ANALOG DEVICE公司的AD9288,它的根本功用描绘如下:

◆两个八位模仿/数字改换通道,100MSPS采样率/每通道

◆低功耗:90mW/每通道(100MSPS时)

◆片内供给参阅电压和采样、坚持电路

◆模仿通道:475MHz模仿带宽信噪比:SNR=47dB@41MHz

◆模仿输入规模:1Vpp/每通道

◆单电压供电(+3.0V)

◆等候形式挑选

◆两种数据输出格局

◆输出数据与拼接形式

AD9288是双通道八位单片模仿/数字转化器,具有内部的采样坚持电路,是一款低价格、低功耗、体积小易于运用的优化产品。它作业在100MSPS转化率时相同具有超卓的动态功用,而且两个通道可以彻底独立作业。

这款模仿/数字改换器只需求单3.0V电源供电(2.7V-3.6V),供给编码时钟输入方法,在大多数运用领域,不需求外接参阅电压或许是驱动器材。数字输出和TTL/CMOS兼容,而且有独立的输出供电引脚,支撑多数字逻辑电压(2.5V或3.3V)接口。编码输入是与TTL/CMOS兼容的,而且8位数字输出能在2.5V到3.3V电压规模内作业(典型值为3.0V)。用户挑选项供给联合等候形式、数据格局挑选,数据拼接形式。在等候形式下,数据输出处于高阻状况。先进的CMOS工艺使得AD9288体积超小(7mm * 7mm * 1.4mm),选用48PIN_LQFP封装。

工业制品温度规模:(-40℃—+85℃)。

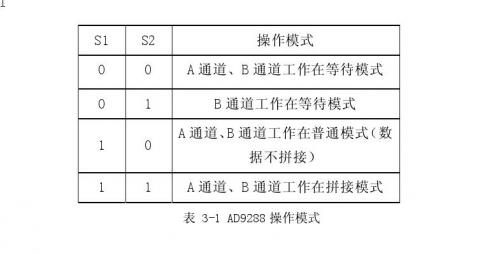

AD9288供给的S1、S2两个引脚可以用来挑选多种操作形式。操作形式如表3-1.

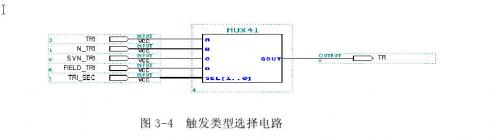

如表所示,当S1、S2都设置为1时,AD9288作业在双通道拼接形式。所谓拼接形式便是答应运用者将B通道输出数据错位半个周期。也便是说,向A、B两个通道供给相同的采样时钟(CLK_A=CLK_B),对同一信号进行采样。两通道的数据同在CLK_A上升沿有用。这样,在输出时B通道的数据就和A通道的数据相差180度相位。然后,使采样率到达了一般作业形式下的2倍。这一功用对错常有用的:假如用100MSPS的采样率对20MHz信号进行采样每个周期只能得到5个采样点,只能根本康复和再现信号波形,假如运用相同的时钟,作业在拼接形式,将一个被测信号一起送入两个通道,就可以得到10个采样点,重现波形的效果会得到很大改进。咱们在实践运用中,令其作业在一般形式下,两通道收集彼此独立,及S1=1,S2=0.其详细衔接图如图3-1所示。

3.2 FIFO的构成

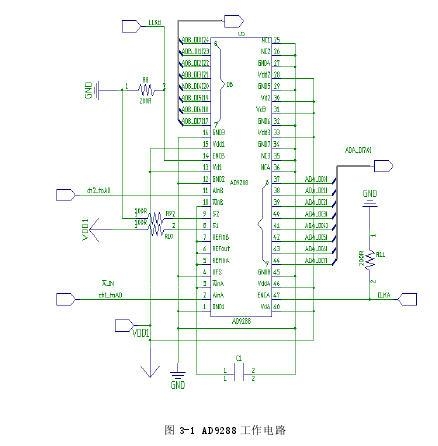

当模仿信号被A/D采样进来今后,需求有一个可以快速保存采样数据的存储器。FIFO(First In First Out)是一种先进先出(即第一个读出来的数据便是第一个写进去的数据)存储器。它没有地址线,省去了寻址时刻。别的,它还可以一起对存储空间进行读写。所以,它比一般存储器的读取速度要快许多。可以满意在高速采样时,对存储器快速读写的要求。在实践运用中,咱们没有选用现成的FIFO芯片。而是运用FPGA里边自带的5K RAM,经过MAX-PLUS II调用它宏单元库MEGA_LPM里的库文件LPM_FIFO_DC,把它设置成为两个2.5K的FIFO.因为一个LPM_FIFO_DC库文件只能完结2n个存储空间。所以,咱们调用了两个库文件(巨细别离为2 9=512和2 11=2048)串连,来完结2.5K的空间。

详细衔接如图3-2.

如图所示,一个LPM_FIFO_DC库文件有一个写使能信号wrreq,一个写时钟信号wrclock,一个读使能信号rdreq,一个读时钟信号rdclock,一个铲除端aclr,8位数据输入线和8位数据输出线;一起还有两个状况端:FIFO满信号wrfull和FIFO空信号rdempty.它的详细作业原理是:1.写FIFO时,数据首要进入0.5K的FIFO.此刻,0.5K FIFO读写使能一起有用,数据进入0.5K FIFO后,随即被写入到2K的FIFO.当2K的FIFO写满后,此FIFO模块的满信号有用,使得该模块FIFO的写使能和0.5K FIFO读使能都置为无效,写入的数据直接存入0.5K的FIFO不再搬运,直到2.5K悉数写满停止。2.读FIFO时,初始状况为0.5K FIFO读使能有用,2K FIFO读写使能一起有用。来一个读时钟就从2K FIFO读走一个最老的数据,一起,又从0.5K FIFO写进一个数据。当0.5K FIFO读空后,即0.5K FIFO的数据已悉数搬运至2K FIFO后,0.5K FIFO读空信号有用,然后,关断2K FIFO的写使能,使2K FIFO只读不写,直到一切2.5K数据悉数读空。

3.3触发

触发是由触发电路来完结的。假如没有触发电路,你在屏幕上看到的将会是具有随机起始点的许多波形凌乱堆叠的图画。而触发电路的首要效果便是确保每次拿去显现的点都是从输入信号上的一准确确认的点开端。它首要包含:触发源挑选、触发类型挑选、触发耦合方法挑选、触发释抑等。

3.3.1触发电路

1.触发源挑选

触发源一般有内触发、外触发和电源触发三种类型。触发源的挑选应根据被测信号的特点来确认,以确保被测信号波形的安稳显现。

(1)内触发:将被测信号自身作为触发源。

(2)外触发:用外接的、与被测信号有严厉同步联系的信号作为触发源,这种触发源用于比较两个信号的同步联系,或许,当被测信号不适于作触发信号时运用。

(3)电源触发:用50Hz的工频正弦信号作为触发源,适用于观测与50Hz沟通有同步联系的信号。

在实践项目中,咱们只选用了内触发和外触发两种触发源。它首要经过DSP宣布的串行码经过FPGA和D触发器来操控一个四路挑选器来完结。详细电路如图3-3.

2.触发耦合方法挑选

挑选好触发源后,为了习惯不同的触发信号频率,示波器一般设有四种触发耦合方法。

(1)“DC”直流耦合:是一种直接耦合方法,用于接入直流或缓慢改变的触发信号,或许频率较低并含有直流重量的触发信号。

(2)“AC”沟通耦合:是一种经过电容耦合的方法,有隔直效果。触发信号经一个%&&&&&%接入,用于调查从低频到较高频率的信号。

(3)“低频按捺”耦合:使触发源信号经过一个高通滤波器以按捺其低频成分。

这关于显现包含许多电源沟通噪声的信号是很有用的。

(4)“高频按捺”耦合:使触发源信号经过低通滤波器以按捺其高频重量。这意味着既使一个低频信号中包含许多高频噪声,咱们仍能使其按低频信号触发。

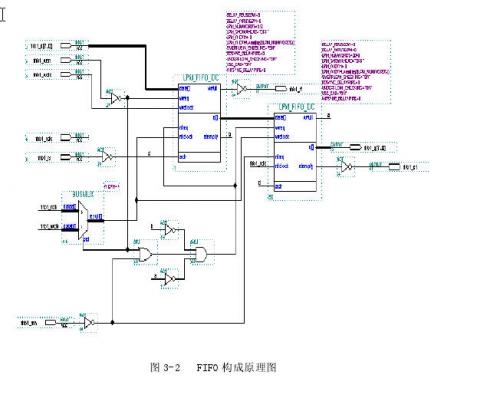

3.触发类型挑选

数字存储示波器最大的长处便是具有先进、多样的触发功用,然后使示波器的运用愈加称心如意。运用这些触发功用,示波器就能完结比曾经更多的作业。常用的触发类型有边缘触发、视频触发、脉冲触发和毛刺触发。本项目中选用了边缘触发和视频触发。其间,边缘触发分为上升沿触发和下降沿触发两种;视频触发分为行频触发和场频触发两种。这四种触发信号别离进入FPGA,经过一个四路挑选器,挑选其间之一作为体系触发信号。其详细电路如图3-4.

4.触发释抑

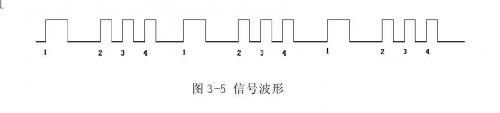

触发释抑的首要效果便是调整触发信号为一规范的周期信号,然后到达安稳显现波形的意图。例如,咱们要观测如图3-5所示的周期信号。这个信号波形一个周期内的1、2、3、4点的方位都满意触发条件。假如按一般状况,体系

就会在1、2、3、4点都发生触发信号,这样就会形成显现时波形的左右颤动。

处理这一问题的要害便是在于调理触发释抑时刻,使触发信号发生在每个信号波形周期的相同方位,即,使每次触发都发生在各周期的1、2、3或4方位,这样,信号波形才干无颤动的重现出来。

本项目中触发释抑详细完结电路如图3-6所示。由图知,这个电路包含三

个输入信号:计数使能信号PRE_TRI_FULL;计数时钟信号CNT_CLK;释抑时刻设置TRI_DELAY_DATA.一个输出信号:触发屏蔽信号Armed.它的作业原理是:刚开端时Armed为低电平,屏蔽一切触发信号。到达预触发深度后,计数使能信号PRE_TRI_FULL有用,使计数器依照计数时钟CNT_CLK开端计数。当计数到预先设置的计数值TRI_DELAY_DATA后(此计数值由DSP送过来),Armed变为高电平,敞开触发信号。