ARM 处理器一共有7 种类型的反常,按优先级从高到低摆放如下:

Reset

Data Abort

FIQ

IRQ

Prefetch Abort

SWI

Undefined instruction

Data Abort

FIQ

IRQ

Prefetch Abort

SWI

Undefined instruction

当任何一个反常产生并得到呼应时,ARM内核主动完结以下动作:

1、复制CPSR到SPSR_

2、设置恰当的CPSR位:

改动处理器状况进入ARM状况;

改动处理器形式进入相应的反常形式;

设置中止制止位制止相应中止。

3、更新LR_

4、设置PC到相应的反常向量

2、设置恰当的CPSR位:

改动处理器状况进入ARM状况;

改动处理器形式进入相应的反常形式;

设置中止制止位制止相应中止。

3、更新LR_

4、设置PC到相应的反常向量

当一个反常处理回来时,一共有3 件工作需求处理:通用寄存器的康复、状况寄存器的康复以及PC 指针的康复。

通用寄存器的康复选用一般的仓库操作指令,而PC和CPSR的康复能够通过一条指令来完结,下面是3 个比方:

MOVS pc, lr 或 SUBS pc, lr, #4 或LDMFD sp!, {pc}^

这几条指令都是一般的数据处理指令,特别之处便是把PC寄存器作为了方针寄存器,而且带了特别的后缀“S”或“^”,在特权形式下,“S”或“^”的效果便是使指令在履行时,一起完结从 SPSR 到CPSR 的复制,到达康复状况寄存器的意图。

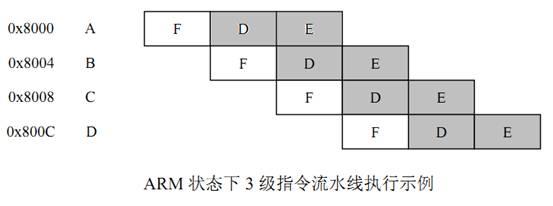

反常回来时另一个非常重要的问题是回来地址的确认,在前面曾说到进入反常时处理器会有一个保存LR 的动作,可是该保存值并不一定是正确的回来地址,下面以一个简略的指令履行流水状况图来对此加以阐明。

咱们知道在ARM 架构里,PC值指向当时履行指令的地址加8处,也便是说, 当履行指令A(地址0x8000)时,PC 等于指令C 的地址(0x8008)。假设指令A 是“BL”指令,则当履行该指令时,会把PC(=0x8008)保存到LR 寄存器里边,可是接下去处理器会立刻对LR 进行一个主动的调整动作:LR=LR-0x4。这样,终究保存在 LR 里边的是 B 指令的地址,所以当从 BL 回来时,LR 里边正好是正确的回来地址。相同的调整机制在所有LR主动保存操作中都存在,比方进入中止呼应时,处理器所做的LR 保存中,也进行了一次主动调整,而且调整动作都是LR=LR-0x4。

下面,咱们对不同类型的反常的回来地址顺次进行阐明:

假设在指令A 处(地址0x8000)产生了反常,进入反常呼应后,LR 上通过调整保存的地址值应该是B 的地址0x8004。

1、 假如产生的是软件中止,即A 是“SWI”指令

反常是由指令自身引起的,从 SWI 中止回来后下一条履行指令便是B,正好是LR 寄存器保存的地址, 所以只需直接把LR 康复给PC。

MOVS pc, lr

2、 产生的是Undefined instruction反常

反常是由指令自身引起的,从反常回来后下一条履行指令便是B,正好是LR 寄存器保存的地址, 所以只需直接把LR 康复给PC。

MOVS pc, lr

3、 产生的是IRQ或FIQ中止

由于指令不可能被中止打断,所以A指令履行完今后才干呼应中止,此刻PC已更新,指向指令D的地址(地址0x800C),LR 上通过调整保存的地址值是C 的地址0x8008。中止回来后应该履行B指令,所以回来操作是:

SUBS pc, lr, #4

4、 产生的是Prefetch Abort反常

该反常并不是处理器企图从一个不合法地址取指令时触发,取出的指令仅仅被标记为不合法,按正常处理流程放在流水线上,在履行阶段触发Prefetch Abort反常,此刻LR 上通过调整保存的地址值是B 的地址0x8004。反常回来应该回来到A指令,测验从头取指令,所以回来操作是:

SUBS pc, lr, #4

5、 产生的是“Data Abort”

CPU拜访存储器时触发该反常,此刻PC指向指令D的地址(地址0x800C),LR 上通过调整保存的地址值是C 的地址0x8008。反常回来后,应回到指令A,测验从头操作存储器,所以回来操作是:

SUBS pc, lr, #8