航空电子图画处理体系为操作者供给各种图画及字符信息,跟着传感器、显现器的性能指标不断进步,图画处理体系的规划面对越来越大的应战,其间图画缩放的功用是图画处理体系的关键技能要求。图画缩放功用有两种完成计划:1)软件完成,其长处是算法挑选灵活多样,生成的画面质量较高,缺陷是运算时刻长。2)硬件完成,其长处是分辨率高,实时性强,缺陷是不易完成功用强大的优异算法。

近年来,FPGA技能发展迅速,片内集成了PLL、硬件乘法器、存储器,具有了完成优异算法的足够资源。许多航空电子嵌入式图画处理体系是由固定的视频源和显现设备组成,体系中图画缩放的倍率是固定的。文中针对此打开要点研讨,依据FPGA硬件,完成固定倍率的图画缩放。

1 图画缩放的算法

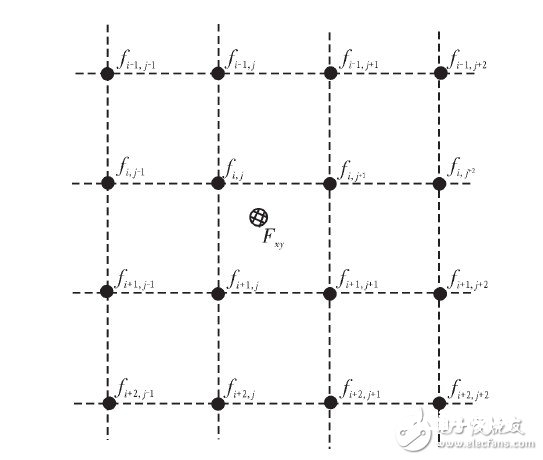

数字图画的缩放是一个处理2维离散信号的进程。输出图画中任一个像素F(x,y),均可以在输入图画f(x,y)的像素矩阵中找到其对应的方位,如图1所示。

图1 输入和输出图画像素的映射联系

F(x,y)的值可以对其邻域的原始图画进行二维卷积运算得到。

其间mxn为邻域规模,f(i,j)是输入原始图画,s(i,j)为系数函数。

因为图画中附近的像素存在着相关性,所以输出图画像素可以依据其在原始输入图画映射方位邻域的像素数据卷积得到。邻域规模内各个像素的相关度由系数函数决议,邻域的规模决议了算法的运算速度。

依据FPGA硬件完成固定倍率的图画缩放,为了下降FPGA规划的复杂性,进步图画缩放算法的运算速度,增强体系的实时性,将2维卷积运算分解成2次1维卷积运算,对输入原始图画像素先进行行方向的卷积,再进队伍方向的卷积,然后得到输出图画像素。

2 图画缩放的FPGA完成

2.1 依据FPGA完成图画缩放的功用结构

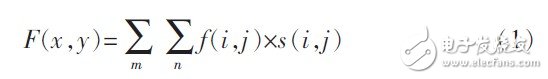

依据FPGA完成图画缩放的功用结构图如图2所示。

图2 功用结构图

卷积核算模块的硬件结构由算法决议,每个点时钟周期内,对输入原始图画像素和系数先进行行方向的卷积,再进队伍方向的卷积,然后得到输出图画像素。系数发生功用是依据操控模块确认的状况,发生算法要求的系数。输入缓存由操控模块不断改写,保证每一时钟输入给卷积核算模块相应的像素数据。输出缓存供给下一环节数据流接口。

操控模块是中心逻辑部分,可以选用逆向映射办法(依照输出像素的时刻次序递加,挑选对应的输入像素得到成果),也可以选用顺向映射办法(直接在输入像素的时序中发生输出像素)。

逆向映射办法作业在输出图画的时钟域,操控模块依据缩放倍率、分辨率和同步信号,确认输入像素坐标的增量巨细,使得在每一时钟周期输入缓存中呈现相应的像素数据。因为逆向映射办法需求使输出时钟域与输入时钟域坚持同步,所以需求大容量的输入数据存储空间,才干保证在每个时钟周期供给相应的输入像素数据。顺向映射办法输入和输出像素有很强的时序对应联系,依照输入像素的时序进程实时确认输出像素的时序,输出图画分辨率发生变化,但帧频共同。图画缩放进程中,输入一个像素可能会输出2个或3个像素,操控模块可以选用输出缓存、双口RAM、改换时钟域、添加数据总线宽度等办法到达这种同步。顺向映射办法契合输入图画的时序,不需求大容量的数据存储空间,详细依据图画缩放算法的邻域巨细而定。

2.2 依据FPGA完成图画缩放的办法

依据FPGA完成图画缩放时,无论是逆向映射办法仍是顺向映射办法,操控模块的规划都比较复杂。为了发挥FPGA的优势,大幅度下降规划难度,简化硬件结构,文中把图画缩放进程规划为一个单元体的循环进程,在单元体内部,可以事前核算出卷积系数。例如,把每行720个像素,扩大到768个像素,相当于每输入15个像素,输出16个像素。此刻可以把15个像素作为一个单元体,事前核算出每个输入像素周期的卷积系数,在FPGA中规划一个包括15种状况的状况机即可。单元体的像素数量越少,事前核算卷积系数和状况机规划的作业量就越少,因而像素的数量操控在20个以内,必要时可以选用近似的整数比。当输出像素的数量与实践要求相差很小时,图画边际部分添加或削减几个像素对显现作用影响甚微,因而各种图画缩放倍率状况下,相应个数的输入像素都可以作为一个适宜的单元体。

为论说便利,文中以将768×576的输入图画扩大到1 024×768为例,阐明依据FPGA完成对输入原始图画像素先进行行方向的卷积,再进队伍方向的卷积,然后得到输出图画像素。

2.2.1 依据FPGA完成行方向的卷积

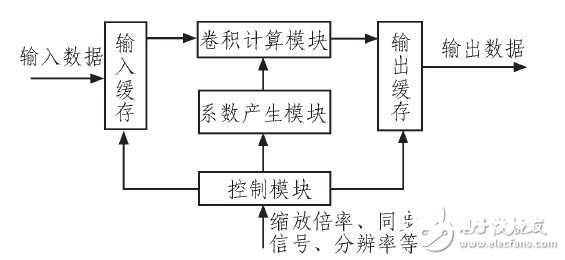

图画内行方向的扩大份额为3:4,即单元体为3个输入像素和4个输出像素,如图3所示。

图3 单元体示意图

输入图画的AB空间中均匀分布X1、X2、X3,3个像素,扩大后输出图画的这个空间将输出y0、y1、y2、y3,4个像素。这个单元体的时序联系是:当输入X1像素时,输出Y0像素;当输入X2像素时,输出Y1像素;当输入X3像素时,输出Y2和Y3像素。行方向的卷积公式为:

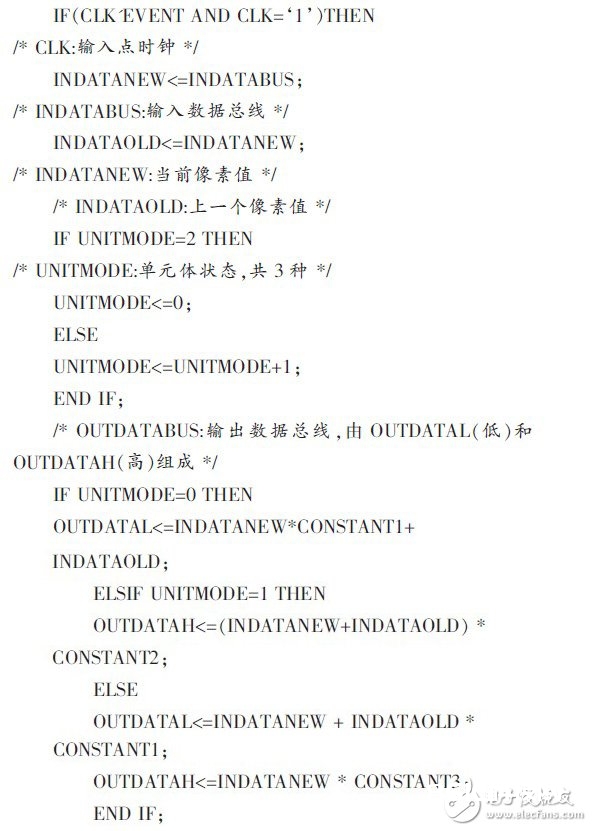

依据FPGA完成的源程序如下:

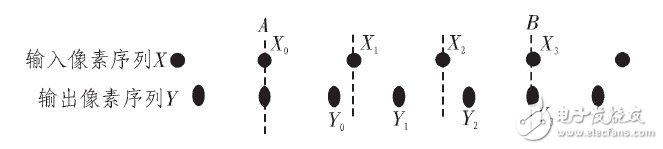

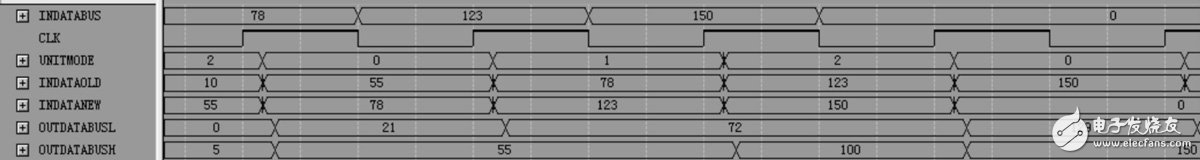

依据FPGA完成的仿真时序图如图4所示。

图4 时序图

在本例中时钟为输入的点时钟,为了在X3像素周期时输出2个像素:Y2和Y3,选用了扩大数据总线的办法。

2.2.2 依据FPGA完成列方向的卷积

数据流内行方向扩大后写入双口RAM,然后从另一侧端口读出进队伍方向的扩大。因为行方向的卷积算法,双口RAM中至少应存储接连的3行输入图画像素数据,其间2行输入图画像素数据处于被读出状况,发生扩大后的输出图画像素,另一行空间被写入当时的输入图画像素数据,循环改写。

列方向的单元体和行方向相同,也由3个输入像素和4个输出像素组成,每种状况下也是相同的卷积系数,仅仅图画横向的空间改换成图画竖向的空间,因而依据FPGA完成列方向的卷积的办法与依据FPGA完成行方向的卷积的办法相同,此处不再赘述。

3 结束语

依据FPGA完成图画缩放,需求依据图画缩放的倍率确认包括恰当数量像素的单元体。在单元体内部,依据图画缩放算法确认每个输出像素的核算公式和卷积系数,确认完成点时钟倍频作用的硬件计划。顺向映射办法输入和输出处于帧同步状况,因为输出像素数量多于输入像素,输出像素的点时钟频率要高于输入像素。本文行方向的扩大进程,点时钟频率均匀添加1/3倍,列方向的扩大进程,点时钟频率还要持续添加1/3倍。完成倍频作用可以选用更高频的独立时钟,或许倍频输入点时钟,再或许添加数据总线宽度。为节约数据存储空间,当对图画扩大时,先进队伍方向的扩大,后进行行方向的扩大;当对图画缩小时,先进行行方向的缩小,后进队伍方向的缩小。

依据FPGA完成图画缩放功用实时性强、分瓣率高。许多航空电子嵌入式图画处理体系是由固定的视频源和显现设备组成,体系中图画缩放的倍率是固定的。本文依据FPGA硬件完成固定倍率的图画缩放,可以大幅度下降规划难度,削减作业量。

依据FPGA硬件完成固定倍率的图画缩放的办法现已使用于某款航空电子产品中,电路板的原有硬件没有变化,对电路板中FPGA从头进行了规划,添加了新的内容,使用作用杰出。