长期以来,Achronix为不同行业的数据密集型和高带宽应用提供了创新性的FPGA产品和技术,并帮助客户不断打破性能极限。其中一些应用需要与先进的模拟/数字转换器(ADC)和数字/模拟转换器(DAC)进行对接——可由JESD204C完美地完成这项任务。

JESD204B/C是由JEDEC定义和开发的高速数据转换器串行接口标准。该标准减少了高速数据转换器和其他高性能器件(如Achronix Speedster7t FPGA)之间的数据输入和输出数量。这种数字和模拟信号链的组合使设计人员能够获得简化的小尺寸电路板布局,同时不会对终端系统的性能产生不利影响,从而使设计人员受益。通过高速通用I/O(GPIO)或SerDes通道来实现数据转换器件之间的接口/互连。

Achronix在其Speedster7t FPGA器件上已经实现了JESD204C接口,使客户能够使用他们所选择的ADC或DAC。由于是在同构FPGA架构上实现了软的JESD204C接口,客户可以使用他们喜欢的ADC/DAC器件并使其设计实现定制化。本文讨论了基于Achronix Speedster7t FPGA器件的JESD204C解决方案。

Achronix JESD204C解决方案支持该标准提及的所有功能,并对以前的版本进行改善。旨在实现由标准机构提出的所有的四个目标:

提高通道速率以支持所需的更高总带宽——Achronix的解决方案目前支持每SerDes通道高达24.75 Gbps的数据速率。SerDes可以支持32 Gbps的JESD204C上限通道速率。用于测试设计的数据转换器使用的是Analog Devices(ADI)的AD9082,它支持的最大数据速率为24.75 Gbps。

提升有效载荷传输效率——Achronix的用户可以使用FPGA逻辑来对其设计进行定制和优化。

链路稳健性——Achronix的解决方案展示了在单通道和多通道模式链路的高度稳健性,同时保持确定性的延迟。例如,对于那些没有量化效应的模式,采样率可以达到AD9082支持的最高极限。

向后兼容先前的JESD204B版本——Achronix将会提供JESD204B解决方案。

实验室测试方案

Achronix已成功实现并演示了Speedster7t JESD204C的解决方案,该解决方案可连ADI的AD9082,AD9082带有四通道16位DAC和双通道12位ADC转换件。实验环回设置(如图1所示)包括以下组件:

Bittware的VectorPath S7t-VG6加速卡。板上使用的是Achronix Speedster7t FPGA器件。

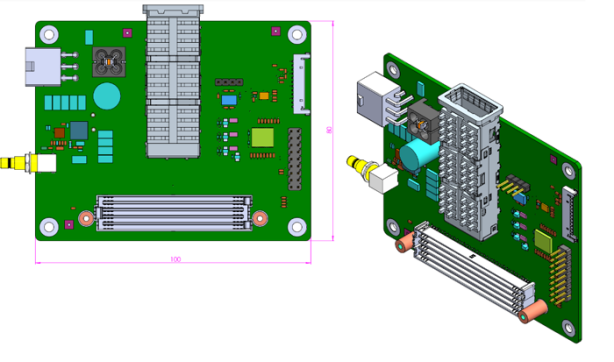

连接VectorPath和ADI的EVAL-AD9082连接器。Achronix开发了一块4-lane的QSFP到FMC的连接器,如果有需要的话,还可以调整为8通道或16通道。

配备FMC连接器的ADI EVAL-AD9082 ADC/DAC板卡。

所需的测试设备和其它配件。

图1:连接VectorPath和ADI的EVAL-AD9082连接器板卡

实验设置给发送(Tx)的和接收(Rx)的方向上提供完整的信号链。各组件的功能如下:

在VectorPath加速卡上的Speedster7t AC7t1500 FPGA器件中实现JESD204C发送/接收IP功能。通过连接的PC上的Linux控制台运行特定的测试脚本。

Speedster7t SerDes通道通过定制的FMC-QSFP连接器板卡连接到ADC/DAC。QSFP28模块支持四个SerDes通道,每个通道的运行速度为24.75 Gbps。

通过所连PC调用API,完成对ADI的AD9082-FMCA-EBZ评估板上数千个寄存器进行编程配置。另外,也可以使用FPGA上的软CPU核或SoC中的硬CPU核对寄存器进行编程配置。

外部时钟源使VectorPath加速卡和AD9082-FMCA-EBZ评估板同步。也可以通过使用AD9082-FMCA-EBZ上的振荡器来生成内部时钟,并通过FMC-QSFP连接器馈送到VectorPath加速卡。

由一个任意波形发生器(AWG)产生波形被通过外部直传送给ADC0和ADC1。

环回发生在Speedster7t FPGA内部,处于JESD204C接收和发送模块之间,而DAC输出显示在示波器上。

DAC0和DAC1输出的预期波形显示在连接的示波器上。

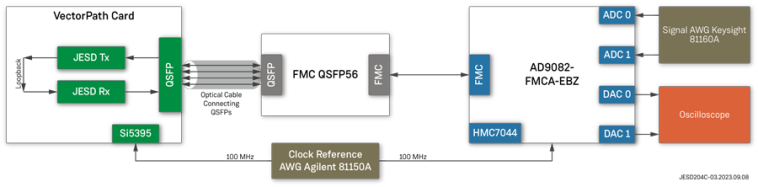

图2:四通道环回示例

上图显示了一个四通道环回配置。信号路径为AWG(I/Q信号)→AD9082-FMCA-EBZ(ADC)→FMC QSFP56→Speedster7t JESD204C Rx→环回→Speedster7t JESD204C Tx→FMC QSFP56→AD9082-FMCA-EBZ (DAC)→示波器。

AD9082-FMCA-EBZ的ADC0和ADC1的输入I/Q波形具有相同的频率,但相位相差90度。频率取决于AD9082-FMCA-EBZ支持的模式,该设置可以在最小且可接受的抖动下,实现该特定模式所声明的最高频率。

基于Speedster7t FPGA器件,实现的先进的Achronix JESD204C解决方案,可以实现JESD204C数据转换器所支持的最高速率。该解决方案为连接的ADC/DAC设备提供了一个与供应商无关的接口,从而支持客户可以选择他们喜欢的ADC/DAC供应商。