在 20 世纪 80 年代,现场可编程门阵列 (FPGA) 的早期,半导体技术的局限性意味着器件小巧简单。这些早期的 FPGA 仅具有数百个逻辑门,用于将以前在多个分立逻辑组件中实现的功能集成到单个可编程芯片中。随着设计工程师认识到 FPGA 能够减少元件数量、节省电路板空间和简化电路板布局所带来的价值,FPGA 市场迅速增长。

半导体技术的进步意味着 FPGA 自 20 世纪 80 年代以来已经发生了转变,成为我们今天所知的大型复杂器件:在高端市场,FPGA 具有数百万个门、支持高于 30 Gbps 数据传输速率的超高速接口,以及实现嵌入式处理器、PLL、功能性 SRAM 存储器等的多个硬连线 IP 块。

高端 FPGA 是数据处理、成像和高带宽通信设备等应用的主要解决方案,吸引了最多的关注,并占据了行业营销和促销资金的最大份额。但请记住,小型 FPGA 最初发挥的作用仍然具有价值,例如:

· 胶合逻辑集成

· 简单计数器或 PWM

· 基本状态机

· 控制逻辑

· I/O 和接口桥接

· I/O 扩展器

· 多个传感器输入的聚合

· 电压监测

小型、低成本和低端 FGPA 的活跃市场支持这些功能及其他功能。它对 OEM 厂商的重要性体现在最近 FPGA 市场的新进入者瑞萨的到来。

然而,对于 FPGA 在主流工业和消费电子设备中的适用性,人们的看法仍然存在分歧。熟悉微控制器的设计工程师通常将 FPGA 视为一个陌生的概念:昂贵、耗电且难以使用。

Xilinx(现在是 AMD 的一部分)和英特尔提供的高端 FPGA 可能是如此。莱迪思半导体、Microchip 和瑞萨提供的低端 FPGA并非如此。事实上,与 MCU 相比,FPGA 的使用在许多功能上具有几个重要优势。

在 MCU 中,任务是在软件中按顺序执行的。在 FPGA 中,任务在硬件中并行执行。因此 FPGA 操作具有有吸引力的特性:高度确定性的性能、低延迟、定制硬件的灵活性以及极低的功耗。

本文介绍了 FPGA 的基本操作,以及 FPGA 制造商提供的设计工具如何使电子系统设计中的 FPGA 实施变得简单且可预测。

FPGA 的基本架构

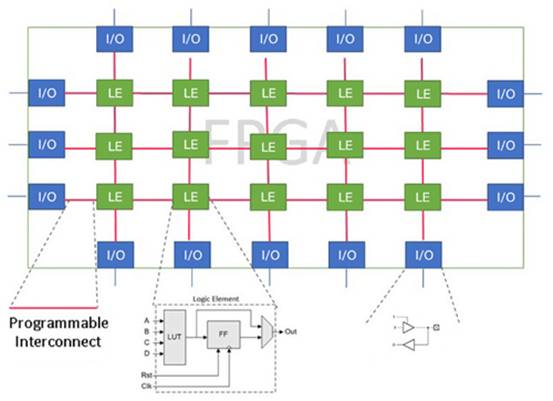

FPGA 由三个基本元件组成,如图 1 所示:

· 可编程逻辑元件 (LE)

· 可编程路由互连

· 可配置的 I/O,提供与外部世界的通信

图 1:FPGA 提供高度可编程的硬件结构

逻辑元件由可配置查找表(LUT)和顺序元件(SE)组成。LUT 可以配置成任何类型的组合逻辑,例如 OR、AND 或 XOR。SE 通常配置成简单的触发器。

· LE 是FPGA 的基本功能块,这也是每个FPGA 根据其包含的LE 数量进行分类的原因。FPGA市场的低端产品涵盖了几百个LE到10,000个LE之间的FPGA

· 可编程互连将配置的 LE 连接在一起,以实现应用所需的功能

· I/O也是可编程的,并且可以配置为支持任何 I/O 接口标准

实现这些元素的底层硬件是大量的可编程开关。在大多数 FPGA 中,每次 FPGA 上电时,这些开关都会重新编程。这需要将编程文件存储在配置存储器中:该存储器可以位于 FPGA 芯片内部,也可以位于外部。

Microchip FPGA 是这一规则的例外:它们的可编程开关采用类似于非易失性闪存的技术制成。 它们可以直接编程,不需要编程文件或配置存储器。

如何配置FPGA硬件

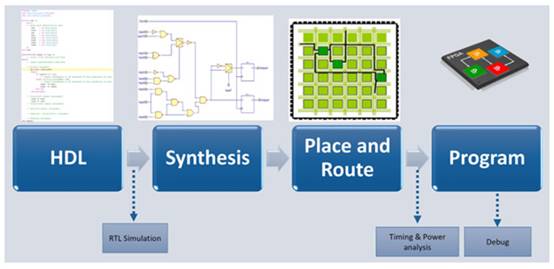

所有 FPGA 制造商都提供自己的设计工具来生成此编程文件,通常称为比特流。每个制造商的工具基本上都与其他制造商相似。这些工具提供以下功能:

· 使用标准硬件描述语言 (HDL)(VHDL 或 Verilog)进行功能描述

· 程序综合

· 布局布线

· 编程文件生成

图 2:FPGA 设计流程由每个 FPGA 制造商为其器件提供的工具提供支持

时序分析是设计流程的一部分,用于检查影响信号通过路由结构传输的传播延迟是否与应用的性能要求一致,如图 2 所示。仿真和验证HDL工具生成的代码也很重要,以验证编程到FPGA中的功能是否按照设计规范运行。

在整个FPGA开发过程中,没有什么比时序分析和RTL仿真的实现更困难了,而且它们也不是特别复杂。所有其他阶段均由设计工具自动执行,只需几分钟即可在标准笔记本电脑上执行。

每个FPGA制造商都提供自己的工具集;它们之间的主要区别在于图形用户界面。只要源代码是使用标准 VHDL 或 Verilog 描述语言编写的,就可以轻松地从一种语言迁移到另一种语言。FPGA 用户通常可以通过免许可证使用这些工具。FPGA 评估板很容易以低成本获得。因此,对于想要开始尝试低端 FPGA 的工程师来说,工具和资源的成本并不是障碍。

低端FPGA产品的多种选择

低端 FPGA 市场由三个制造商提供服务:Microchip、莱迪思和最近加入的瑞萨。

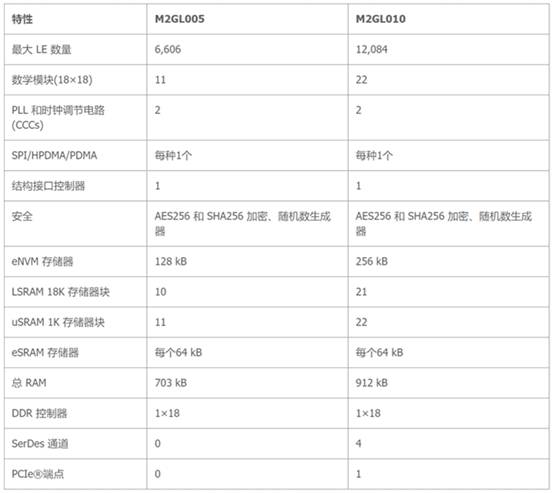

Microchip的产品组合主要面向中端 FPGA 市场。然而,IGLOO® 2 闪存 FPGA 系列中的入门级器件确实算作低端 FPGA,如图 3 所示。

图 3:Microchip IGLOO 2 FPGA 产品系列中低端器件的主要特性

Microchip 提供 Libero SoC 工具,用于 IGLOO 2 FPGA 的开发。可为最多 25,000 个 LE 的器件提供免许可证。IGLOO 2 FPGA 以其众多的存储器选项而著称,包括功能嵌入式非易失性存储器以及高速接口。

莱迪思长期以来一直坚持支持低门密度FPGA市场的政策,并拥有基于两个系列的强大产品:XO2/XO3和iCE40。

XO2/XO3 系列基于易失性技术,它在与 FPGA 矩阵相同的芯片上提供配置存储器,为设计人员提供单芯片 FPGA 解决方案,无需外部配置存储器。

XO2/XO3 器件提供多种密度选项,从 256 个 LE 到最多 10,000 个 LE。它们的主要特点是:

· 凭借片上非易失性配置存储器,几乎可以即时启动操作

· 单电压和低功耗选项

· 硬连线 I2C 和串行外设接口、PLL、闪存和内部振荡器

· 莱迪思提供免许可证的 XO2/XO3 的 Diamond 设计工具。

莱迪思的另一个低端 FPGA 系列 iCE40 系列分为几个子系列:iCE40LP、iCE40UL、iCE5LP、iCE40UP、iCE40LM 和 iCE40HX。该系列涵盖从 384 个 LE 到 8,000 个 LE 的范围。在 iCE40 系列中,莱迪思针对低功耗和小尺寸优化了功耗/尺寸/性能的权衡:具有低于 100 µA的市场最低的静态电流。iCE40 还采用 FPGA 业界最小的封装,尺寸仅为 1.4 mm x 1.4 mm。

瑞萨是第三个低端 FPGA 制造商,是最近进入该市场的公司。瑞萨以其 GreenPAK™ 可编程混合信号产品技术而闻名。现在,新的 FPGA 产品对该技术进行了补充。

ForgeFPGA™ 系列提供相对少量的可编程逻辑,可以快速有效地设计到成本敏感型应用中。与其他替代方案(包括非 FPGA 设计)相比,ForgeFPGA 器件可显著节省成本。瑞萨为其 FPGA 提供免许可证的 GoConfigure™ 设计软件中心。

瑞萨的 ForgeFPGA 器件系列具有 1,000 个 LE 至 4,000 个 LE,预计将于 2024 年提供样片和量产。

低端 FPGA:非专业人士的便捷选择

FPGA 被广泛认为是一种高端、高成本、难以使用的高端应用产品。

事实上,低端FPGA恰恰相反。因此,富昌电子提出了一种关于 FPGA 的新方法,以认识到它们在普通工业和消费应用中的优势,例如机器人手臂的多电机控制、工厂设备的监控/警报管理、电动汽车充电器的逆变器、电池管理系统、智能建筑和智能城市应用中的传感器信号处理等。

这些确定性低功耗设备的使用范围非常广泛。首次探索低端 FPGA 的微控制器开发人员会发现,他们可以从中获益匪浅。

评估套件:适用于 IGLOO2 FPGA 的 M2GL-EVAL-KIT

支持的元器件:M2GL010T-1FGG484

IGLOO2 评估套件可以更轻松地开发基于 IGLOO2 FPGA 的电机控制、系统管理、工业自动化或高速串行 I/O 应用的嵌入式设备。这些 FPGA 以其强大的功能集成、低功耗、卓越的可靠性和经验证的安全性而闻名。

IGLOO2 评估套件提供了一个平台,用于为基于 PCI Express 和千兆位以太网的系统开发基于收发器 I/O 的 FPGA 设计。该板符合小型 PCIe 外形,能够使用任何带有 PCIe 插槽的台式电脑或笔记本电脑进行快速原型设计和评估。

该套件使开发人员能够:

· 开发和测试 PCI Express Gen2 x1 通道设计

· 使用全双工 SERDES SMA 对来测试 FPGA 收发器的信号质量

· 测量IGLOO2 FPGA的低功耗

· 快速创建工作的PCIe链路

该板包括一个连接 10/100/1000 以太网的 RJ45 接口、512 Mb LPDDR、64 Mb SPI 闪存、USB-UART 连接以及 I2C、SPI 和 GPIO 接头。