一。 导言

数字频率计是电子测验、自动化操控等设备中不可或缺的重要模块,对其精度和本钱都提出了较高的要求。最常用和直接的频率丈量办法是直接测频法。直接测频法作业原理简略,规划复杂度低。其通过在给定的闸口信号中对待测信号脉冲进行计数,然后算出待测信号的频率。但由于闸口是与基准信号(fr)彻底同步,而不是待测信号(ft),所以丈量成果有±1个待测信号脉冲的差错,这对低频信号是难以容忍的。多周期同步测频法中闸口的时刻不是固定的,而是被测信号的整周期倍。闸口的开闭受门控信号和待测信号的两层操控,以期到达闸口与待测信号彻底同步,然后消除±1个待测信号脉冲的差错。多周期同步测频法将差错搬运为±1个基准脉冲的差错,而基准信号的频率一般较高,其±1个脉冲差错可忽略不计。多周期同步测频法尽管处理了差错的问题,但其增加了闸口信号的规划难度,并且加剧了频率核算部分的担负。

根据此,本文提出了一种选用较小规划CPLD(Xilinx XC95144)和单片机(AT89C51)相结合的数字频率计规划计划。该计划不只体积小、保密性强,并且规划简略、本钱低、精度高、可测频带宽。

二。 数字频率计作业原理

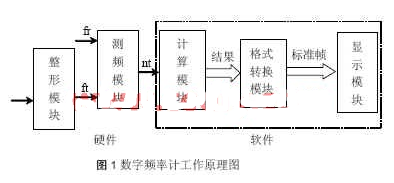

本文提出的根据CPLD和单片机相结合的规划计划不只能较好地处理差错问题,差错仅小于等于 0.1HZ,一起还通过对软硬件界面的科学区分,在确保功用的根底上,尽最大或许地简化了硬件规划的难度。该办法原理图如图1所示。其间测频模块选用CPLD(Xilinx XC95144)规划完结,其他功用主要由单片机来完结。完结的功用如下:

测频模块:主要是对基准信号fr和待测信号ft的脉冲进行计数,计数周期为1s;

数字处理模块:接纳测频模块送出的待测信号脉冲计数值nt,核算出其实践的频率值。然后选用10次求均匀的办法逐步求精待测信号频率值;

格局转化模:块担任将核算模块所得的成果转化为显现模块能够辨认的帧格局;

整形模块:担任对输入的待测信号进行整形处理(扩大、滤波);

显现模块:担任待测信号频率值的显现。

下面将对对其间心模块的规划做一介绍。

三。 数字频率计的规划

3.1 测频模块

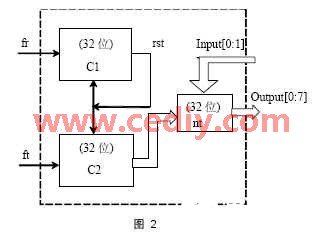

如图2所示,测频模块主要由两个计数器C1和C2组成。其作业进程如下:

C1对基准信号的脉冲进行计数,计数周期为1s;C1计数的一起,C2对待测信号的脉冲进行计数。当C1计数满1s时,门控信号rst有用,其停止C1和 C2的计数,并将C2的计数值锁存至32位寄存器nt中,然后将C1和C2计数值清零;接着rst无效,并开端下一次计数,C1计数不满1s期间rst始终保持无效。

3.2 数据处理模块

数字频率计的中心单元AT89C51,通过操控P3.0和P3.1两个端口将32位寄存器nt的4个字节输出到AT89C51的直接地址30H, 31H, 32H, 33H处。当计数器的值被读到单片机中后,通过调用数据处理模块,对计数值进行相应的处理,求出所测参数的值和单位,最终应将参数值转化为十进制数,再转化为驱动LED数码显现器的段码,包含1个小数点。对计数值的处理运算要用到除法和乘法。为了用8位单片机来处理32位数的二进制到十进制的转化,首要运用字节除法求出每个字节对应的十进制数位值。

如:a100=[30H]/100, a10=([30H] mod 100)/10,a1=[30H] mod 10

其间,a1是频率值的第一个字节的个位, a10是频率值的第一个字节的十位, a100是频率值的第一个字节的百位。

咱们将每位十进制数用非紧缩BCD码表明,别离存储在AT89C51的直接地址40H~49H。然后通过如下核算:

40H=a1+6*a2+6*a3+6*a4

41H=a10+6*a20+5*a2+6*a30+3*a3+6*a40+a4

42H=a100+6*a200+5*a20+2*a2+6*a300+3*a30+5*a3+6*a400+a40+2*a4

43H=5*a200+2*a20+3*a300+5*a30+5*a3+a400+2*a40+7*a4

44H=2*a200+5*a300+5*a30+6*a3+2*a400+7*a40+7*a4

45H=5*a300+6*a30+7*a400+7*a40+7*a4

46H=6*a300+7*a400+7*a40+6*a4

47H=7*a400+6*a40+a4

48H=6*a400+a40

49H=a400

由于本规划用非紧缩BCD码表明十进制数,40H到49H所表明的数值还要进行相应的调整,调整过程如下: 42H←42H+40H/100

40H←40H mod 100

41H←41H+40H/10

40H←40H mod 10

43H←43H+41H/100

41H←41H mod 100

42H←42H+41H/10

41H←41H mod 10

……

调整后的每位十进制数都契合非紧缩BCD码的表明标准。为了减小直接测频法的差错,本规划选用了十次均匀逐步求精的办法。由于对同一待测信号,接连两次计数值之差不会超越1,所以可拓荒一10字节的行列,初始时全为0,每次先将个位(40H)入队,然后求该行列的均匀值,将商返送40H,余数送非常位。为使显现成果尽量准确,可用相同办法填充百分位、千分位、万分位和十万分位。

3.3 格局转化模块

本规划中,将显现模块能辨认的核算成果界说为如下帧格局,即每帧由8字节(50H~57H)组成。其间50H表明丈量值的第一个有用数字;51H表明52H~56H中还有几个整数位,剩余的为小数部分;57H

表明显现单位。如12159676表明115.967 MHZ,10985435表明1.98543KHZ。

四。 试验成果

为了验证本规划计划的正确性以及先进性,咱们做了很多试验,该试验预置计数周期为10s。试验成果如下:

早年三组试验可知,本规划关于整数频率的丈量差错为0;第四组试验的差错主要是由显现位数的精度不行引起的,即本规划最多只能显现6位,其他的将舍去,其最大差错是-0.9HZ;后两组试验的差错主要是由非整数频率引起的,这是直接测频法先天决议的,通过十次求均匀可将其操控在-0.1HZ以内。

从试验成果能够看出,本计划将部分影响规划复杂度和完结本钱的功用移至软件部分来完结,在不考虑显现精度引起的差错的情况下,该计划规划的数字频率计准确度可达99.9%以上,基本上能满意大部分运用范畴的要求,且该计划具有规划本钱低价、规划简略、精度高、可测频带宽等长处,值得从事同类开发人员的学习。

本文作者立异点在于提出了一种根据CPLD和单片机相结合的规划计划。该计划以直接测频法为根底、软件补偿技能为辅佐,大大降低了规划本钱和完结复杂度,且较好地处理了差错问题。总归,论文所描绘的规划思维先进,对同类运用具有较高参考价值。

责任编辑:gt