I2S总线是一种用于音频设备间传输数据的串行总线标准,该总线选用独立的时钟线与数据线,防止了时差诱发的失真。跟着多媒体的广泛运用,该总线已被运用于越来越多的数字体系中。

PCI总线是一种高性能的32/64位部分总线,理论最大传输速率可达132 Mbit/s,可支撑多组外设,现已被各类干流处理器做为总线标示,是现在运用最广泛的外围总线。现在大部分处理器并没有集成I2S接口,但在嵌入式体系中CPU常常运用PCI总线与外围设备进行交互,故需规划一种PCI—I2S接口转化电路,然后完结CPU与外围音频设备进行通讯。现在完结此种接口转化电路首要经过PCI接口芯片与音频接口芯片等专用集成电路芯片在板级电路进行组合然后完结依据PCI的音频播映设备。此种电路尽管老练牢靠,但电路规划杂乱、灵敏性小而且需求占用很多的电路板空间。

跟着数字通讯技能的开展,因为FPGA的灵敏性与其较短的开发周期,在接口电路规划中的运用现已越来越广泛。本文提出一种运用FPGA完结PIC—I2S 的接口转化电路,不只能够防止运用协议转化芯片,节约电路板上的空间,而且还大幅加强了体系的灵敏性,便利保护晋级。

1 体系的硬件规划

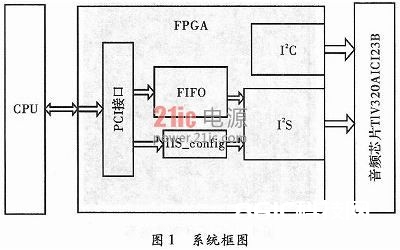

音频播映体系首要由立体声音频编解码器TLN320AIC23B,FPGA器材XC6SLX75以及处理器PowerPC8270组成。体系框图如图1所示,CPU将原始音频数据经过PCI总线传至FPGA后以每组数据16 bit的格局串行传输至音频芯片TLV320AIC23B,并由音频芯片将数字量转化为模仿音频信号输出。FPGA完结PCI接口功用和对音频编解码芯片的装备与数据传输功用,其内部首要由PCI协议接口,I2S协议接口,I2S装备存放器,I2C协议接口以及FIFO存储器等组成。

TLV320AIC23B在体系中完结数字音频信息到音频模仿量的转化,在体系上电作业时,首要需求经过I2C接口装备它的多个操控存放器,尔后芯片将依据位传输时钟(Bclk)与左右声道操控时钟(LRCIN),按操控存放器中装备的办法收集由FPGA发送来的音频数据。接收到的数据将传至芯片内部进行数模转化、滤波等处理。

FPGA依据I2S协议标准与芯片要求,由主时钟(MCLK)分频发生位传输时钟(Bclk)与左右声道操控时钟(LRCIN),与音频数据同步发送至 TLV320AIC23B。其间左右声道操控时钟(LRCIN)应与音频数据的原始采样等级频率相同,依据I2S的协议标准及芯片材料,其位传输时钟 (Bclk)与芯片的主时钟(MCLK)如下:

BCLK=Sampling Size×Sampling Rate (1)

MCLK=Sampling Size×Sampling Rate×384 (2)

式中,Sampling Rate为原始采样等级频率;SamplingSize为采样巨细。

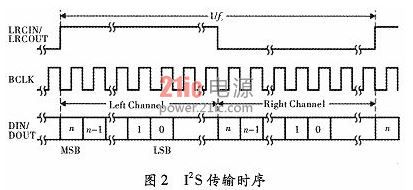

体系中,TLV320AIC23B芯片选用左对齐的接口形式,其时序如图2所示,其间LRCIN为高电平时音频的左声道选通,为低时音频的右声道选通。在 LRCIN的一个周期内,左右声道上传输同一组数据。因为PCI总线的传输速度远高于I2S总线的传输速度,为不使CPU过高频率的呼应中止,所以在 FPGA中生成一个FIFO,可使得PCI总线能够接连传入很多数据。此外,因为不同的音频文件有着不同的采样等级频率,而一般音频文件的采样频率为16 kHz或32 kHz,故在FPGA中生成I2S_config存放器,能够经过PCI总线设置此存放器以调用FPGA中不同的数字时钟办理(DCM),然后为 TLV320AIC23B芯片供给不同的时钟。

2 PCI接口规划

PCI协议比较杂乱,它不只有严厉的同步时序要求,而且需求许多的装备存放器,因而完结电路也比较杂乱。一般状况下,在FPGA中完结PCI接口一般有3 种办法:(1)用FPGA自行规划PCI接口,该办法可依据需求有挑选地完结PCI接口功用,更靠近体系需求,而且能够下降体系本钱,但需求开发者对 PCI协议有着深入的了解,且在外部环境恶劣时,不容易满意体系的安稳性要求,开发难度较大。(2)运用PCI硬核来对体系进行开发,PCI硬核便是嵌入在FPCA内部的固化电路,类似于专用的PCI接口芯片,规划者只需完结信号链接与验证即可,但此办法中,PCI硬核现已固化在FPGA中,影响了体系的灵敏性。(3)运用PCI软核进行开发,PCI软核能够依据用户本身的需求进行装备,更为灵敏,靠近用户体系,且其现已过规划厂商的验证,牢靠性高。本文选用Mentor公司供给的开源软核MPCI32用于FPGA上PCI接口的开发。

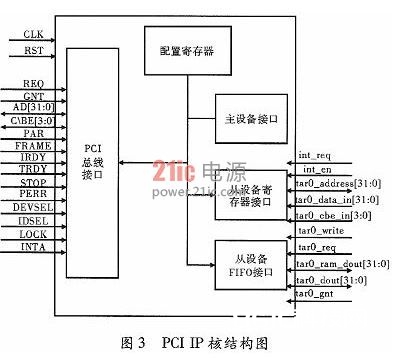

Mentor公司的PCI核完全契合PCI2.2的标准,支撑33/66 MHz、32位数据的传输,PCI核的结构如图3所示,该PCI核的功用是将进口测杂乱的PCI接口信号转为出口侧较为操作的用户信号。PCI核内用户侧设置有主操控接口和从操控接口以及装备存放器等模块,其间从操控接口分为存放器接口与FIFO接口。因为本文中仅运用了从操控接口,所以图中仅对从操控接口的信号展现。能够看出,IP核左边的信号为PCI的标准信号,在运用时与前端PCI总线衔接,右侧信号为本地数据信号,能够看出IP核将PCI上本来复用的地址线与数据线处理后别离接出为32位的地址线与32位数据线,而且本来总线上双向的数据线被区分为单向读信号线与写信号线。此外还有后端逻辑对存放器的读写地址信号线与PCI拜访逻辑的读写地址信号线,后端对存放器运用时的恳求信号线,存放器被占用的标志信号线等。装备存放器包含一切PCI装备空间的信息,其间包含标明设备信息的Device ID与Ven dor ID存放器,以及指令存放器,Base Address Register等主设备初始化时需求拜访的信息,这些信息在PCI核生成时现已被设定,无需改动。

在规划PCI接口时,用户经过建议存放器读写恳求tarO_req,去拜访后端存放器,从存放器交流数据,在CPU检测到都算逻辑未运用存放器时,可建议占用恳求并占用存放器(tarO_gnt被置位),此刻,PCI读写此存放器中的数据。

3 音频接口规划

在驱动后端的音频芯片时首要需求经过I2C接口装备音频芯片的操控存放器,尔后依据音频数据不同的采样等级频率操控FPGA发生的时钟,终究音频数据从FPGA内部的FIFO中经过FPGA发生的时钟依据I2S协议标准向音频芯片传输。在FPGA中规划的音频接口包含I2C时序协议接口模块,I2S时钟操控接口模块和I2S时序协议接口模块。

3.1 I2C接口模块的规划

I2C总线是由飞利浦公司开发的串行总线,总线由两根信号线构成,其间SCLK为时钟信号线,SDA为双向数据线。I2C总线上的一切设备均可做为主设备,每个设备在总线上都有仅有的地址。

立体声音频编解码器TLV320AIC23B中,共有11个存放器需求装备,一切存放器为只写存放器。这些存放器别离操控芯片输出音频的左右耳机音量、左右功放音量、芯片电源、采样率等参数。在芯片的装备参数传输时,以I2C的数据线(SDA)在时钟线(SCLK)为高时下降沿条件作为数据的开端位,尔后每逢FPGA向TLV320AIC23B传输8位数据时,TLV320 AIC23B在第9个时钟时经过SDA向FPGA回来一个ACK信号。假如FPGA承认收到ACK信号则持续传输下一组数据,否则将重复传输此组数据。实践中示波器丈量的传输波形如图4所示。

3.2 I2S时钟操控接口模块的规划

因为不同的音频数据有着不同的采样等级频率,所以在传输不同音频文件时,FPGA供给给TLV320AIC23B的时钟频率不同,为使不同采样频率的声音文件都能在本体系上正常播映,故在FPGA内部运用其DCM由主时钟12.288 MHz生成16 kHz和32 kHz两种采样时钟频率,接入缓冲器BUFGMUX中,而且经过在PCI的装备空间中拓荒一个存放器,存放器的值接至BUFGMUX的挑选端,这样经过装备PCI总线装备此存放器即可依据播映音频的状况挑选时钟频率。

3.3 I2S时序协议接口模块的规划

I2S时序接口模块的主时钟由FPGA内部供给,模块内经过对主时钟进行分频发生BCLK与LRCin,模块在每个LRCin的上升沿由缓存FIFO中读取一个16 bit的数据放入暂时存放器,尔后在BCLK的每个上升沿顺次由高至低读取存放器中的每一位并赋值给数据线SDIN,而且在LRCIN的下降延时重复传输此数据,然后完结音频数据的I2S协议传输。

4 体系测验及成果

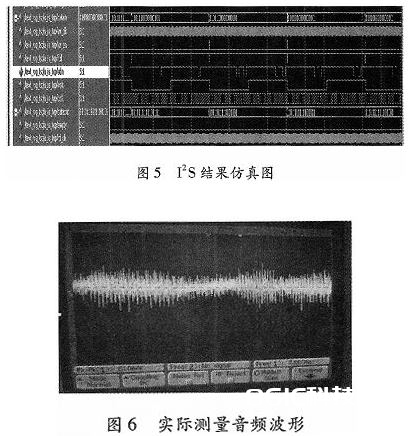

经过在上位机中向CPU内部Flash烧录一段音频数据,尔后经过拜访FPGA的装备存放器将此段数据传入至FPGA内64 kB的FIFO中,后端音频模块检测到FIFO非空即开端作业。首选经过逻辑仿真软件对体系进行仿真,成果如图5所示,信号线SDIN、 LRclk,BCLK输出成果契合I2S协议标准中左对齐形式。尔后能够在音频芯片模仿输出端接入耳机或功放等音频播映设备,用示波器丈量其模仿输出。成果证明此体系作业正常,能够依照要求播映16 kbit/s与32kbit/s WAV音频文件。经过示波器丈量的模仿输出如图6所示,能够看出显着的包络信号。经过以上定论能够看出,体系能够充分运用FPGA 片内资源,然后削减对板内面积占用并减低体系功耗,也易于移植入同类的嵌入式体系中。

在本文的基础上,能够进一步发挥FPGA的灵敏性,比如在开发FPGA上支撑PCI从设备DMA形式,以进一步加强PCI总线的读写功率、I2S总线的右对齐和DSP形式等,而且能够开发语音芯片上的语音收集功用,使体系完结语音收集、转化、传输等功用。