AD7616是一款16位、具有双采样坚持通道同步采样才能,本钱和功用经过优化的2 × 8通道模数转化器(ADC),。双采保的ADC架构使得AD7616能够对16通道中的两个模仿通道进行一起采样。

这一功用关于电力运用来讲,能够用来对一对电压和电流通道进行一起采样,以便下降这一对输入之间的相位差错。

但是,在三相电力丈量体系中,假设只要两个采保通道还不足以对六个模仿通道一起进行采样。在做三相功率核算的时分,三相电压电流的信号采样值因为非一起采样的原因会形成必定的相位视点差错而引起三相功率差错变大,并且这样的差错很难经过软件准确补偿,尤其是在谐波功率也需要被核算的时分。

运用AD7616输入通道完结准同步采样的办法,能够大大削减16个通道间因为非同步采样而引起相位差错,一起这个办法自身对绝大多数电力运用来并也不会削减幅值丈量的精度。其将16个通道之间的相位失配降至最小。这种办法在最小化通道间相位失配的一起,不会下降起伏精度功用。

伪同步采样

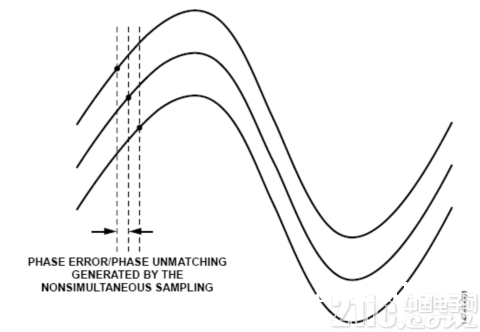

当一个复用输入非同步采样ADC循环挑选并逐个转化其输入通道时,通道之间会引进转化时刻推迟。推迟时刻取决于ADC的采样速率。从体系视点看,这种时刻推迟会在各模仿通道之间发生一个体系级相位差错或相位失配。

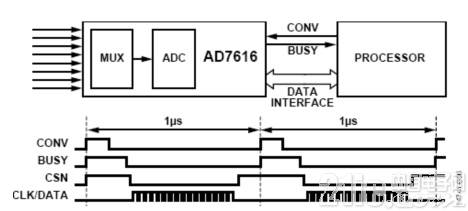

图1.非同步采样引起的相位失配

假定将同一个50 Hz正弦波信号施加于一个8通道复用ADC的输入(一切通道共用一个输入源),ADC以1 MSPS速率轮询采样各通道。当软件收到终究样本时,运用离散傅里叶变换(DFT)算法核算通道之间的相位角。理论上,榜首通道和第二通道之间的相位视点差为:

准同步采样办法运用均匀法来使相位差错最小化。

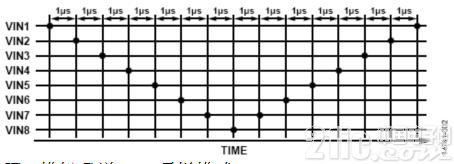

下面举一个简略的比如来讲,先把一个多通道非一起采样ADC采样次序编程为一个如下所示的次序:VIN1 → VIN2 → VIN3 → … → VIN6 → VIN7 → VIN6 → … → … → VIN3 → VIN2 → VIN1。

图2.模仿通道VINx采样形式

这样,在一个转化序列中模仿通道VIN1至模仿通道VIN7有两个转化成果,而模仿通道VIN8只要一个转化成果。运用软件对VIN1至VIN7通道的前后两次转化值取均匀,并将均匀均值成果作为终究ADC采样成果进行电力运用相关的后续核算。当整个采样序列中的ADC的采样距离时刻被严密操控成为等距离的时分(各样本之间相差1 µs)。,VIN0至VIN7的均匀值的成果在时刻轴上其实与VIN8大致是对齐的,相当于对1到8各个通道来了一次准同步的采样。

图3.时刻均匀样本与VIN8对齐

请留意,这正是将该办法称为准同步采样的原因。

运用准同步采样的边界条件

为了解运用准同步采样办法的边界条件,应剖析最差状况下的差错,并确认在体系规划中有必要做些什么来将差错操控在合理水平。

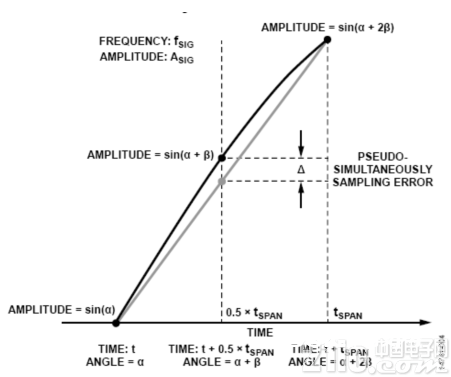

图4.确认采样差错

运用伪同步采样办法时,参见图4并运用如下公式核算差错。

两个样本点的均匀值为:

两个样本中点的正弦波原始值为:

因而,差错Δ为:

当α = (π/2 − β)时,差错最大;最大差错仅取决于β。

ΔMAX

因而,

其间:

N为一个采样序列中的总通道数。

fSIG为信号频率。

fS为采样频率。

例如,假定最大采样频率为1 MHz,ADC共有8个通道,输入频率为50 Hz,则一个50 Hz信号的理论最大起伏差错为:

留意,此差错可忽略不计。

当输入频率为250 Hz(五次谐波)时,一个50 Hz信号的理论最大起伏差错为:

当输入频率为2.55 kHz(51次ST谐波)时,一个50 Hz信号的理论最大起伏差错为:

关于此理论剖析,请留意以下几点的定论:

•较高采样速率有利于完结较高的体系级起伏精度。

•一次突发采样中的样本间时刻距离主张坚持稳定。

•无法准确丈量较高频率的输入信号。但是,在典型输配电运用中,较高次谐波的丈量精度一般不重要。对大部分运用而言,一般满意体系标准即满意。

运用AD7616完结伪同步采样

灵敏序列器

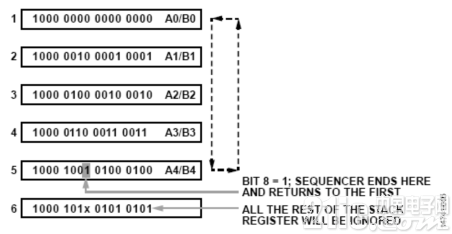

在软件形式下运用时,AD7616有一个灵敏且可编程的采样序列器。在体系上电初始化期间,用户能够写入序列器仓库寄存器来对AD7616序列器编程,为其设置预订采样次序。序列器仓库由32个寄存器组成,能够用它来完结1到32个采样次序的自在编程

各序列器仓库寄存器的8个LSB(通道D0至通道D7)界说A组(通道A0至通道A7)中的哪个通道和B组(通道B0至通道B7)中的哪个通道被选入下一次转化。寄存器中的位D8界说序列器在完结下一次转化之后是否中止以回来仓库的榜首层。当序列器激活时,它会从榜首个仓库寄存器中读取榜首次的采样通道装备来进行采样,假设D8=1,那么这个采样序列在完结这次转化今后就完毕,不然就会读取下一个仓库寄存器的值来进行通道的装备和采样,然后依据D8的值来决议是否整个采样序列到此为止。D8=0,那么持续读取再下一个,D8=1,那么采样序列完毕,回到榜首个仓库寄存器,等候下一次突发采样发动信号的到来。

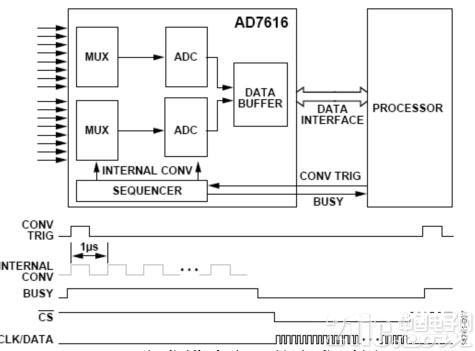

图5.对AD7616序列器编程以激活突发采样

突发形式

关于大部分传统复用输入和逐次迫临型寄存器(SAR) ADC,一个转化信号只能引起一个ADC转化。换言之,一个CONV脉冲只能对一个ADC通道进行采样。

为了满意运用准同步采样所需的边界条件,用户有必要经过发送一系列高速脉冲向ADC接连供给CONVST信号,并且这些脉冲之间的距离时刻相同。

图6.运用传统复用输入ADC完结的突发采样

此外,传统的ADC还有必要在十分短的时刻(下一个CONVST脉冲到来之前)内读出ADC转化数据。有时分,当客户期望运用通用微操控器(MCU)与ADC接口时,这种要求或许引起问题。

AD7616的突发形式十分好地处理了这个问题。当突发形式激活时,ADC只需要一个来自操控器的CONVST触发信号。AD7616的内部逻辑能够发生一系列高速内部CONVST脉冲以触发ADC内核,把预先经过可编程序列器修改好的采样序列扫面一般并且将整个扫描序列的ADC突发转化成果依照先后次序存储在数据缓冲器中。然后,操控器能够较慢速度读出整个数据帧而不必忧虑数据丢掉的问题。

图7.运用AD7616突发形式完结的突发采样

经过运用突发形式用户能够在一次突发的多通道扫描中完结ADC内核的最高采样速率,而对MCU MIPS和数据接口速度无任何约束。结合用户自界说的灵敏序列器,在AD7616上能够轻松完结准同步采样。

实践测验

测验设置

图8所示为实践测验设置。一个精细信号(音频精细)发生器向AD7616送入低噪声、低THD正弦波信号。

ADSP-CM408F处理器操控选用准同步采样装备的AD7616。ADC原始数据经过通用异步接收器/发送器(UART)发送给PC以供进一步剖析。然后,运用VisualAnalog®软件能够剖析ADC数据以取得沟通功用(SNR和THD),运用Microsoft Excel®能够运转DFT算法以取得相位和起伏信息。

图8.实践测验设置

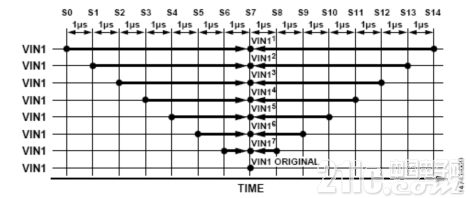

为使的试验成果的比照更为简单,咱们把可编程序列器编程为对同一个模仿输入通道VIN1进行采样。

图9.VIN1样本(S0至S14)

这样,在一个数据突发中,VIN1依照先后次序,一共被采样15次。如图9所示,榜首样本(S0)与终究一个样本(S14)配对以取得VIN11的均值成果,第二样本(S1)与第14个样本(S13)配对以取得VIN12的均值成果,以此类推。留意,第八样本坚持不变,被用作原始VIN1。一切其他均值数据(VIN11至VIN17)与原始VIN1进行比较,以取得终究测验成果。

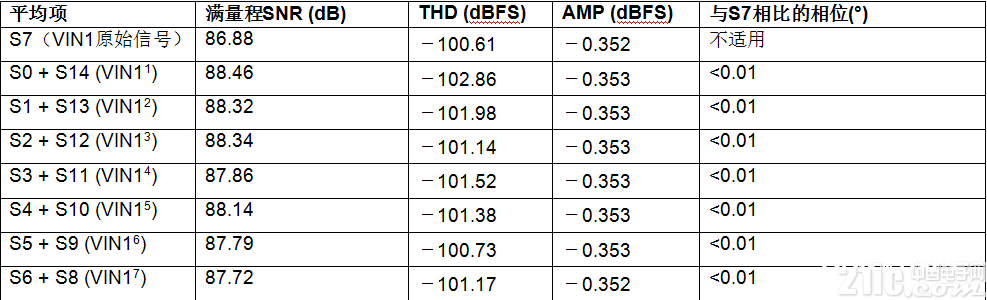

测验成果

测验信号 = 50 Hz(电力线基频)

关于低频输入信号(50 Hz),均值信号相关于原始信号的总推迟为0。起伏和总谐波失真(THD)底子不受影响。事实上,信噪比(SNR)功用还略有改进。概况参见表1。

测验信号 = 250 Hz(电力线五次谐波)

当输入信号的频率稍加提高到250 Hz时,均值信号相关于原始信号简直无推迟。起伏有−0.001 dB衰减(相当于0.01%,与“准同步采样的边界条件”部分所评论的数学推导的成果相吻合)。THD相关于原始信号总体上无变化,SNR则有0.5 dB到1 dB的改进。概况参见表2。

表1.测验成果,输入信号频率 = 50 Hz

表2.测验成果,输入信号频率 = 250 Hz

测验信号 = 2550 Hz(电力线51次谐波)

当输入信号频率提高到2550 Hz(关于50 Hz的工频信号来讲相当于51次谐波)时,处理成果的最大起伏差错略有添加。均值信号S0 + S14是起伏丈量的最差状况。衰减约为−0.055 dB,相当于0.63%的差错,与数学剖析成果共同。THD相关于原始信号总体上无变化,SNR有0.5 dB到1 dB的改进。相位差错依然十分低(0.01°),在大多数电力自动化运用中能够忽略不计。概况参见表3。

表3.测验成果,输入信号频率 = 2550 Hz

定论

大多数电力自动化运用的实践需要丈量的输入信号在50 Hz到2550 Hz范围内。这些运用基本上都经过运用AD7616的灵敏序列器和突发形式,来完结准同步采样以保证其各个模仿量通道之间被近似于同步的采样,并且整个体系丈量的沟通精度并不会下降。