5.2显现数据传输电路

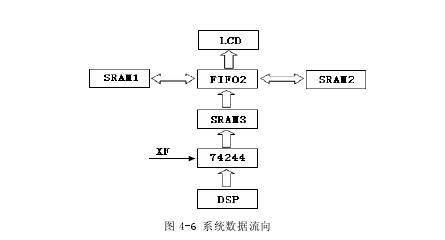

显现数据在整个体系的流向如图4-6.模仿信号经AD采样进来后经过FIFO进入DSP处理,处理完的数据随后存入SRAM3.SRAM3中的数据经FIFO2送入SRAM1和SRAM2.当要显现波形时,SRAM1、SRAM2分时复用,将显现数据再经过FIFO2送至液晶显现。体系中,SRAM1、SRAM2、SRAM3都为单口RAM,所以首要存在以下两个问题:1.合理分配SRAM3的地址总线、数据总线分时被DSP和FPGA2占用的问题;2.正确和谐SRAM1和SRAM2分时复用送显现数据的问题。

5.2.1 SRAM3的总线占用

处理SRAM3总线占用问题的关键是由DSP宣布的XF信号(如图4-7)。当XF为低电平时,SRAM3的读写、片选信号ram3_rws[2..0]由DSP宣布的读写和片选信号DSP_RWS[2..0]操控,一起DSP的数据、地址线经过74244和SRAM3的数据、地址线衔接起来,并运用XF作为选通讯号。当XF为高电平时,SRAM3固定为读信号和片选信号有用,此刻SRAM3中的数据经过FIFO2进入SRAM1和SRAM2.DMA_A[17..0]是FPGA里地址计数器发生的往SRAM1和SRAM2中写数据时的地址。这样,咱们就可以经过操控XF的凹凸来挑选是谁占用SRAM3的总线。

5.2.2 SRAM1和SRAM2的分时复用

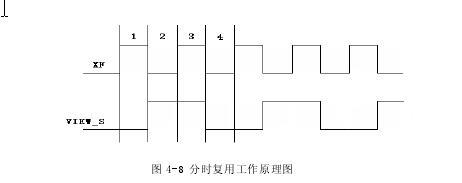

所谓分时复用便是指两片显现存储器SRAM1和SRAM2顺次向液晶供给显现数据。它的作业原理如图4-8所示。其间,View_S由XF反相后二分频得到。

图中各部分的作业状况如下:

1. RAM3经FPGA2向RAM2里写数据。一起,RAM1的数据送LCD显现。

2. DSP向RAM3里写数据。一起,RAM2的数据送LCD显现。

3. RAM3经FPGA2向RAM1里写数据。一起,RAM2的数据送LCD显现。

4. DSP向RAM3里写数据。一起,RAM1的数据送LCD显现。

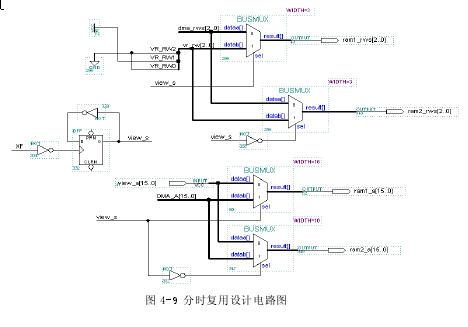

它的具体作业电路如图4-9.

图中,DMA_RWS[2..0]为固定的读信号和片选信号有用。VIEW_A[15..0]为显现时读显现RAM的地址。DMA_A[15..0]为写显现RAM时的地址。这两个地址都由FPGA中的地址计数器发生。

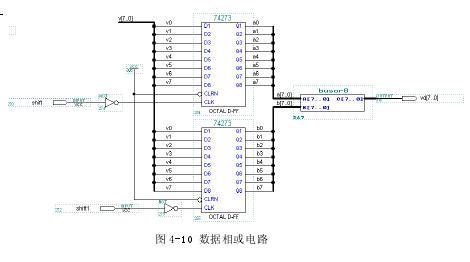

数字存储示波器的显现根本包含两部分,一部分是界面显现部分,包含菜单的显现,光标的显现等,另一部分是波形显现部分,波形显现部分是随时在更新的,而菜单显现部分更新的次数是很少,一般在不按键操作的状况下是很少改动的。所以咱们选用分页显现,行将显现存储空间分红两个区间,每个区间都是一屏显现所需的空间即为240×320×2÷8=19200Bytes.一个区间用来显现菜单,光标等不常改写的界面,一个区间用来显现波形,LCD显现时将两个存储区间里的对应地址的数据经过硬件电路相或今后再送LCD显现。这样在软件处理是节省了重复刷屏的时刻,也简化了软件的编写。图4-10为由显现RAM中两个的数据区间相或后送到LCD显现的电路。其间SHIFT和SHIT1别离两个区间的地址计数器的计数时钟,它们的时钟脉冲要求在一个CP周期内完结,即两个区间的数据读取有必要在一个CP时钟周期内才干确保正确的数据显现。

第六章串行接口通讯

在许多现场测验场合,工程技能人员都需求取得某种办法的丈量成果的硬拷贝,以便今后作为参考材料运用,或许设备陈述发生过错动作时需求检查以往的材料。别的,在许多状况下咱们需求把示波表中的信号传往PC机,一起在某些状况下,咱们也或许期望用PC机来对示波表进行操控,以上这些状况都要求示波表具有通讯才干。也便是说,示波表有必要装有通讯硬件以及其支撑的软件。咱们称此通讯用软硬件为“接口”。常用的接口有两种,RS-232接口和通用接口总线(GPIB),后者又称为IEEE-488总线。与并行接口比较,串行接口的最大特色是减少了器材引脚数目,降低了接口规划复杂性。

串行通讯是指数据按位顺次传输,串行通讯中要求发送和承受两边有必要恪守一致的规则,这样才干确保正常进行,这些对数据传送办法的规则便是通讯协议,通讯协议包含数据格局和时刻约束等方面的界说和要求等,通讯协议可由用户自己拟定,也可选用规范通讯协议。

串行数据传输可分为同步和异步两种形式。通用PC机的RS-232接口为通用异步接口UART(Universal Asynchronous Receiver and Transmitter),而MOTOROLA公司的串行外围设备接口SPI、行列SPI(QSPI)、PHILIPS公司的内部IC总线(I2C),National公司的微总线(MICROWIRE)均为同步串行协议。现在简直一切的数字信号处理器都供给了一个或多个串行接口,但是,大都DSP芯片供给的是同步串口。在实践的使用中,也需求DSP可以与外设进行异步串行通讯,如与PC机进行串行数据传输就要求DSP体系具UART串行接口。针对这种状况,本文研讨并完结了一种简略、牢靠的异步串口扩展办法。

实践规划中,咱们选用美国MAXIM公司的MAX3111串行异步收发器,与DSP的McBSP口直接衔接,将同步数据变换为UART异步数据格局进行传输。硬件上无需任何其它外围器材,一起因为异步数据的发送和接纳由MAX3111以硬件计划完结,所以软件编程需求考虑的也仅仅DSP与MAX3111之间的同步数据通讯。这样,用最简略的硬件衔接和软件编程就能完结同步到异步的串行数据格局转化。

6.1 McBSP的功用与特色

TMS320VC5416具有3个高速、全双工、多通道缓冲串行接口(McBSP),其便利的数据流操控可使其与大大都同步串行外围设备接口。McBSP是在规范串行接口的基础上对功用进行扩展的,除具有规范串口的功用特色外,其灵活性体现在如下几个方面:

◆双缓冲区发送,三缓冲区接纳,答应接连数据流传输;

◆可与SPI、IOM-2、AC97等兼容设备直接接口;

◆可编程帧同步、数据时钟极性,支撑外部移位时钟或内部频率可编程移位时钟;

◆具有彼此独立的数据发送和接纳帧同步脉冲和时钟信号;

◆多通道发送和接纳,最多可达128个通道,速度可为100Mbit/s.

6.2 MAX3111通用异步收发器

MAX3111通用异步收发器是MAXIM公司专门为小型微处理体系进行最优化规划的UART,它包含一个振荡器和一个可编程波特率发生器;具有一个可屏蔽的中止源;另具有一个8字节的接纳FIFO(先入先出)缓冲器。它使用SPI/MICROWIRE接口技能直接与主操控器进行通讯,线路简略、体积小,通讯速率可达30kbit/s.别的其内部除具有UART之外,还包含两个RS-232电平转化器,这样无需再接入一般的MAX232进行电平转化,即可使用一个芯片完结微控器(具有PI/M%&&&&&%ROWIRE接口)与PC机或其它设备之间的异步数据传输。

MAX3111经过SPI接口与主设备进行16位数据的全双工同步通讯,即主设备传送16位数据给MAX3111的一起,也可接纳到MAX3111发送的16位数据。主设备在MOSI线上向MAX3111发送的16位串行数据序列中包含传输格局操控字,如波特率设备、中止屏蔽、奇偶校验位等,一起还有发送的数据字。MAX3111在MISO线上向主设备发送的16位数据序列中除了接纳到的数据外,还包含中止标志等状况位。所以经过16位的实时数据传输,主设备可取得MAX3111作业状况信息,一起对其具有彻底操控权力。这样,两个设备的操控、状况、数据信息的实时通讯就确保了数据传输的牢靠性和稳定性。

6.3 TMS320VC5416与MAX3111的接口规划

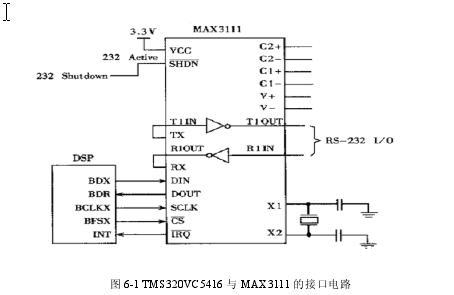

TMS320VC5416的McBSP串行接口作业于时钟中止形式时与SPI协议兼容,可直接与MAX3111进行衔接,然后完结与RS-232设备进行异步数据传输。此刻DSP作为SPI协议中的主设备,其接口电路如图6-1所示。

TMS320VC5416发送时钟信号(BCLKX)作为MAX3111的串行输入时钟,发送帧同步脉冲信号(BFSX)作为MAX3111的片选信号(CS)。在这种办法下对接纳时钟信号(BCLKR)和接纳帧同步信号(BFSR)将不进行衔接,因为它们在内部与BCLKX和BFSX相衔接。BDX与DIN衔接作为发送数据线,BDR与DOUT衔接作为接纳数据线。MAX3111的TX与T1IN衔接,RX与R1OUT衔接,以便运用其片内的转化器完结UART到RS-232电平的转化。MAX3111的中止信号(IRQ)与DSP的外部中止相连。

在SPI串行协议中,主设备供给时钟信号并操控数据传输进程。由MAX3111接口电路时序图6-2可知,有必要设置DSP的McBSP于恰当的办法才干确保与MAX3111的时序相合作。

MAX3111要求在数据传输进程中CS信号有必要为低电平,在传输完毕后有必要为高电平。此信号由McBSP的BFSX引脚供给,因而有必要正确设置DSP的帧脉冲发生器,使之在每个数据包传输期间发生帧同步脉冲,即在数据包传输的第一位变为有用状况,然后坚持此状况直到数据包传输完毕。

McBSP的采样率发生器发生恰当频率的时钟信号,由BCLKX引脚输出,确保主从设备间的同步数据传输。因而有必要正确设置DSP的采样率发生器时钟源(CLKSM)和时钟降频因子(CLKGDV)。依据SPI传输协议,有必要正确设置数据发送延迟时刻(XDATDLY)。由图6-2可知MAX3111要求在SCLK变高之间的半个周期开端传输数据。

所以有必要为McBSP挑选适宜的时钟计划,即设置McBSP的时钟中止形式。在本使用中选用McBSP的时钟中止形式2(CLKSTP=11b,CLKXP=0),这样即可确保与MAX3111的时序相合作。

定论

经过一年多的项目分析、证明、规划、制造及调试,现已完结本课题的规划使命,完结了样机的制造。本课题是“100MHz数字存储示波表”项目中数字体系部分。它是该项意图重要规划部分,经过本课题的研讨,本文首要完结了以下几点:

1.数据收集体系的研讨与规划。数据收集体系是数字存储示波器与模仿示波器的首要不同之处,它完结模仿信号数字化,经过实时取样和随机取样两种取样技能将模仿信号数字化。这儿首要难点在于AD在高速采样率下怎样防止采样时钟的搅扰和AD数据与FIFO的时序合作问题。

2.显现操控电路完结。首要规划精华在于在没有专用操控芯片下,选用FPGA规划LCD显现时序电路,彻底由硬件电路完结LCD数据显现流程以及多页面数据显现操控技能。

3.DSP与外部接口电路的规划。首要是经过MAX3111完结同步到异步的串行数据格局的转化。

一起在规划和调试进程中遇到了以下几点问题:

1.在调试LCD显现时,显现屏上某些点呈现闪耀现象。经研讨发现是LCD的显现操控时序合作欠好的原因。从头调整时序后,闪耀现象消失。

2.在随机取样时,规划的展宽脉冲电路时,发现跟着MAXPLUSⅡ每次编译的不同,波形康复呈现作用不一样,有时能正常康复,有时呈现飞点,后来在选用FPGA时选用了工业级,作用非常好。

经过以上作业,示波表的硬件软件调试作业已开始完结,考虑到项目规划和调试进程中碰到的问题以及与国外同类产品的比较,特提出了以下优化主张:因为本课题选用了随机取样技能,它只能测出单一频率的周期信号。关于非周期信号不能再现完好波形。故主张在经后作业中进步实时取样时钟。悉数选用实时取样技能。这样也简化了软件的规划。