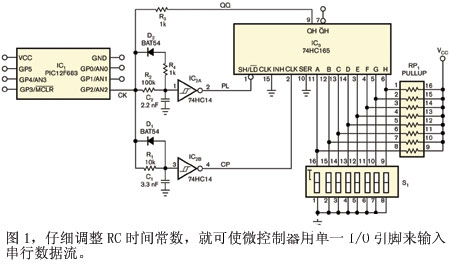

与UART的杂乱比较,用微控制器的单一输入引脚来输入多个信息比特更简略,事实证明这很有用。这种计划答应扫描键盘、形式开关或任何改动较慢的数字数据。参考文献1具体说明晰一种用单一引脚输出信号的办法。来自开关组S1的数据首要抵达IC3,后者是NXPSemiconductors公司的74HC165并串转换器(图1)。把数据加载到移位寄存器中,这需求PL线路上的一个脉冲(引脚1)。线路CK在微控制器引脚线路上把一个长脉冲作为输出发送出去,由此完结上述脉冲。R2和C2引进延时,而且一旦脉冲超越该延时,PL线路就变为低电平,数据被加载。

PL信号上升后,微控制器的I/O端口上的较短脉冲在移位寄存器的时钟输入端CP(不是在PL输入端)发生脉冲。这些时钟脉冲的持续时刻有必要满足长,应超越延时R1C1,但不能超越R2C2。这些时钟脉冲使数据移位,使得8比特在移位寄存器输出端QQ次序呈现。

假如微控制器的数据方向时刻短地改动,以便凭借高阻抗输入,那么上述移位寄存器数据会占分配位置,这是因为R1、R2、R3的相对值所造成的,R3值低得多。高阻抗状况存在的时刻有必要短于R1C1时刻常数(图2)。微控制器现在读取单一数据比特。三个不同周期的效果发生了三种功用:加载、时钟、数据读取。微控制器改动端口方向、读取引脚数据、把引脚方向重设为输出所需的时刻决议了时序。例如,1ms微控制器需求10ms。

为防止假CP脉冲,该时刻常数有必要低于0.33R1C1,因而R1C1可所以30ms,而R2C2可所以200ms。这些设置答应在大约1ms内完结一次8比特读取。为完成更快操作,可把RC继电器换成精细可再触发单稳多频振荡器(如NXP公司的74HC123)和逻辑门。可用更多移位寄存器扩大此计划,来读取数十个信号。

请注意:74HC165移位寄存器中的内部逻辑阻挠CP信号在LD处于有用状况时使数据移位。电阻器R4保证LD和CP的正确次序。二极管D1和D2使每个%&&&&&%敏捷放电,来“复位”R1C1和R2C2的延时功用。