最近在学ARM Cortex-M3,找了本声称很经典的书“An Definitive Guide to The ARM Cortex-M3”在看。这个系列学习笔记其实就是在学习这本书的过程中做的读书笔记。

第二章 Cortex-M3 概述

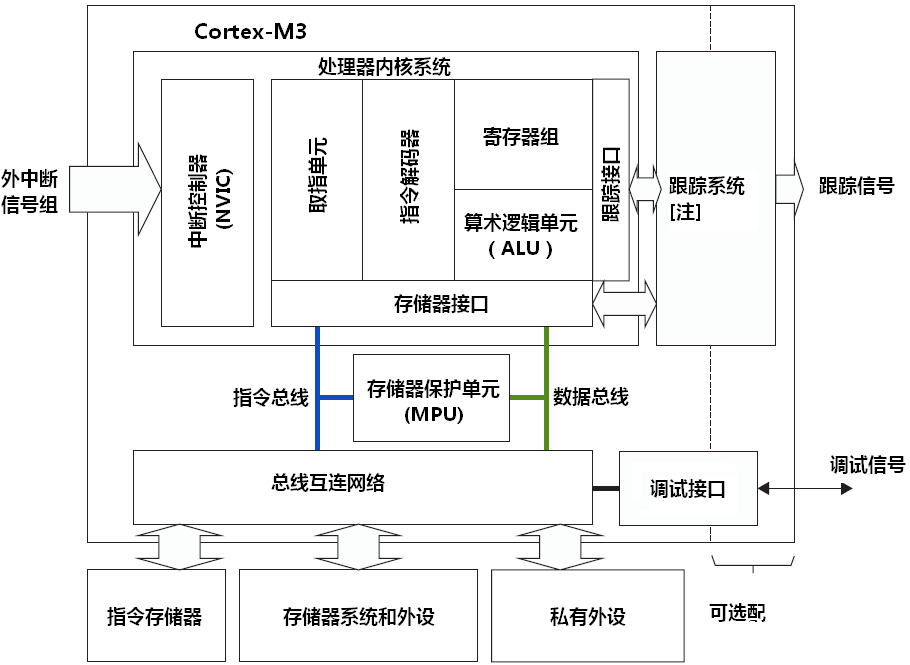

Cortex M3 内核的组成能够用一张简图来一共:

图 3 Cortex-M3内核简图

内核寄存器组包含R0-R15,R0-R12是通用寄存器,部分Thumb指令只能拜访R0-R7。

R13是仓库指针,实践上有两个,一个是主仓库指针(MSP)另一个是进程仓库指针(PSP),仓库要求4字节对齐。

R14寄存程序的回来地址。

R15是PC,记载程序当时的碑文地址。

特别功用寄存器包含:

程序状况字寄存器组(PSRs)

中止屏蔽寄存器组(PRIMASK, FAULTMASK, BASEPRI)

操控寄存器(CONTROL)

运转形式和特权等级

两种运转形式:handler mode和thread mode。

两种特权等级:特权级和用户级

中止例程作业在特权级,一般程序代码既能够作业在特权级也能够在用户级。

相互间的转换用下图来描绘:

图 4 操作形式转换图

嵌套向量中止操控器NVIC(Nested Vectored Interrupt Controller)

可嵌套中止支撑

向量中止支撑

动态优先级调整支撑

后边有一章会对NVIC进行详细的介绍。

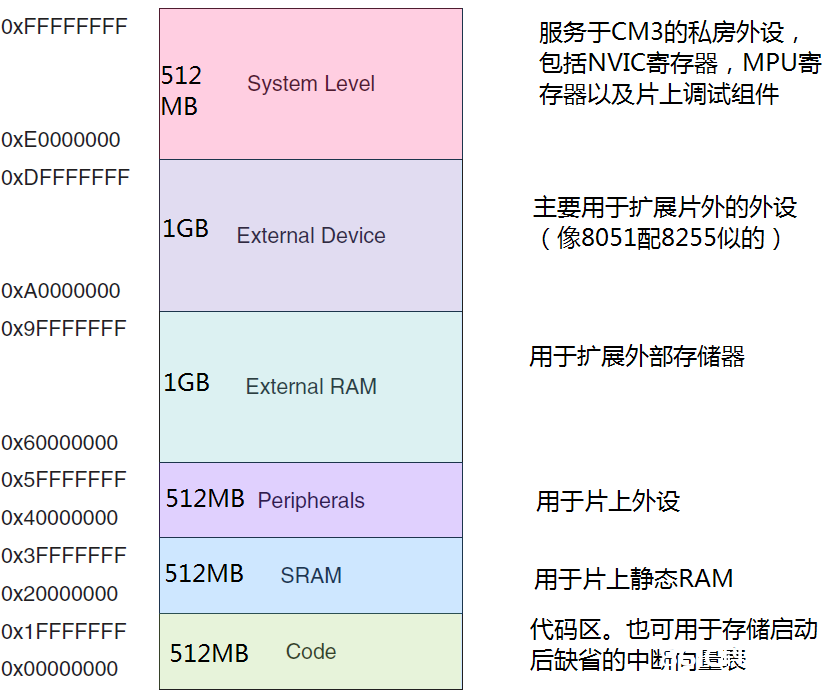

地址空间分配

与曾经的ARM 内核不同,Cortex-M3对地址空间的分配有个大的结构。向NV%&&&&&%寄存器等的地址也都被固定了下来,这就方便了在程序的移植。详细的地址分配能够用下图来简略的描绘:

图 5 地址分配

总线

Cortex-M3内部有若干个总线接口,以使Cortex-M3能一起读取程序代码和拜访内存,它们是:

指令存储区总线(两条)

系统总线

私有外设总线

中止和反常

Cortex-M3支撑11个内部反常和240个外部中止。当然,对详细的芯片,能够支撑的外部中止数量必定就要少的多了。

调试支撑

在支撑传统的JTAG基础上,还支撑更新更好的串行线调试接口。

根据CoreSight调试解决方案,使得处理器哪怕是在运转时,也能拜访处理器状况和存储器内容。

内建了对多达6个断点和4个数据调查点的支撑。