摘要 介绍了宽带载波电力线通讯协议中用到的信道交错。在此协议的基础上,提出了根据FPGA信道交错模块的规划计划。文中对信道交错的物理层完结办法进行了介绍,该办法是经过ROM读操作和RAM的读写操作来完结信道交错进程,较好地满意了资源和时延的两层要求。

关键词 信道交错;FPGA;宽带载波电力线通讯

跟着通讯技能的不断发展,呈现了各式各样的通讯,一般有线通讯和无线通讯之分,有线通讯一般是经过光缆电缆进行的通讯,而无线则是经过电磁波进行空中信息传递的通讯。尽管无线通讯省缺了有形的传输前言,经过空中接口进行通讯,但无线通讯在传输容量和传输质量都不如有限通讯。电力线网络覆盖规模广,是其他网络无法比拟的,而且是有限通讯,经过电力线进行通讯则成为研讨要点,但电力线的初衷仅仅用来进行电力传输,还没有考虑到用电力线进行信息的传递,所以原有电力线的铺设导致电力线信道特性较差、搅扰大、时变性差,不只存在多径时延问题,且存在频率挑选性式微的现象。跟着信号处理技能和信道调制技能的不断发展,现在现已能克服这种电力线信道差的问题。其间的关键技能便是正交频分复用(Orthogonal Frequency Division Multiplexing,OFDM),这是一种复用技能,一起是一种用多个彼此正交的子载波来传送信息的一种多载波调制技能。该技能能够处理电力线通讯信道差的问题,大幅进步了平铺利用率,并可完结电力线的有用通讯。

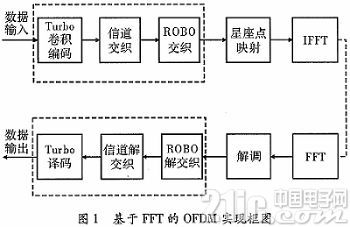

图1是根据FFT的OFDM完结框图。发送端:从数据链路层接纳数据,经过一系列的信号处理和改换,以OFDM调制办法经过将信号发送到电力线。接纳端:从电力线检测到信号后,做相应的反向处理,最终将电力线上的载波信号复原为数据,送到数据链路层。在电力线通讯体系中采纳信道交错技能,在时刻的维度上离散信道的突发过失,然后使得有回忆信道可近似转变为无回忆信道,使得规划的纠随机过失的纠错码相同适用于多径式微信道。

1 信道交错的基本理论

信道交错的理论建立在香依理论的基础上。Claude.E.Shannon提出:关于恣意给定的有噪声信道至少存在一种杂乱的编码办法,可使信道的传输速率无限迫临信道容量而一起确保传输过失率到达恣意小。而信道交错便是迫临这一相同理论的一种较好的完结办法。

信道交错的本质是一种置乱器,仅经过改动信息的结构来进步数据传输的可靠性。信道交错是经过把接连的比特信息分散开以防止突发过失事情。这样就能把过错的规模尽量操控在纠错电路的才能规模之内。在接纳端经过纠错译码电路后,将这种置乱次第信息复原就能最大极限的的正确译码出发送的信息。

依照信道交错技能关于数据次第的改动规则,信道交错码可分为周期交错和伪随机交错两类。周期交错又分为分组交错和卷积交错,周期交错指交错规则有清晰的周期性,序列内数据之间的交错距离稳定。所谓伪随机交错,指交错不选用仅有的单个交错深度值而选用有改变的交错深度值,但改变仍有必定的规则。

2 电力线通讯协议的信道交错完结

宽带载波电力线通讯协议中的信道交错进程包含信息位的交错、校验码交错、信息码和校验码之间的交错,半字节移位4个进程。具体的信道交错的进程如下:首要设定K代表信息bit的数量,N-K代表校验bit的数量,K个信息bit会分红4个子块,每个子块的巨细为K/4 bit,N-K个校验bit会分红4个子块,每个子块的巨细为(N-K)/4 bit,然后便是按进程顺次操作。

(1)信息位的交错。将信息bit存入一个K/4行4列的矩阵,顺次把每列存满。进行交错时每行的4个bit是一起读出的。从这个矩阵读出数据时,从第0 行开端,从第2次开端每次读时行地址加上参数StepSize,这样榜首轮读的行地址次第为(0,StepSize,2×StepSize,… [K/4]-StepSize),当读了[K/4]/StepSize行之后,就读到了矩阵的尾部,然后读下一轮的行地址初始化为1,之后每次读取时行地址加上参数StepSize,当读了[K/4]/StepSize行之后又到了行尾,这样第二轮读的行地址次第为(1,1+StepSize,1+2 ×StepSize,…[K/4]-StepSize+1),然后第三轮的行地址加1为2,顺次类推,经StepSize轮后悉数行均已读出。

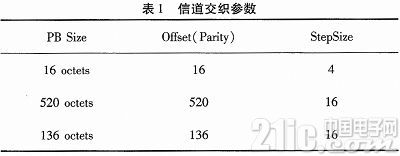

(2)校验码交错。校验码的交错与信息位的交错相似,仅仅每次读行地址时均加一个偏移量。因而,校验bit榜首次读从参数offset界说的行开端,步长参数仍是StepSize,文中界说T=(N-K)/4,榜首轮读出的行的次第为(offset,(offset+StepSize)mod T,(offset+2×StepSize)mod T,…(T-StepSize+offset)mod T),然后第二轮榜首行的指针加1,再重复作StepSize-1轮,最终经过StepSize轮,每轮读出了T/StepSize行数据,总共读出T行数据。表1列举了信道交错中3种传输块用到的参数。

(3)信息码和校验码之间的交错。输出的前4 bit为信息码,接着4 bit为校验码,以此类推。

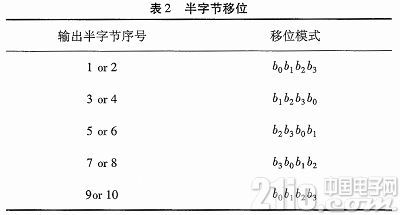

(4)半字节移位。半字节移位以4 bit为单位进行移位,不管信息bit仍是校验bit,每2个半Byte调整一次次第,表2列举了具体移位形式。而且全体以32 bit为一个循环进行半字节移位操作。

3 电力线通讯协议中信道交错规划

在宽带载波电力线通讯协议中信道交错处理的数据单元块有3种:PB16,PB136和PB520。FPGA中信道交错主要有两种完结办法:一是经过计数器和逻辑操控单元来完结;另一种是经过存储在ROM中的信道交错表来完结。经过计数器和逻辑操控单元来完结,其间会涉及到很多的除法和取模运转,时刻延迟大且不易操控。但选用存储在ROM中的信道交错表来完结的话,只需经过Matlab计算出信道交错表的映射联系,然后将Matlab中的数据导出生成HEX 文件作为ROM的初始值。最终按ROM中存储的地址写到RAM即可完结信道交错。其间ROM和RAM直接调用Altera的IP核。考虑到后者只用经过 ROM读和RAM读写就完结了信道交错,且逻辑简略、时延小,所以本规划计划选用后者。且每种数据单元块对应一张信息交错表,因而只需信道交错表就能满意体系的要求。宽带载波电力线通讯协议中信道交错的FPGA完结便是选用存储在ROM中的信道交错表来完结的办法。

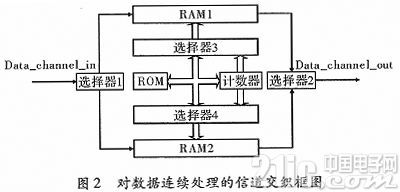

为了对数据进行接连处理,规划选用两个RAM一起作业的办法,完结框图如图2所示。具体做法便是经过对两个RAM的乒乓操作来完结数据的缓存和发送。在第 1个传输周期,在输入端经过挑选器1将数据写入RAM1。在第2个传输周期,在输入端切换挑选器1将数据写入RAM2,在输出端一起将RAM1中的数据经过挑选器2读出。在第3个传输周期,在输入端切换挑选器1将数据写入RAM1,在输出端一起将RAM2中的数据经过挑选器2读出。如此循环便可完结对数据的接连缓存和读出。

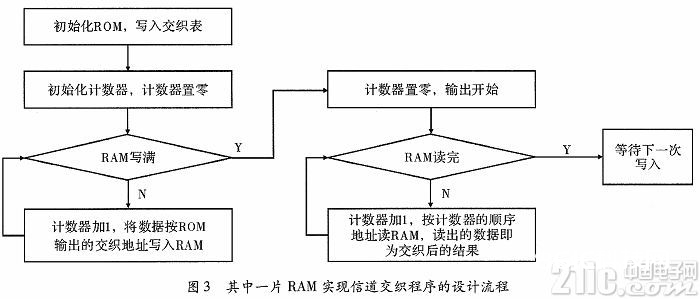

对其间一片RAM完结信道交错具体的完结进程便是经过操控ROM的读出和操控RAM的读写来完结:在ROM中寄存交错地址表,将RAM作为寄存数据的缓存器,先将计数器的输出送至ROM地址总线,挑选器再挑选从ROM读出的交错地址送至RAM的地址线完结交错;然后按计数器的次第地址将RAM中的数据读出,即为交错后的输出成果。具体的信道交错流程如图3所示。

4 仿真成果剖析

本文用Verilog HDL言语编程完结信道交错,并经过QuanusⅡ和Modelsim软件进行仿真验证。图4为截取的一段仿真波形,波形显现的是先按信道交错表的地址将输入数据写入RAM,输入数据是接连的256个0,1比特流,最终按计数器的次第地址读出交错后的数据,交错后的成果是前64个数据均为0,接着64个数据均为1,然后接着64个数据均为0,最终64个数据为1,与Matlab中的仿真成果共同,证明了该完结计划的正确性。

5 结束语

本文在宽带载波电力线通讯协议的基础上,给出了根据FPGA的信道交错模块的物理层完结办法。该办法从实际出发,权衡资源和时延的要求,实用性较强。其间,选用双RAM可完结流水线操作,处理了单RAM等候的时延的问题;选用信道交错表的办法,比较单纯选用逻辑操控的办法,可操作性和可移植性强。该计划已成功应用于某宽带载波电力线通讯模块中,证明该计划切实可行。