Mentor Graphics的Tanner EDA软件是一套针对定制集成电路(IC)、模仿/混合信号(AMS)和MEMS规划的产品。对物联网(IoT)需求的忽然上升使全流程混合信号规划环境面临共同的要求:经济实惠且易于运用,但功用强大,可创立布置物联网所需的各类产品。

简介

Mentor Graphics的Tanner EDA软件是一套针对定制集成电路(IC)、模仿/混合信号(AMS)和MEMS规划的产品。对物联网(IoT)需求的忽然上升使全流程混合信号规划环境面临共同的要求:经济实惠且易于运用,但功用强大,可创立布置物联网所需的各类产品。尽管许多EDA东西供货商为AMS规划供给软件,但这些东西不是本钱太高(性价比低),便是定制点处理方案需求很多数据操作和手动集成。Tanner EDA软件AMS IC规划流程具有其共同的优势。它供给了严密集成的混合信号规划套件,规划周期极短、性价比高,特别合适物联网和根据项目的规划。

前端规划

电源办理、显现器、图画传感器、光伏、生命科学、轿车、航空航天和消费类电子产品等器材所服务的运用和细分商场品种繁复,与AMS集成电路相关的规划应战也多种多样。可是,在AMS规划方面,物联网将会发生最大的影响。

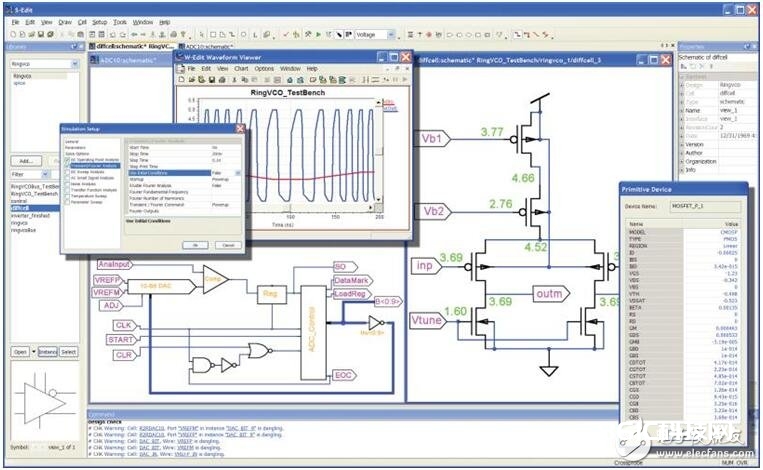

图1:Tanner S-Edit SchemaTIc输入规划和仿真渠道,显现了原理图、仿真波形、模型参数和仿真设置

在创立模仿/混合信号规划时,规划人员需求对两个范畴进行权衡。规划人员越快找到最优处理方案,就能取得更多时刻来处理扎手的极点状况。具体而言,Tanner T-Spice AMS支撑Verilog-AMS建模,经过根据高档方程式针对混合了行为的Verilog数字模块的仿真模块进行建模,然后完结杂乱混合信号IC的自顶向下的规划。规划人员能够快速探究混合信号架构,然后在具体规划单个模块时运用笼统的Verilog-AMS模型作为履行规范。

Tanner S-Edit原理图输入是一款前端规划东西,为创立模仿/混合信号规划所需的多视图单元供给简略易用的规划环境。S-Edit支撑已制作的原理图视图、以及SPICE、Verilog、Verilog-A和Verilog-AMS视图,因此规划人员能够轻松地以单元为根底交流笼统或具体模型。S-Edit经过Open Access或经过Cadence、Pyxis、Laker、OrCAD和ViewDraw的EDIF导入原理图并主动转化原理图和特点,以完结兼容数据的无缝整合。规划人员能够运用S-Edit的原理图规划查看功用快速找出常见过错,例如未驱动的网络、未衔接的管脚以及由多个输出驱动的网络。在运转仿真之前发现过错能够进步规划功率和速度,对AMS规划而言特别重要。

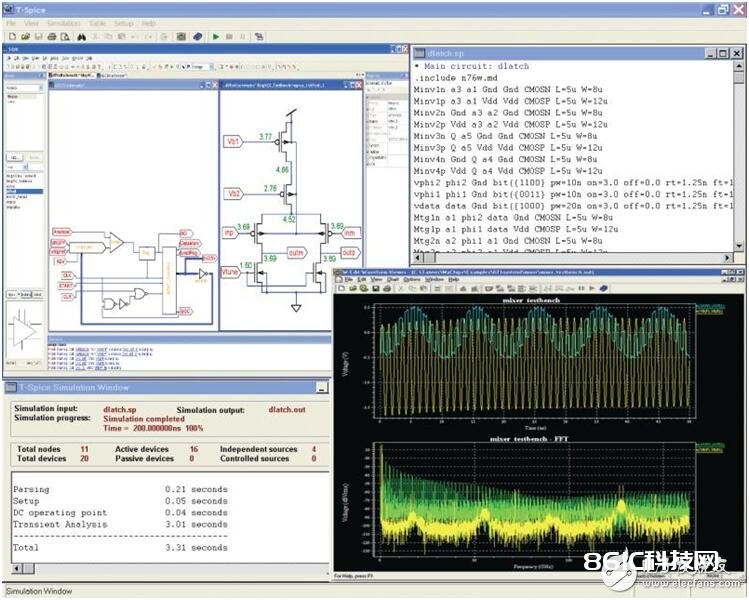

接下来是高精度的规划仿真。考虑到电路规划越来越大,杂乱性越来越高,且需求支撑各种晶体管和行为模型,这个使命对混合信号规划而言并非易事。Tanner T-Spice SimulaTIon支撑广泛的规范,具有经商场验证的可靠性、高性能和可扩展性,能够应对这些应战。T-Spice供给与HSPICE和PSpice兼容的语法,支撑职业最新模型,包括PSP、BSIM3.3、BSIM4.6、BSIM SOI 4.0、EKV 2.6、MOS 9、PSP、RPI a-Si & Poly-Si TFT、VBIC和MEXTRAM多种模型,然后经过全规模的晶圆代工厂模型轻松进行现代规划和传统规划的仿真。T-Spice使规划人员能够运用虚拟数据丈量、蒙特卡罗剖析和参数扫描准确地描绘电路行为的特征。它还支撑Verilog-A进行模仿行为建模,使规划人员能够在进行器材的全体规划之前,验证体系级的规划。

图2:Tanner T-Spice Simulator图形用户界面包括:原理图、SPICE网表、仿真日志和波形数据

此外,T-Spice还能够运用Mentor Graphics ModelSim数字仿真器进行高性能的混合信号仿真。规划人员能够结合运用Verilog、Verilog-A、Verilog-AMS和晶体管层级的SPICE加载网表。T-Spice可主动切割网表并发动AMS协同仿真,一起在处理任何SPICE或Verilog-A规划时,将恣意数字模块发送到ModelSim。只需信号在模仿/数字鸿沟发生变化,T-Spice和ModelSim就会协同仿真并相互通讯。

完好的物理地图功用

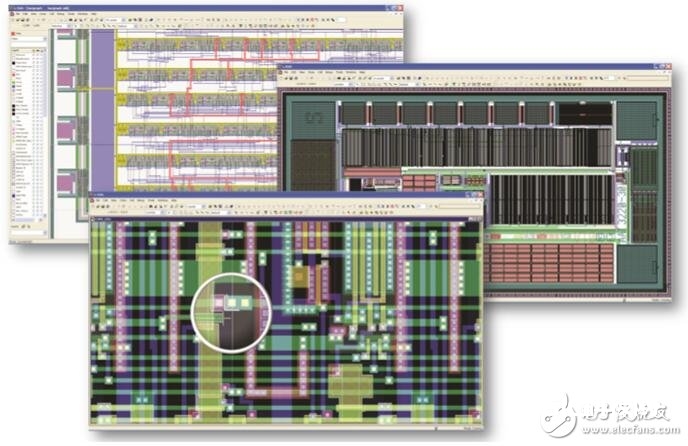

前端规划和验证作业完结后,接下来便是物理地图了。规划人员有必要再次权衡优先次序,特别是规划的模仿部分。再次重申,Tanner能够供给根据PC渠道的最优功用组合,易学易用。Tanner L-Edit IC Layout东西是一款完好的层次化物理地图修正器,结合了快速烘托东西和内置功率东西,使规划人员在创立用于规划的地图时能够最大极限地提高功率。该东西的修正功用经过优化,所需的鼠标操作比任何其他地图修正器都要少。内置功率功用包括目标捕捉、对齐东西、主动生成保护环、针对恣意形状和曲率的多边形目标的杂乱布尔运算,以及原理图与地图之间的交互显现。

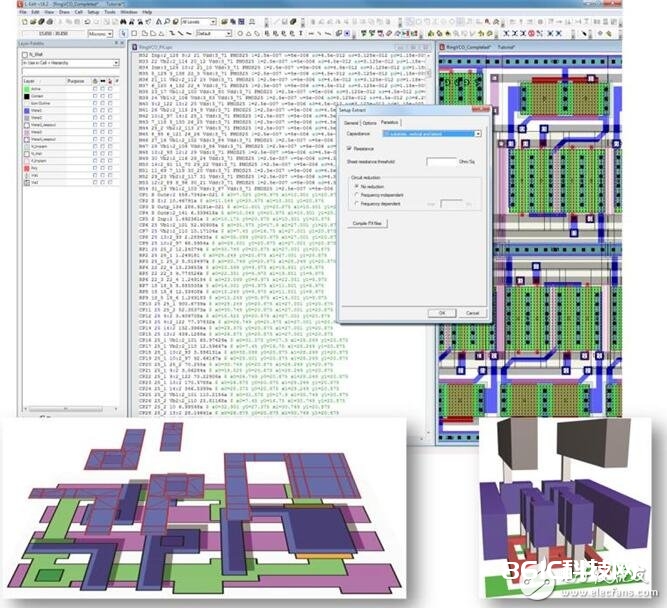

图3:Tanner L-Edit IC Layout 东西显现三种规划的地图数据

L-Edit支撑参数化单元规划,使规划人员能够主动化地创立自定义地图生成器或运用DevGen轻松设置针对MOSFET、电阻器或电容器等常见器材的地图生成器。该东西的交互式规划规矩查看(DRC)功用能够在地图修正时实时显现违规状况,协助规划人员能够一次性成功创立简练、无误的地图。此外,经过L-Edit的节点高亮显现功用,规划人员能够高亮标出一切衔接至节点的几何图形,然后快速发现并修正短路和开路等LVS问题。

L-Edit经过支撑多个用户在同一地图作业来提高规划功率。规划人员能够直接运用晶圆代工厂供给的文件,无需手动设置。然后削减了物理规划东西中 CAD支撑担负,使规划人员能够集中精力进行规划。

地图布局团队能够经过完好的原理图驱动地图流程来最大化功率。S-Edit和L-Edit坚持通讯与同步,包括交互显现和ECO符号。根本元件、子单元和参数化单元的主动实例化可节省时刻并防备过错,而实时飞线和辅佐性手动布线能够最佳方法快速进行规划布局和布线。

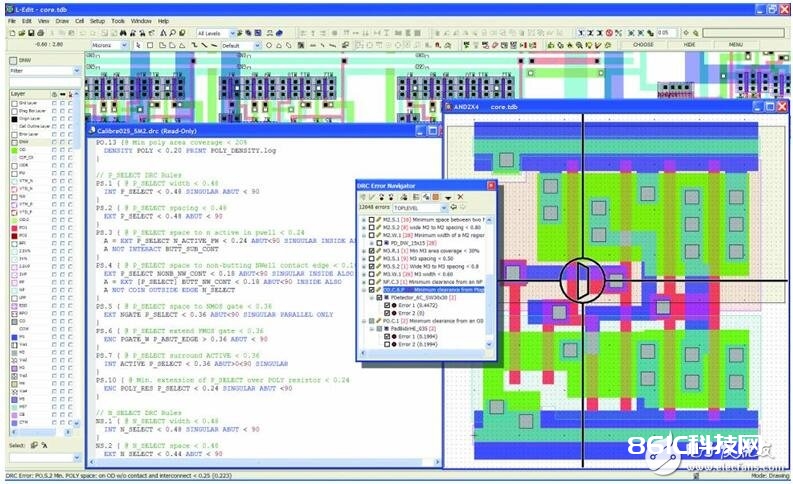

物理验证

Tanner Verify DRC和LVS东西供给了全面且经济的物理验证处理方案。这些东西可履行模仿/混合信号IC规划规矩查看(DRC)和网表提取。单元中呈现违规状况时,层次化规矩查看引擎能够在第一时刻发现,使规划人员得以立刻更正违规之处,而不是在屡次重复违规之后才发现问题。别的,该东西可与Tanner L-Edit IC Layout集成,然后能准确找出过错、快速修正并加速调试速度。

图4:Tanner L-Edit IC Layout在语法高亮显现修正器中显现规划规矩查看、DRC运转成果、以及针对特定规矩违规状况的过错符号

建模地图的效果

对先进的工艺节点(以及频率更高、电压更低的相关电路)而言,互连寄生参数已然成为一个巨大的应战。跟着工艺尺度变小,互连厚度添加,以此抵消因互连宽度减小而导致的电阻添加。这就使得横向耦合电容的影响比笔直耦合电容要大得多。横向耦合能够导致不同的时序行为,要准确计算出推迟和电路行为,就有必要将其包括到仿真中。

Tanner ParasiTIc ExtracTIon是一款高性能的寄生参数提取东西,作为可选的插件供给。该东西可与Tanner L-Edit IC Layout集成,然后能够轻松快速地提取寄生参数。它能够从地图中快速提取处于仿真安排妥当状况的SPICE网表,包括器材(MOSFET、双极晶体管等)和互连寄生参数。Tanner Parasitic Extraction还能够提取针对各个节点的准确的、完好的寄生网络,包括笔直和横向耦合电容以及互连电阻。此外,经过内置的网表约简算法,该东西能够在无需将仿真精度下降至用户指定频率的状况下简化RC寄生网络。

图5:经过反向标示互连寄生模型仿真环型振荡器

精简的数字物理规划

在创立绝大部分电路是模仿电路、少部分电路是数字电路的规划时,即所谓的“大A小D”(Big A/little D)规划,模仿规划人员面临着许多应战。从概念层面来看,模仿规划团队开端面临的困难是针对混合信号电路进行自顶向下的全体规划。在整个规划流程中,他们要面临来自多个范畴的应战。例如,规划人员或许很难把握数字逻辑为内部状况或躲藏状况的数字电路的边际状况或问题。全芯片时序剖析对规划人员来说一般很难敷衍。假如存在颇具规划的数字部分,他们就很难完结整个时序剖析。最终,在物理验证方面,数字逻辑发生的噪音对具有相同基底的模仿电路来说就或许会太大。

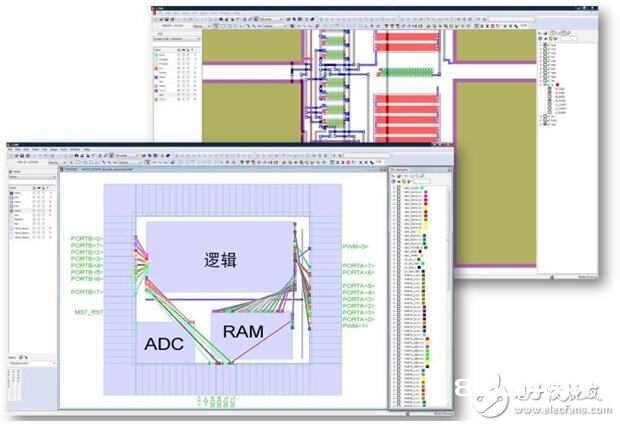

Tanner套件专用于处理这些应战。运用混合信号东西的模仿规划人员可获益于其更强的主动化、更高的准确性、更低的NRE本钱以及更短的上市时刻。为此,Tanner处理方案采用了专门针对“大A小D”AMS商场的从RTL到GDS的完好流程。这是一款完好的逻辑组成东西,具有针对区域、电源、时序和可测验性规划(DFT)的组成与优化功用。Tanner Place and Route与L-Edit高度集成,使规划人员能够彻底掌控布局和布线流程中的每个进程。TimeCraft是一款速度快、容量大的静态时序剖析器(STA),可用于纳米时序剖析和Sign-off。(请注意,ModelSim可供给运用布局后布线信息的动态时序剖析。)

全芯片拼装

任何全面的模仿/混合信号流程将包括全芯片拼装进程,行将首要功用模块置入压焊框并进行顶层信号和总线的布线。

图6:Tanner L-Edit IC Layout的原理图驱动地图展现了实时飞线并支撑手动、人工辅佐和全主动的布线形式

Tanner的全芯片拼装处理方案经过S-Edit和L-Edit的SDL接口完结。以顶层模块为例,规划人员能够运用SDL的实时飞线摆放模块,以尽量削减布线拥塞。规划人员还能够运用SDL的短路和开路查看器快速查看衔接问题,该查看器无需运转完好的LVS便可在单元环境中运转并高亮显现过错。

SDL Router是一款与SDL集成的主动布线引擎,能够加速模仿单元的地图和顶层芯片拼装的布线。该东西使规划人员得以集中精力在要求精密的布线上,以便操作或处理对模仿灵敏的部分或悉数网络。对一切剩下的电路,SDL Router可主动为非要害网络布线,以不同的用户指定宽度为不同网络布线,支撑用于图层转化的多个通孔。规划人员还能够经过它将现有的几何图形符号为特定网络的一部分,然后经过网络依照规划人员的目的挑选、高亮显现和拼接几何图形。

结语

2015年3月,Mentor Graphics收买了Tanner的事务财物,运用其雄厚的技能领导力和全球散布网为致力于从事IC、MEMS到IoT器材的各种混合信号项目的规划人员供给支撑。这些规划人员面临着各式各样的应战,大多数与IC的功用和杂乱性继续添加有关。一起,事务压力迫使规划人员有必要要缩短上市时刻和削减返工。Tanner套件从根底开端制作,以规划人员的需求为中心。一些EDA东西供货商供给了用于AMS规划的软件,但这些东西不是本钱太高(性价比低)、便是需求很多数据操作和手动集成的自定义点流程东西。Tanner套件能够为AMS规划人员供给共同而全面的东西套件,完结业界无可对抗的功率、可用性和性价比。