1 导言

POS-PHY Level 4(PL4)是用于在物理层和链路层之间传输分组和信元的通用接口,支撑多种物理层协议,广泛使用于ATM、POS(Packet over SONET/SDH)以及10吉以太网,敏捷成为用于物理层设备与链路层设备间进行分组或信元传输的最通用的接口规范。

POS-PHY Level 4是由Saturn Development Group在POS-PHY Level 3的基础上拟定出的接口规范,在光互联网论坛(OIF)被规范化为SPI-4 Phase 2(SPI-4.2),在ATM论坛中被规范化为frame-based ATM Level 4(FBATM-4)。与之前的10Gbit/sec接口比较,PL4接口协议更易于工程完结,减少了管脚数量和功耗,增强了信号完整性,被业界广泛选用。

PL4接口选用16位的依据LVDS I/O的数据总线,数据速率622Mbits/sec,供给带内操控字和用于流量操控的带外状况通道。带内操控字指示各个通道的地址、分组的开始和结束,以及校验和;状况通道选用2位状况总线,供给接纳方的通道状况信息,并对发送方各通道的数据进行轮询调度。PL4接口协议还界说了练习序列,用来消除数据总线传输进程中各传输线上数据的不同步现象。

咱们的规划方针是完结10路1Gbps以太网线路接口功用。物理层设备选用PMC-Sierra公司的PM3388芯片,链路层设备选用两块Altera公司的Stratix GX系列FPGA芯片,别离完结数据的发送和接纳并对数据进行处理。StraTIx GX系列FPGA芯片供给了速率达500Mbps~3.1875Gbps高速通道,最高1Gbps的源同步差分串行接口,和最多达4M的RAM,能够满意PL4接口10Gbps速率的规划需求。

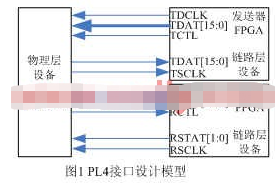

如图1所示PL4接口规划模型,PL4接口可分为发送器和接纳器两部分。因为PL4接口数据总线只要16位,时钟速率抵达320MHz(DDR),在FPGA内是难以抵达这样的速度的,因而在FPGA内部选用128位数据总线,80MHz的时钟。

2 发送器作业原理:

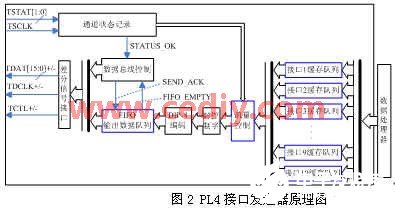

在电路上电复位后,首要,数据总线操控模块接连发送练习模板,通道状况记载模块查看接纳方发送来的10个通道的状况信息是否有用,并锁存有用的状况信息。假如状况信息有用,阐明接纳方电路已处于安稳的正常作业状况,向总线操控模块发送信号STATUS_OK,布告已获得有用的通道状况信息。然后,数据总线操控模块中止发送练习模板,查看输出数据行列的状况标志FIFO_EMPTY。假如为空,没有数据要发送,则数据总线操控模块发送闲暇操控字;假如为非空,则向输出数据行列发送数据传输答应信号SEND_ACK,输出数据行列模块将行列中的数据读出并发送到差分信号接口模块,进行并串转化后发送到PL4总线上。

在发送器正常作业时,从数据处理器侧接纳数据并依照数据的意图接口送到相应的缓存行列中。流量操控模块依据各个通道的状况信息,选用加权轮询调度(WRR)的战略从10个缓存行列中读取数据,送到封操控字模块增加相应的操控字,再送到DIP-4编码模块核算DIP-4校验码,最终送到输出数据行列等候发送。

3 接纳器作业原理:

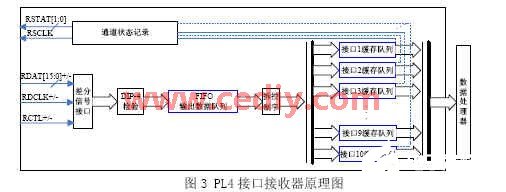

在接纳器中通道状况记载模块将各接口的缓存行列的状况发送到状况总线。差分信号接口模块接纳16位的差分信号,经串并转化变为128位数据。在DIP-4查验模块查看校验码,假如有过错,则将过错的分组或信元扔掉,查看后的数据送入输入数据行列模块。在拆操控字模块将操控字去掉,增加相关的帧头、帧尾标志,并依据操控字送到相应的接口缓存行列。

因为StraTIx GX系列器材中嵌入了专用电路动态相位定位器dynamic phase aligner(DPA),能够纠正因为漂移引起的时钟和数据线上的相位差,所以在接纳器中不需求经过练习序列完结数据线和时钟线的相位同步,对接纳到的练习序列直接丢掉,不再做进一步处理。

4 差分信号接口模块的完结

StraTIx GX系列芯片内嵌了专用的差分源同步串行接口电路,供给了移位寄存器、锁相环和动态相位对齐(DPA)电路,数据传输速率可抵达1Gbps。经过设置串并转化系数和时钟倍频/分频系数,能够得到所需求的数据总线宽度和时钟频率。在咱们的规划中串并转化系数和时钟倍频系数均设为8,可将128位宽总线上的数据串行化,发送到16位差分数据总线上,也可将16差分数据总线上的数据解串为128位宽的数据。

将128位宽的数据写入移位寄存器时,把第128位数据以16比特为单位划分为8块,依照数据在16位差分数据总线上传输的次序,处于最高位的16比特块的每一位别离写入16个移位寄存器的第一位,第n个16比特块的每一位别离写入16个移位寄存器的第n位,如图4所示。

从16位差分数据总线解串为128位的进程与前面相似。

5 对角穿插奇偶校验(DIP)的完结

5.1 16位对角穿插奇偶校验(DIP)的规矩

DIP-4校验码仅对操控字及其前面的载荷数据进行核算,假如操控字的前面依然是操控字,那么仅核算操控字自身。核算时操控字的低四位按全1核算,核算的成果填写在操控字的低四位。图5对DIP-4校验码进行了功用性描绘。第一次抵达的16比特数据循环右移一位后,与第2次抵达的16比特数据进行模2加运算,运算的成果再循环右移一位,依此类推,遇到操控字中止,将得到的16位校验和的高8位与低8位进行模2加运算,得到8位校验和,再将高4位与低4位模2加,得到4位的DIP-4校验码,并填写到操控字的低四位。

5.2 128位数据的对角穿插奇偶校验的算法

假如选用16位的数据总线,要抵达10Gbits/sec的速率,就要求运用640MHz(SDR)的时钟,这在现有的FPGA内是做不到的,因而咱们有必要寻觅一种易于完结的解决办法,能够选用160MHz或80MHz的时钟对64位或128位宽的数据进行DIP-4编码,这在FPGA内比较简略完结。图6给出了128位宽数据的DIP-4编码的办法。

如图6所示,将128位宽的数据分红8个16比特块,把每次抵达的128比特数据的处于同一列的16比特块,依照与图5中相似的办法进行运算。不同之处在于,16比特数据每次循环右移8位后与下一次抵达的128位数据中处于同一列的16比特块进行模2加运算,而不是循环右移一位。将第n列16比特块运算后的16位校验和sum n循环右移n-1位,再将8个新的16位校验和SUM n进行模2加,得到最终的16位校验和,再将高8位和低8位模2加得到8位校验和,将高4位和低4位模2加得到最终的DIP-4校验码。

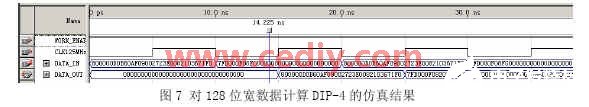

假如图6中128位宽数据的最终一行中,第二列即26×16比特块为操控字,这以后的16比特块也以闲暇操控字填充,则对本段载荷数据的DIP-4码的核算规模包含载荷数据和26×16比特块的操控字,这以后填充的操控字按全0核算,而且要对核算的成果进行批改。批改的办法是,最终一行中,第一个操控字后假如有W个填充的闲暇操控字,那么将核算得到的4位DIP-4码循环左移W位,这是因为27~32×16比特块尽管按全0核算,但前面的数据与这些全0的比特块进行模2加时,依然要循环右移,所以咱们经过循环左移康复到正确的校验和。这样做看起来好像有些费事和剩余,但用硬件完结时这样做是简略高效的。图7给出了对128位宽的需进行批改的一段数据核算DIP-4校验码的仿真成果,能够得出结论,这种办法能正确核算DIP-4校验码,而且比较简略、高效。

6 结束语

本文介绍了在Altera公司的StraTIx GX系列FPGA器材中完结POS-PHY Level 4接口协议的一种规划计划,并具体介绍了128位宽数据的4位对角穿插奇偶校验码的核算办法,经过仿真证明这种办法是正确的。此计划能够使用于路由器的线路接口、交流背板等通讯设备中,而且已经在国家863项目“高性能T比特路由器”的10×1G比特以太网线路接口的规划中得到使用。

责任编辑:gt