1 引 言

跟着信息需求量的增大,网络都逐步朝着归纳化、宽带化方向开展。数据速率的进步,关于数字信号处理的速度和质量的要求也越来越高。

在数字基带传输体系中,为使基带数据传输取得满意小的误码率,有必要使码间搅扰和噪声的归纳影响最小。奈奎斯特榜首原则指出了要消除码间搅扰,体系从发送滤波器经信道到接纳滤波器总的传输特性所应满意的条件。依据这一传输特性,实践体系一般选用具有升余弦滚降特性的滤波器作为发送滤波器。在第三代移动通讯中,信号的码片速率高,频谱旁瓣大,在传输时简单发生邻道搅扰,影响体系容量。假如在发送前,选用奈奎斯特(Nyquist)FIR滤波器将数字基带信号进行成形滤波,紧缩旁瓣,能够大大减小搅扰的影响,然后下降误码率。因而,滤波器的规划在通讯体系中占有重要的位置,它的性能将直接影响整个通讯体系的性能目标。本文在对滤波器进行研究的基础上,运用窗函数规划了一种奈奎斯特升余弦数字滤波器,并用硬件言语编程进行了FPGA完结。

2作业原理及结构

在数字信号传输进程中,咱们只需求特定时刻的波形幅值怎么无失真的传送,而不必要整个波形无失真。奈奎斯特榜首原则,又称榜首无失真条件告知咱们:假如信号经传输后整个波形发生了改变,但只需其特定点的抽样值坚持不变,那么用再次抽样的办法,依然能够准确无误得康复原始信码。咱们能够求出满意奈奎斯特原则的成形滤波器,在实践中得到广泛应用的是起伏频率响应具有奇对称升余弦形状过渡带的一类滤波器,一般称之为升余弦滤波器。

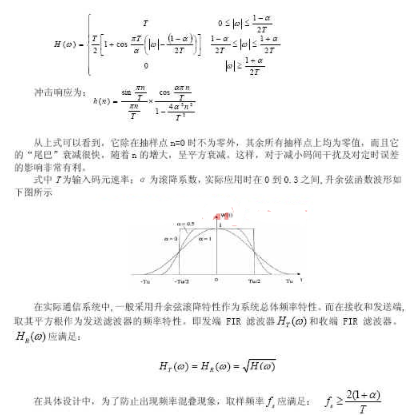

为了减小或消除码间搅扰的影响,滤波器的传输特性的过渡带应规划成具有升余弦滚降特性即规划成奈奎斯特FIR成形滤波器。具有升余弦滚降特性的滤波器传输函数为:

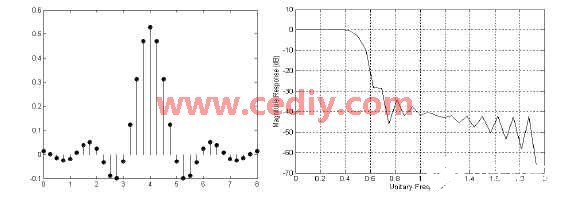

取滚降系数α=0.22,则取样频率依据上式可知应大于2.44倍输入码片速率,咱们取为4,取FIR滤波器的有限长度N为33,调用Matlab中的库函数rcosfir能够得到其频域和时域剖析图:

依据Matlab的剖析成果,阻带最小衰减为33.983085dB,满意规划要求。因为存在量化差错,需求把量化前后的频率响应比照,看量化后的频谱特性是否满意规划目标,然后决议量化的比特数,一起也或许要求对滤波器的阶数调整。在满意频谱要求的前提下尽或许的减小量化比特数和滤波器的阶数,以便利规划的完结。成形滤波器假如选用直接型需求33次乘法和30次加法,运用了平方根升余弦滚降滤波器的系数对称性,挑选分布式算法,能够削减大约一半的乘法运算,则使33次乘法削减为16次,总的运算量大大减小。

3 FPGA完结及结构阐明

3.1 FPGA整体结构

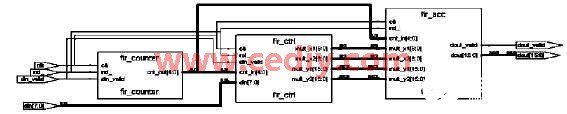

要规划的滤波器为33阶FIR根升余旋滤波器,假定输入取样数据速率为3.84M,滤波器的主时钟只需能够到达76.8M,便能够使每个数据在滤波器里边的核算时刻为20个时钟周期,这样做首要是考虑到要使乘法器的运用个数削减(本规划中运用了2个乘法器),进步乘法器的运用功率。因为在滤波器的完结进程中,有很多的乘、加运算,所以为了到达较高的时钟频率,有必要在运算的进程中运用流水线办法。

运用分布式算法,所规划的滤波器区分成了三个首要的模块,如下图所示。其间,fir_counter模块首要完结一个计数的功用,输出的计数成果操控别的两个模块的运转;fir_ctrl完结输入数据移位以及送入乘法器的数据的挑选;fir_acc则完结乘累加功用并输出最终的成果。

计数模块:计数器输出总线宽度为5bits,数据巨细为0~31,在没有din_valid(输入有用信号)信号的情况下,计数器输出会从0到31重复输出

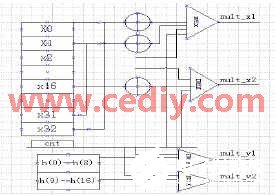

从下面的仿真图中也能够看出,计数器在din_valid信号操控下的计数进程。 数据操控模块:该模块完结的首要功用首先是将输入的数据保存在寄存器里边,进行移位,然后将所保存的33个最近输入数据半数相加,放到别的的寄存器里边。接着依据计数器成果,将相应的半数数据和滤波器抽头系数输出作为后边乘累加运算的输入数据。下面的硬件框图能够实际该部分的首要算法。

在代码的编写上,首要由一个状况机完结,分为Idle和Work两个状况,状况为Idle时,处于闲暇状况,乘法器输出为0,当din_valid信号为“1”时,触发状况机进行跳转,Idle-》Work ,一起将滤波器输入数据存入寄存器并进行移位。进入Work状况后,依据计数信号的值进行各种挑选运算。

从下面的仿真图中能够看出状况机随输入有用信号信号和计数信号改变而发生的跳转。其间,状况(state)为高电平时表明状况Work,为低电平则表明状况Idle。

乘累加模块:该模块首要功用是完结mult_x1与mult_y1以及mult_x2与mult_y2的乘操作今后把两个乘法器的输出送入累加器,完结循环累加作业。操控该部分的首要要害是一个计数器和一个输出有用信号,每20个时钟输出一次数据。详细计数进程和输出有用操控如下:

3.2 仿真验证

所运用的仿真东西为ModelSim,上面的波形截图就是来自ModelSim的wave窗口。咱们用相同的输入数据,分别用ModelSim和Matlab进行仿真,将仿真成果进行比较,得到简直相同的成果。(因为输入的滤波数据为随机发生的数据,所以得到的成果没有什么规律性可言。)

4 结 论

运用窗函数规划FIR滤波器的原则是:一是挑选主瓣较宽的窗函数,然后加大阻带的衰减,确保通带的平稳,二是在确保阻带最小衰减目标的情况下,恰当添加列长N值,使过度带窄一些。但N值的改变一起影响过度带和主瓣的变宽或变窄,别的挑选主瓣较宽的窗函数时(平等N值下),其过度带就宽一些了,可见这两个规划原则是无法一起满意的,这一定论可从上面的规划示例中得到验证。因而规划FIR滤波器时,应依据技术目标,经过屡次实验,找到适宜的窗函数和N值 。本文作者的立异点是在原有的滤波器优化结构的理论基础之上对FIR滤波器的硬件模块进行的了规划,选取Verilog HDL言语进行硬件模块区分,分程序进行完结,一起选取尽量少的乘法器,尽或许的优化结构是要害,以到达节省本钱简化工序的作用。

责任编辑:gt