LPDDR4是用于移动运用的最新双数据率同步DRAM,它是当今高端便携产品中常见的DRAM类型,运用于如Samsung Galaxy S6智能手机,Apple iPhone 6S [1],以及数种最新发布的设备。除了移动运用之外,估计LPDDR4会像其上一任LPDDR3那样运用于平板电脑、轻浮笔记本电脑中,会选用“底层存储器”装备,亦即,DRAM以物理办法焊接在主板上。

LPDDR4在很小的PCB面积和体积上供给了巨大的带宽;在3200Mbps的数据率下,当两片Die封装在一同时,单个15毫米x15毫米LPDDR4封装包可供给25.6 GByte/s的带宽。LPDDR4建立在LPDDR2和LPDDR3的成功根底之上,增加了新的特性并引入了首要的结构改动。

本白皮书中阐明晰LPDDR4与曾经一切JEDEC DRAM规范的差异之处。评论了下述方面:

规划人员为何挑选LPDDR4

LPDDR4体系结构的亮点

怎么最好地装备LPDDR4通道

怎么处理具有多通道衔接的2片和4片封装

经过体系级芯片(SOC)切割同享通道的长处

怎么优化通道以完结最低功耗

为什么是LPDDR4?

LPDDR4包含多项特性,这使得SOC规划团队可以下降别离DRAM的功耗。关于比如PC和服务器等桌面设备,一般将运用安装在双列直插内存模块(DIMM)上的DDR器材,所述DIMM坐落64位宽总线上。这类板级解决计划可以就地晋级DRAM容量,但需求长且负载较重的衔接线,与较短的走线比较,它耗费的功率更高。关于运用LPDDR2、LPDDR3和LPDDR4的体系,每条总线上的内存器材一般数量更少,衔接线也更短,因而耗费的功率比DDR2、DDR3和DDR4器材更低。

规划团队可以调用LPDDR4 DRAM内的节能选项。这些特性包含更低的电压和I/O电容;更小宽度的多路复用指令和地址总线;消除了on-DRAM DLL;更快进出的低功耗待机形式;更快、愈加简略的变频。

最终,LPDDR4 DRAM具有温度感知改写特性,这有助于使DRAM的改写率与DRAM的位单元自身的要求匹配,特别是在低功率自改写待机形式下更是如此。在待机形式下可自动启用该特性,相似地,在自动形式下可读取温度指示,使得LPDDR4操控器可以调理其自改写率,从而与LPDDR4器材的热状况相符。

LPDDR4选用了针对移动设备的模型

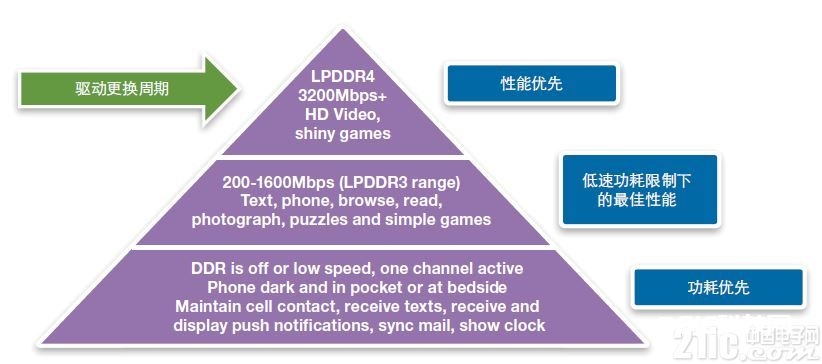

在实践运用中,移动用户仅在较少的时刻段内才会用到LPDDR4的最高作业频率。此刻,用户或是收集或显现高清晰(4K)视频,或是玩具有高图形要求的游戏,或是处理图形,或是引导或加载新的软件。

在部分时刻段内,内存会降至LPDDR3速度等级。这一功能水平足以支撑文本、呼叫、网页阅读、相片、简略游戏:一切这些功能对CPU或GPU没过高要求。

在大部分时刻段内,移动设备并不运用,它或是在口袋内、或是在床边,此刻DRAM断电或处于低速形式下。仅一个内存通道处于活动状况下,用于履行“一直在线、一直衔接”使命。在该形式下,设备履行后台使命,如坚持电池触摸,接纳音讯,接纳/显现推送告诉,邮件同步,以及时刻显现。

但是,正是因为最高运用时刻的设备功能,许多移动用户晋级了其设备,这正是该运用形式下优异用户体会十分重要的原因之地点(图1)。

图1:最高运用时刻是移动用户晋级循环的驱动要素

LPDDR4体系结构改动

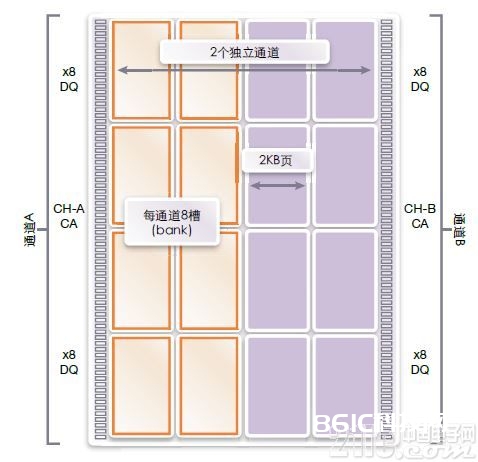

与前代比较,LPDDR4规范中确认了多种功能和特性改进。最为重要的是,LPDDR4对体系结构进行了严重改动:LPDDR4器材选用了每一裸片上2个独立通道的布局计划。

DDR2、DDR3和DDR4器材的每一封装包供给了一套指令地址输入总线和一套数据总线,最为常见的是每一封装包一个裸片。LPDDR2和LPDDR3的每一封装包可供给1~4个裸片。关于LPDDR4、LPDDR3和LPDDR2,在双裸片和4裸片封装包景象下,一般供给了2套独立的指令地址输入和数据总线(通道)。换句话讲,LPDDR2和LPDDR3器材施行了部分多通道,其间,每一封装包供给了2个独立通道。LPDDR4将该特性发挥到极致,这是因为每一裸片都有两个独立通道,大多数封装包都有4个通道。

衔接多个通道

LPDDR4体系结构天然具有2个通道(图2),每一裸片有2套指令地址输入和2套数据总线。LPDDR4的2裸片封装包供给了4个独立通道。为了更有效地运用LPDDR4,规划人员有必要了解LPDDR4体系结构改动对SoC体系结构的影响。

图2:LPDDR4双通道体系结构

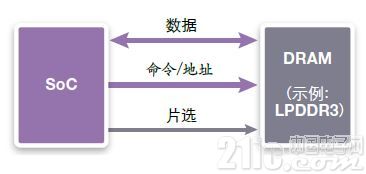

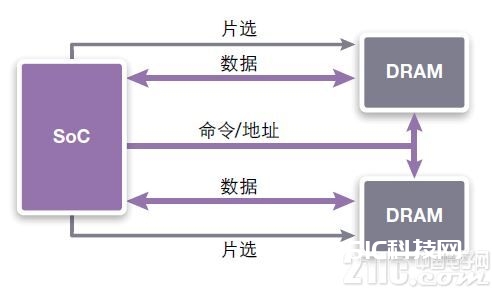

关于具有1个通道(如LPDDR3的单裸片封装包)的单个DRAM器材,只能做单向衔接,即SOC上的指令/地址总线接到坐落DRAM上的指令/地址总线,SOC数据总线接到DRAM数据总线(图3)。片选(CS)可在需求时使能DRAM。

图3:衔接单个DRAM设备的规范办法

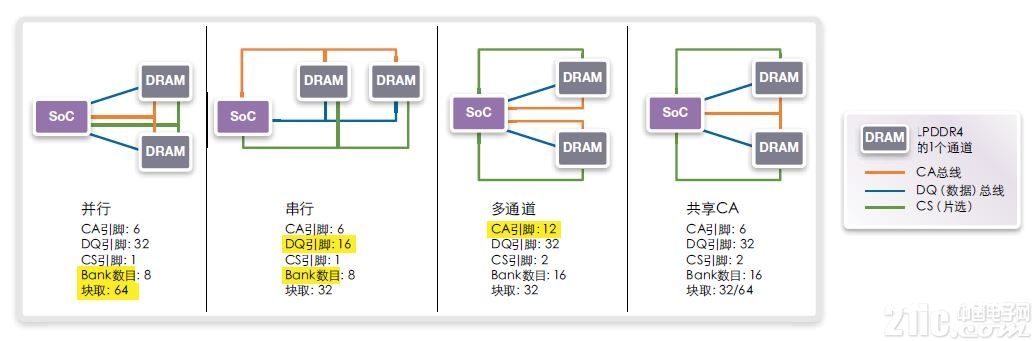

2个DRAM器材,或具有2个独立接口的单个DRAM器材(如LPDDR4)可支撑4种或许装备:

并行(前后紧接)

串行(多级)

多通道

同享指令/地址

并行(前后紧接)衔接

关于在DDR2/DDR3/DDR4方面具有丰厚经历的规划人员,最了解的挑选是并行或前后紧接装备。并行装备(图4)关于2个或多个DRAM裸片是恰当的,关于与同一指令/地址总线相连的LPDDR4的2个通道也是恰当的。它们选用了相同的片选,但每一数据总线具有独立的数据通道。在这类并行衔接中,一切的DRAM器材接纳相同的指令和地址,但会经过不同的字节线发送其数据。因为可一同拜访一切器材,因而两个DRAM一直处于相同状况。它们翻开相同的内存页面,并拜访相同的数据列,但保存在每一 DRAM中的数据不同。

图4:并行(前后紧接)衔接

串行(多级)衔接

第二种挑选是选用串行或多级装备将器材衔接在一同(图5)。这等效于将多个DIMM置于PC上的同一通道内。指令/地址和数据总线均衔接在两个DRAM器材上,但依据指令循环选中的2个不同的片选,以对两个DRAM器材的拜访进行独立操控。这两个器材可处于不同状况,具有不同的活动内存页面。典型情况下,SOC担任操控同享数据总线,保证DRAM不会一同进行数据传输。

图5:串行(多级)衔接

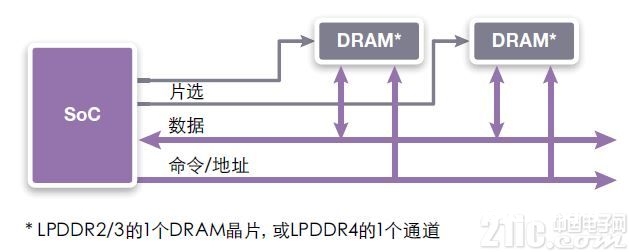

多通道衔接

多通道衔接(图6)为DRAM的每一通道或每一DRAM器材供给了与SOC的独立衔接,其间,每一器材或通道具有自己的指令/地址总线,数据总线和片选。因为选用了这一灵敏装备,每一DRAM器材(或器材组)可以互相彻底独登时作业。它们或许处于不同状况,接纳不同指令和不同地址,当一器材履行写入操作时,另一器材可履行读取操作。

多通道衔接还答应DRAM作业在不同功耗状况下。例如,某一块内存或许处于待机自改写形式,而另一内存处于彻底激活状况。

图6:多通道衔接

同享指令/地址(CA)衔接

最终一种装备挑选更常运用在非低功耗DDR器材中,这是一种具有同享指令/地址(CA)或同享AC(图7)的多通道装备。在该装备下,两个DRAM设备接纳相同的指令和地址,与串行衔接相似,片选决议了哪个DRAM器材担任监听特定的时钟周期,因而每一器材或许处于不同状况下。两个通道之间的DRAM指令裁定在SoC内部完结,但每一DRAM可以独立传输数据。

图7:同享CA衔接

双通道衔接的各种装备选项的比较

这些装备选项中的每一个各有其优缺点(图8)。例如,并行施行仅有8个可用库(bank),任一时刻在32位数据总线上可突发块取的最小数据量为64字节。并行办法不太适合于运用堆叠封装(POP)的规划。

图8:LPDDR4的双通道(1个晶片)衔接选项比较

串行衔接也不太适合于POP完结。它确实能节约一些DQ引脚,但因为DRAM器材同享了数据总线,它所供给的带宽只要其他解决计划的一半,该办法的吸引力较低。

同享CA适合于DDR体系,多通道衔接使得规划团队可以从LPDDR4中获取最大优点。

办理具有多通道衔接的2裸片和4裸片封装包

在LPDDR4的施行中,最常见的办法是在单个封装包中运用2个LPDDR4裸片,该包供给了4个16位通道,可完结8种不同拓扑计划。在将LPDDR4器材衔接至SOC的8种或许办法中,有三种特别有用的施行计划:

“真实”的4通道,双通道加双并行,彻底并行

关于期望在其LPDDR4设备中完结最大带宽的规划团队,特别是在运用较小的数据块传输时,或许会考虑真实的4通道施行计划(图9)。与其他施行计划比较,它具有最大的bank数目,以及最小的块提取尺度。它要求在SOC上具有24个CA引脚,可与SOC上的4个独自的内存操控器以及PHY一同施行。

图9:真实的4通道施行

双通道加双并行施行在全并行施行和4通道施行之间完结了杰出折衷。关于LPDDR3-LPDDR4组合(图10),它特别有用。在运用LPDDR4的前期商用SOC中,大部分都选用了该装备。

双通道加双并行

图10:双通道和并行施行

全并行施行仅选用了6个CA引脚,具有最大的DQ数(64)。但是该体系中仅供给了8个Bank。最小尺度块提取尺度为128字节,这将会束缚其在某些运用中的实用性。因为总线负载或芯片级时序收敛方面的原因,或许还需求仿制CA总线。

图11显现了双裸片4通道LPDDR4多通道施行(左边)和4裸片施行(右侧)的示例。LPDDR4封装包具有4个衔接的裸片,每一物理通道具有与其相连的2排(rank)内存存储体。关于该装备,要求规划团队在包的4个通道的每一通道的串行方向上扩展衔接。不幸的是,4裸片包未供给8通道连通性;在4裸片包上只要4个通道。

图11:双裸片和4裸片施行。4裸片LPDDR4多通道和串行施行增加了DRAM容量。该解决计划与2裸片封装包兼容

归纳而言,引荐的双裸片LPDDR4施行为:

双通道加并行,这是LPDDR3用户最了解的计划,也是可以完结LPDDR3/LPDDR4组合的完结办法;

4通道,这是最灵敏并具有潜在最高功能的计划。

关于同享通道的规划引荐,经过多Bank改进LPDDR4的功能

相似地,LPDDR4承继了DRAM的许多特性,其存储结构由Bank构成,每一Bank具有多行(Row),每一行具有用于存储数据的多个列(Column)。拜访坐落相同行内保存在列中的数据很快,拜访坐落不同Bank内不同的行也很快,但拜访坐落相同Bank内的不同行则会很慢。

独立拜访其他器材的每一通道意味着,每一通道上的每一Bank可以具有不同的活动行。关于像视频和网络包等在内存中随机散布的小尺度的数据传输类型而言,具有更多的Bank可以防止一些固有的、会束缚功能的内存时序参数。在尽或许多的Bank上传输数据可以改进功能是因为它能下降遇到一些内存时序参数的概率。

在体系中有更多的Bank,并延长在每一Bank上完结指令所需的时刻这一办法可以改进功能,是因为下降了因tRRD、tFAW和tRC内存时序参数所导致推迟的概率::

tRC:内存的行周期时刻。这是触发同一Bank中不同行所需的最小时刻。

tRRD:行-行推迟。这是触发不同Bank中不同行所需的最小时刻。

tFAW:4激活窗口。该时序参数的意义是,在一个tFAW窗口内,不能宣布4个以上的激活(active)指令。LPDDR4规范将其设为tRRD的4倍,因而,关于LPDDR4,它们实践上是相同的守时束缚,关于其他内存,或许会选用tRRD和tFAW之间的不同联系。