作者 宋哲 朱铁林 张志芳 天津航天中为数据体系科技有限公司(天津 300457)

宋哲(1987-),男,硕士,工程师,研讨方向:图画处理、无线通讯。

摘要:针对无人机遥感红外相机传输视频实时性以及机载存储空间有限等问题,提出了一种FPGA结合专用芯片ADV212的视频紧缩处理计划,该计划可对720×576分辨率的红外视频进行实时紧缩并可经过串口接纳外部命令调整视频紧缩比,FPGA装备ADV212初始化以及接纳ADV212紧缩后的视频数据,数据经过FPGA处理后传输到机载收发信机并传回地上设备。测验结果标明,体系作业安稳可控,视频紧缩实时性强,可广泛使用于无人机遥感范畴。

0 导言

无人机在高空飞行时,机载遥感相机实时收集的视频数据量十分巨大,对其处理办法一般有两种:一是运用无人机机载存储设备直接存储视频数据,待无人机降落后再处理,但是机载存储空间究竟有限,因而需将视频数据进行紧缩后再存储;二是经过无线数据链设备实时地将视频数据传回地上,而实践可用的无线通讯带宽十分有限,为了满意实时性的要求,必须将视频数据进行紧缩后再进行无线传输[1]。传统的视频紧缩办法,如MPEG-4、H.264是运用视频的帧间相关性进行紧缩的,其解码时间长,对实时性要求较高的体系不适合[2-3]。而JPEG2000是把运动的视频序列作为接连的静止图画来处理,对每一帧图画独自紧缩,图画康复的实时性较好。

ADI公司的ADV212芯片是现在市场上为数不多的能够单芯片支撑JPEG2000编/解码功用的芯片[4],它们能对动/静态视频图画实时紧缩与解紧缩,并能取得高清晰度的实时图画,一起也能供给很好的图画传输灵活性和可扩缩性。因为具有弹性的界面,ADV212可用来与多种形式视频和静态印象格局调配运用。ADV212的一个杰出长处便是它能够多芯片并行作业,从而进步其编解码功率,一起也支撑更高格局的印象。相对其它的硬件处理计划,ADV212的处理计划更完好,功用更全面,适用于多种视频和静态图画格局。

本文提出了根据ADV212和FPGA的红外视频紧缩体系,AD转化芯片ADV7189实时收集模仿视频信号并转化成10 bit数字信号输出到ADV212,经过FPGA对ADV212芯片进行初始化装备,ADV212以1:100的紧缩率对输入的视频信号进行紧缩,紧缩后的数据经机载射频收发信机发送到地上接纳设备。

1 体系整体规划

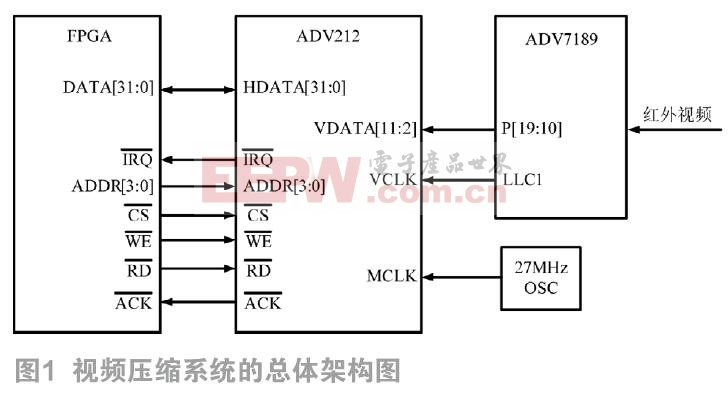

整个体系包含三个模块:ADV7189担任模数转化,ADV212担任视频数据的紧缩,FPGA担任芯片的装备和数据的接纳,图1给出了视频紧缩体系的整体架构。ADV7189芯片具有模仿视频信号的收集和模数转化的功用,其支撑NTSC、PAL、SECAM等制式的模仿视频输入,数据格局包含CVBS、S-Video和YPrPb等。输出数字信号支撑8、10、16和20位ITU-R BT.656 YCrCb数据。本体系红外模仿视频输入信号选用PAL制式YPbPr,分辨率为720×576,隔行扫描25 帧/s。FPGA经过I2C总线对ADV7189进行装备,作业时钟为27 MHz,输出数据位宽为10 bit,输出数据格局YCrCb为4:2:2,编码格局为EAV/SAV。

ADV212芯片具有实时紧缩宽和紧缩标清和高清视频信号的功用[5],支撑最高6级的9/7和5/3小波改换;图画的尺度可编程,3色彩重量4:2:2隔行扫描情况下宽带可达2048像素,单色彩重量情况下宽带可达4096像素;不可逆形式像素输入最大速率为65 MS/s,可逆形式像素输入最大速率为40 MS/s[6]。本体系中ADV212选用5级的5/3小波改换,每块图画的尺度为128×32像素点,输入数据为ADV7189输出的数据,速率为20 MS/s,即160 Mbps。ADV212装备紧缩比为100:1,即输出数据的速率为1.6 Mbps,输出数据的格局为JP2。

FPGA选用Xilinx公司的Virtex-5系列XC5VFX70T[7],其具有11200个Slice,5 MB Block RAM,6个时钟办理单元,640个用户I/O,大局时钟由外部40 MHz晶振供给,彻底可完结对ADV7189和ADV212的装备及数据的读写。

2 ADV212的作业原理及芯片装备流程

2.1 ADV212的作业原理

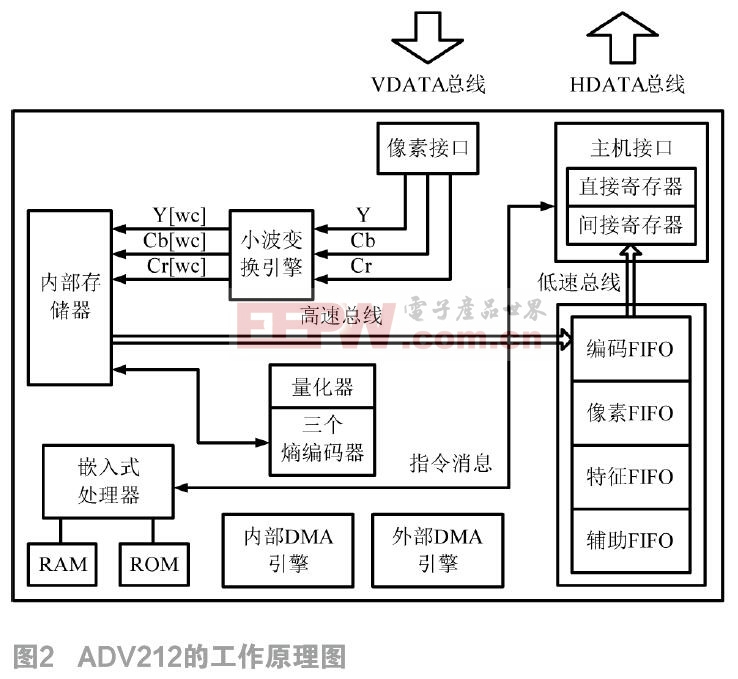

ADV212芯片内部作业原理如图2所示。该芯片由主机接口、像素接口、小波改换引擎、存储器体系、熵编码器和量化器、嵌入式处理器和内外部DMA等组成[8]。本体系作业在ADV212的主控编码形式(Normal Host),详细的作业流程为:视频数据经过像素接口输入到小波改换引擎中,进入小波改换引擎的数据,每个128×32的图块将经过5/3滤波器分解成许多频率不同的子带,将对应的小波系数写入内部存储器中。小波改换后的系数经过3个熵编码器被分解为独立的码块单元,选用量化、率失真优化和关联性建模等办法对数据进行紧缩,紧缩结束后以JPEG2000码流形式送回内部存储器。存储在内部存储器中的JPEG2000码流经过内部DMA引擎传输到编码FIFO中,编码FIFO作为高速内部存储器和低速主机接口间的缓存器,当编码FIFO到达设定的阈值时,JPEG2000码流便能够经过HDATA总线输出到芯片外部。

2.2 ADV212芯片装备流程

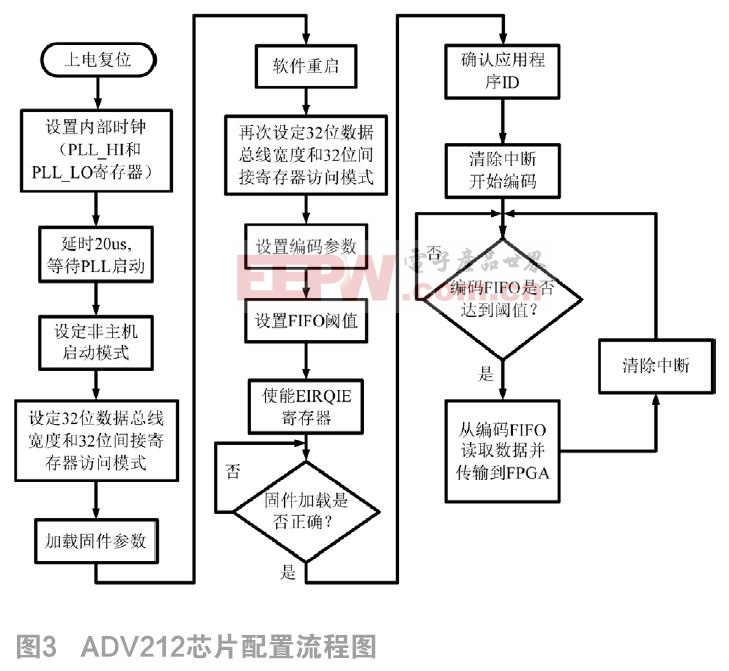

如图3所示,FPGA装备ADV212直接存放器PLL_HI和PLL_LO,将ADV212内部时钟JCLK和HCLK装备为108 MHz,延时20 ms后设置ADV212为非主机发动形式,设置ADV212数据总线宽度为32 bit,直接存放器拜访形式为32 bit。FPGA经过直接地址存放器IADDR和直接数据存放器IDATA加载ADV212固件,固件参数来自ADI官方供给的.sea文件,存放在FPGA内部的32 KB Block RAM中[9]。固件加载结束后,装备ADV212,进行软件重启,再次设置数据总线宽度和直接存放器的拜访形式,并设置视频编码参数和编码FIFO的阈值。一切的存放器装备结束后,经过EIRQIE存放器使能FIFO中止,即当FIFO中的数据到达阈值时,体系会发生中止。经过检测体系的ID来判别固件程序是否加载正确,芯片处于紧缩编码作业的ID为0xFF82。当芯片开端进行紧缩编码正常作业时,体系不断检测FIFO中的数据是否到达阈值,到达阈值并发生中止后,FIFO中的数据将被读取到FPGA中。

3 FPGA与ADV212之间通讯及仿真测验

FPGA装备ADV212初始化和FPGA读取ADV212紧缩后的数据过程中,FPGA与ADV212之间均选用异步通讯办法,FPGA经过改动发送的地址来读写ADV212不同的存放器值,下面给出详细的读写操作办法。

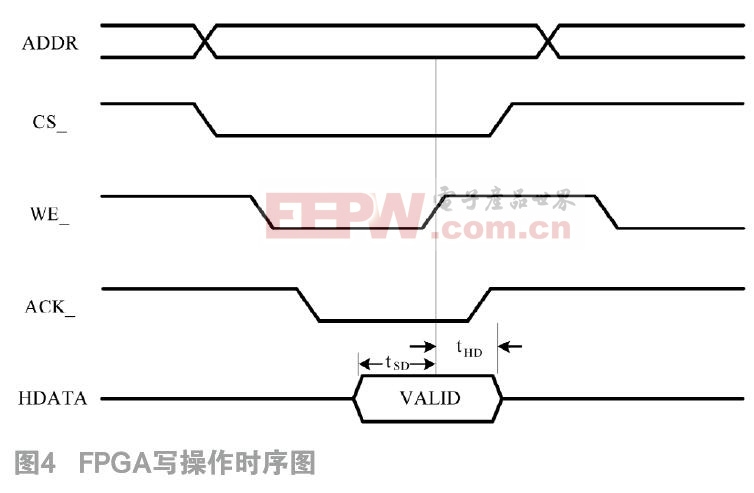

3.1 FPGA写操作

FPGA向ADV212写数据的时序如图4所示,ADDR为地址总线,CS_为片选信号,WE_为写使能信号,ACK_为ADV212握手信号,以上信号均为低电平有用,HDATA为数据总线。由图4能够看出,ADV212在WE_的上升沿对HDATA总线上的数据进行采样,采样前后需求确保树立时间tSD和坚持时间tHD内数据不变。FPGA写操作详细流程如下:

首要,FPGA向ADV212宣布地址和片选使能,下一个时钟周期FPGA将写使能WE_拉低并将数据写入HDATA数据总线,等候ADV212呼应写恳求ACK_有用。若ACK_有用,将WE_拉高,当WE_由低电平(有用)跳变为高电平(无效)时,ADV212对HDATA数据线进行采样。WE_拉高后,FPGA数据线和地址线均需坚持一个周期,以确保数据正确输入到ADV212中。

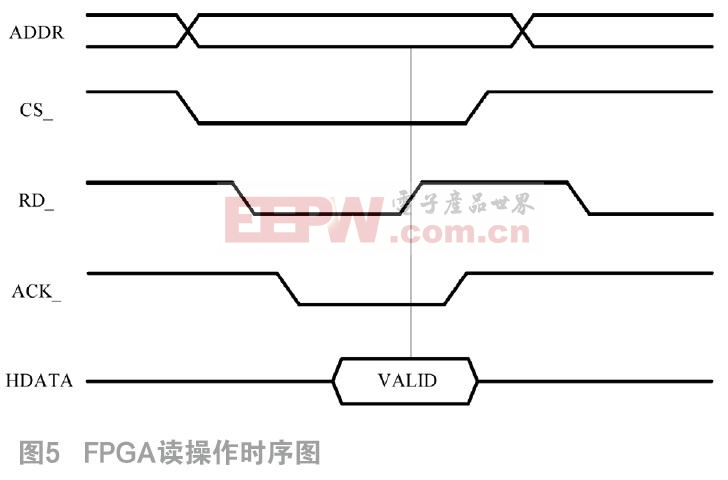

3.2 FPGA读操作

图5给出了FPGA从ADV212读数据的时序,RD_为读使能信号,其他信号与写操作相同。FPGA读操作详细流程如下:

首要,FPGA向ADV212宣布地址和片选使能,下一个时钟周期FPGA将写使能RD_拉低,等候ADV212呼应写恳求ACK_有用,此刻FPGA不采样HDATA数据总线上的数据。当ACK_有用时,将RD_拉高,RD_由低电平(有用)跳变为高电平(无效)的时间,FPGA对HDATA数据线进行采样。RD_拉高后,FPGA数据线和地址线均需坚持一个周期,以确保数据正确采样到FPGA中。

FPGA读写ADV212直接存放器和直接存放器的差异有两点:榜首,读写直接存放器时,FPGA接纳到ADV212握手信号ACK_需求一个时钟周期,而读写直接存放器时,FPGA需求一个或两个时钟周期;第二,FPGA读写直接存放器需求经过数据总线HDATA来发送和接纳直接地址,即完结一次数据的操作需求对HDATA进行两次操作,先发送或接纳直接地址,再发送或接纳直接数据。因而,FPGA操作直接存放器至少需求三个时钟周期,而操作直接存放器至少需求八个时钟周期。

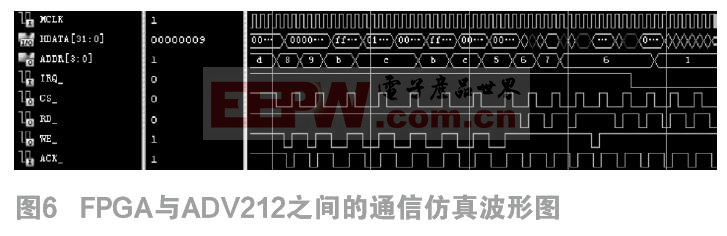

3.3 测验与仿真

根据Xilinx ISE树立FPGA工程,经过ISE自带的ISim仿真软件对体系进行仿真,如图6所示,HDATA为FPGA与ADV212之间的数据总线,其端口类型为inout型,即双向端口。当HDATA作为输入端口时,需求屏蔽HDATA对外输出值,行将HDATA的输出赋值为高阻态。当IRQ_为低电平时,标明FIFO中的数据已到达阈值,FPGA开端从地址1中读取FIFO的数据。

4 定论

JPEG2000算法可对视频进行高效紧缩,但是其算法复杂度高、硬件完结困难、完结的体系规划大等一系列问题约束了其在无人机遥感范畴的使用。ADV212专用芯片逐个处理了这一系列问题,该芯片体积小、功耗低、功能安稳,与FPGA一起建立视频紧缩处理体系可广泛使用于无人机遥感范畴。经测验,本体系作业功能安稳,具有紧缩比可调、实时性好、紧缩数据易康复和本钱低一级长处。

参考文献:

[1]谢清鹏.无人机序列图画紧缩办法研讨[D].武汉:华中科技大学, 2005.

[2]石迎波.MPEG-4视频编码体系的研讨与完结[D].西安:西安电子科技大学, 2005.

[3]李枫.根据H.264的航拍视频实时紧缩体系[D].北京:北京理工大学, 2011.

[4]Analog Devices Inc. ADV212 JPEG2000 Video Processor User’s Guide (Revision 1.1)[EB/OL].www.analog.com, 2006.

[5]刘春风,王惠平,潘利明.根据ADV212的高清视频紧缩体系规划[J].电子规划工程, 2010, 18(3), 65-67.

[6]薛旭成,张淑艳,李洪法,等.根据ADV202的遥感图画实时紧缩体系规划[J]. 微电子学与计算机, 2008, 25(5):197-199.

[7]Xilinx. Virtex-5 Family Overview [EB/OL]. www.xilinx.com, 2009.

[8]刘永征,刘学斌,胡柄樑,等.根据ADV212的JPEG2000静态图画紧缩体系规划[J].电子器件, 2009, 32(3), 504-508.

[9]Analog Devices Inc. ADV212 JPEG2000 Programming Guide (Revision 2.0) [EB/OL]. www.analog.com, 2007.

本文来源于《电子产品世界》2018年第6期第40页,欢迎您写论文时引证,并注明出处。