高速H桥上管驱动电路

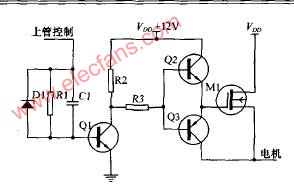

上例计划的速度瓶颈为光耦,假如不采用光耦那么操控信号的频率能够进步许多。经过实验,咱们开发了如下的高速型H桥上管驱动电路。计划如图9所示。

图中上管操控信号高电平为+l2 V,低电平为0 V。操控信号经过电阻电容和二极管电路加到Q1的基极,Q1的集电极输出作为

图9 高速H桥上管驱动电路

Fig.9 High Speed H-bddge Highside Driving

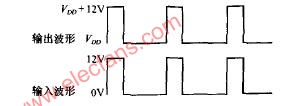

Q2,Q3组成的差动驱动电路操控信号,差动电路的输出作为Ml的驱动信号。Q2,Q3组成的差动驱动电路上端Q2接 +l2 V电源,下端Q3接到Ml的s极。当上管操控信号为低电平时,Q2导通,Q3截止,Ml的G极约为 D+l2 V,使Ml可顺利导通。Ml导通后,其D极和s极之间为通路,简直没有压降,此刻s极也为l,DD,则Ml的G和s之间的压差为l2 V,满意MOS管的导通条件,Ml可维持导通状况。当上管操控信号变为高电平时,Q2截止,Q3导通,使Ml的G和s极之间压差很小,不能满意MOS管的导通条件,则Ml截止。需求指出的是,当Q2导通M1没有导通的瞬间,Ml的G和s间压差为l,DD+l2 V,但由于MOS管的敞开时刻极短(几十US),Q2导通时,Ml简直一起敞开,使MJ的G和s之问的压差确保为12V(如图10)。

高速H桥上管驱动信号畸变

Fig.10 Signal Transmogrification of High Speed H-bddge

图9所示的上管驱动电路有很强的驱动才能,并具有很高的极限频率,运用这个驱动电路来驱动MOS管,能使MOS管的操控信号在较高的频率(20 k以上)下不失真。