运放的输入电容参数常常使人困惑或是疏忽。现在让咱们清晰这些参数怎样才是最好的使用。

运放电路的安稳性受输入电容的影响,它在反向输入端引进了一个相移,即抵达反向输入端的反应支路的推迟。反应网络受输入电容影响构成了一个不想要的极点。引进输入电容来核算反应网络的阻抗特性是确保运放电路安稳性的重要一步。可是,哪种电容有影响?差模电容?共模电容?仍是都有?

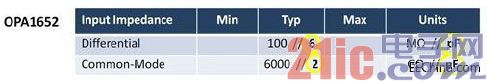

运放输入电容一般能够在输入阻抗参数一栏找到,差模电容和共模电容都有标明。

输入电容模型如图1:共模电容衔接各个输入端到地,而差模电容衔接在两个输入端之间。虽然双电源供电时没有地平面与运放相衔接,咱们能够把共模电容看作与负电源端相连,沟通等效到地。

在需求重视安稳性的高频区域,运放的开环增益低,在两个输入端之间实际上存在一个沟通电压。这将导致差模电容和共模电容一同效果, 然后改动反应信号的相位。因而,两个衔接反向输入端的电容相加,加上2pF的导线的杂散电容。这个总电容与并联阻抗反应网络(R1//R2)一同构成一个极点。

一般以为:此极点的频率应大于两倍的放大器闭环增益带宽。一个两倍闭环增益带宽上的极点将会削减电路的相位裕量约27°。关于大多数电路,大于两倍闭环增益带宽一般是能够的。有些使用需求更严苛的安稳条件或是驱动容性负载,或许会需求留更大的裕量。减小反应网络的阻抗,或是考虑在反应电阻上R2上加一个电容。

今日的通用型运放有着宽的带宽,从5MHz到20MHz乃至更高。本来适用于1MHz的运放反应网络现在或许会出现问题,所以这就需求您仔细查看和承认规划的安稳性。

SP%&&&&&%E仿真在查验输入电容的敏感性和反应阻抗很有协助,好的运放模型能用准确的输入%&&&&&%建模。1mV的输入阶跃信号的瞬态呼应测验信号不会引起过度的过冲和振铃现象。可是要记住,实际往往超出理论指导和仿真,这种类型的电路需求在终究的电路布局布线中作精密的调整。