这篇文章将评论两种可消除励磁电流失配和失配漂移影响的办法。榜首种办法是把内部多路复用器用于大多数集成式解决方案的软件办法。第二种办法是更改电路拓扑结构的硬件办法。

堵截励磁电流源

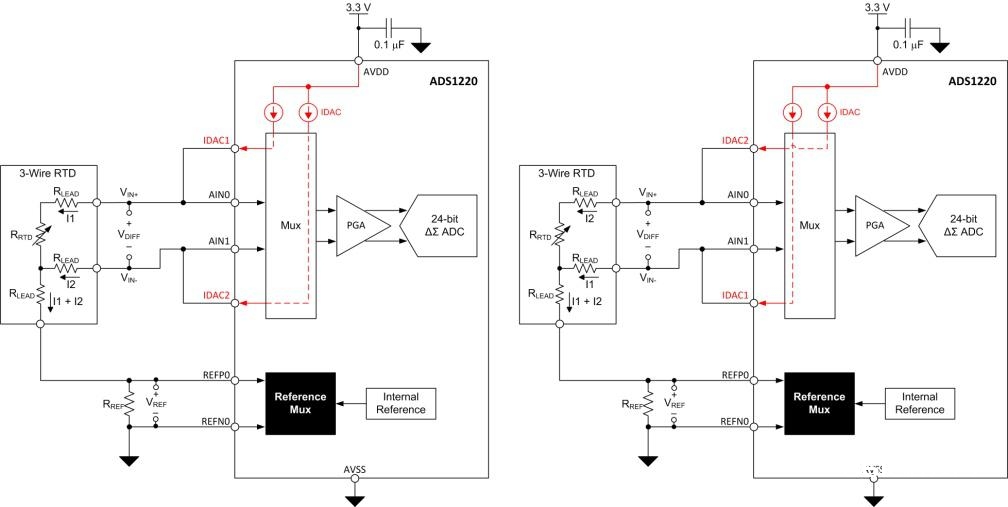

一种用来削减励磁电流失配所造成的差错的技能是让两个输入端之间的电流活动道路替换改动。这一般被称为“斩波”。把励磁电流注入到RTD电路,然后对它们进行交流,一起获取每种设置下的读数。两个读数的均匀值将不受两种励磁电流之间失配的影响。在大多数集成式解决方案中,可用内置多路复用器让到两个输出端的励磁电流活动道路替换改动来完成这一意图。图1展现了如安在该电路中堵截励磁电流。

图1:堵截励磁电流

当励磁电流被交流时,体系规划人员有必要等候,直到输入信号安稳,以便进行有用的丈量。趋稳时刻根据所挑选的模数转换器(ADC)以及已被装置启用的任何外部滤波器。切换多路复用器并等候获取读数会给丈量体系添加推迟,这在一些运用中或许是不受欢迎的。跟着计时变得越来越杂乱,把均匀成果转换成温度读数所需的数字处理算法也变得日趋繁琐。

具有高侧参阅的三线RTD丈量体系

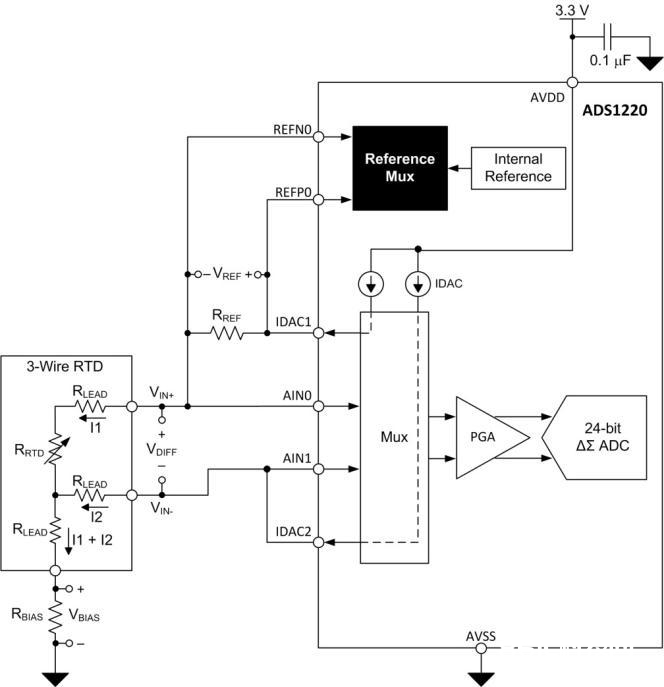

一种可堵截励磁电流的更有用代替办法是将参阅电阻器放置在RTD传感器的高侧(图2)。在该装备中,仅有一种励磁电流既流过参阅电阻器也流过RTD。第二种励磁电流只用于三线RTD引线电阻抵消。由于仅有一种励磁电流会发生参阅电压和输入电压,所以电流源失配和失配漂移将不再影响ADC传递函数。任何失配差错只能影响RTD引线抵消的有用性,这与本来的电路没有什么不同。

图2:高侧参阅电阻器装备

高侧参阅电路装备

经过将低侧参阅电阻器移动到RTD的高侧,全新的装备会带来一些附加的规划应战。首要,从RTD到接地有必要衔接一个附加电阻器RBIAS。跨RBIAS的电压VBIAS将在ADC的线性输入共模电压规模内改动RTD电压。完成这一方针的一起有必要使电流输出数模转换器(IDAC)输出端的电压低于其依从电压(compliance voltage)额定值。

方程式(1)诠释了适用于图2中电路的输入共模电压VCM。

适用于可编程增益放大器(PGA)的输入共模电压有必要坚持在产品阐明书扼要规则的规模之内。方程式(2)展现了最小共模电压VCM MIN的两个极限值。请运用VCM MIN这两个值中较大的一个。方程式(3)诠释了最大共模电压VCM MAX。

在IDAC输出端的电压不得超越依从电压,不然它们将无法正常发挥作用。方程式(4)诠释了IDAC的依从电压。

![]()

在这种电路装备中,最大IDAC输出电压在IDAC1处,用VIDAC1 MAX表明。用方程式(5)可核算出VIDAC1处的这种电压。

![]()

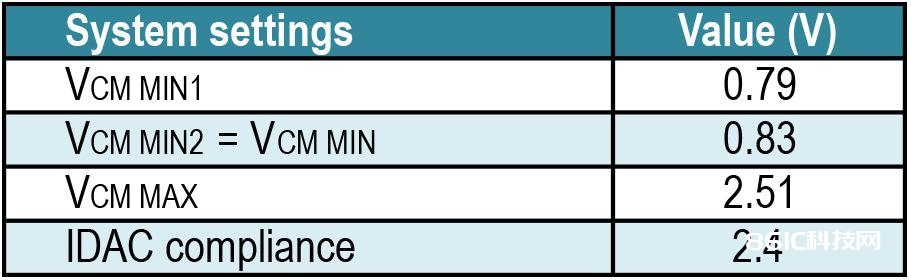

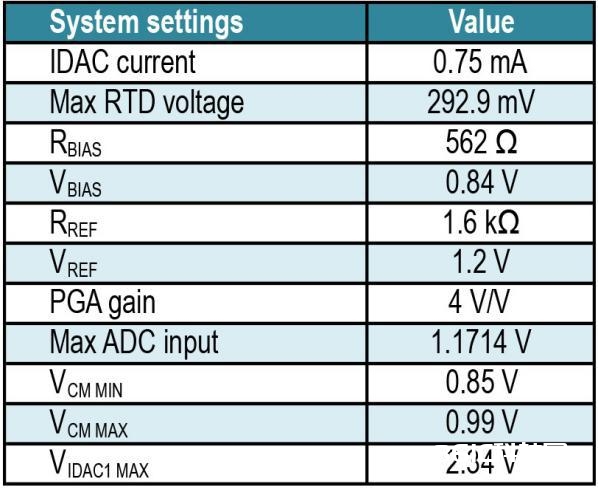

根据3.3V电源,表1展现了最小和最大共模电压以及IDAC依从电压的值。

表1:运用+3.3V电源时的共模和IDAC依从电压极限值

在高侧参阅装备中,IDAC输出端的电压会进步,由于添加了RBIAS —— 这会下降可用余量。为了满意IDAC电压顺度要求,或许需求经过调理IDAC电流或电阻器值来下降参阅或偏置电压。反过来,不同的IDAC电流或许需求调整PGA增益来坚持体系分辨率。

凭仗所引荐的高侧参阅解决方案,满意输入共模和IDAC依从电压极限值要求仍然是切实可行的。首要,挑选超越VCM MIN的偏置电压。这可最大极限地进步余量,以契合IDAC依从电压要求。然后,根据最大RTD电压挑选参阅电压和PGA增益设置,旨在最大极限地进步体系分辨率。

表2为运用+3.3V电源合理优化的高侧参阅电路列出了电路值,也列出了该电路中的VCM MIN和VCM MAX电压以及VIDAC1 MAX电压。请注意,最大ADC输入电压可充分利用大部分的VREF电压规模,一起保证不违背表1所列共模和IDAC依从电压极限值规则。

表2:适用于高侧参阅电路的电路参数

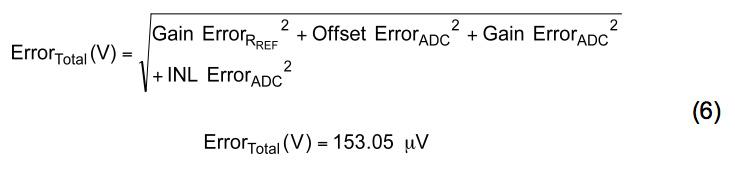

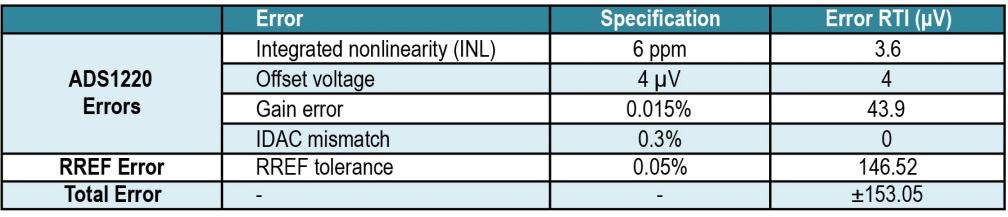

高侧参阅电路总差错

咱们剖析了由ADC和RREF发生的差错。尽管方程式和差错源坚持不变,但输入相关电压差错将根据电路中新挑选的IDAC电流和组件值而改动。表3汇总了差错源,并为25℃下的高侧参阅电路核算出了总或然差错。如图所示,可消除来自IDAC失配的差错。运用方程式(6)能核算出总差错。

表3:总差错(TA = 25°C)。

总输入相关电压差错可再次被转换为温度差错。

消除励磁电流失配差错的行动能使未校准温度差错削减67% —— 而在本来的低侧参阅装备中核算出的温度差错是1.589℃。

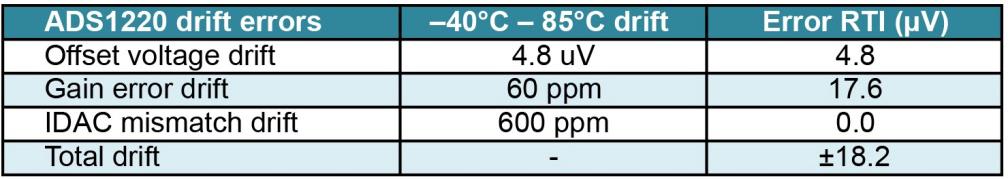

高侧参阅电路漂移差错

表4列出了ADS1220在体系工作温度规模(TA = -40°C至+85°C)内的温度漂移差错。如图所示,选用高侧参阅装备也可消除由IDAC失配漂移发生的差错。

表4:体系工作温度规模(-40°C至+85°C)内的温度漂移差错

消除IDAC失配所造成的差错的行动可明显下降输入相关漂移差错(本来是119.6μV,下降后仅有18.2μV)。现在,在-40°C至85°C的温度规模内,总漂移差错只会另发生±0.062°C的温度差错;而在低侧参阅电路中总漂移差错会另发生±0.306°C的温度差错。消除来自励磁电流失配的差错可削减对过温校准的需求或要求。

总结

在规范份额型三线RTD丈量电路中,无论是在室温下仍是在工作温度规模内,励磁电流失配一般都是最大的差错源。堵截励磁电流法是一种可在传统低侧参阅份额型RTD收集电路中削减励磁电流失配影响的简略办法。而将该电路改成高侧参阅装备的举办法既能消除励磁电流失配和电流失配漂移的影响,一起又能完成零丈量推迟并让附加组件数变得最少。只需契合输入共模电压和励磁电流依从电压极限值规则,高侧装备还可用于低电源电压。

这篇文章要点介绍了两种可削减或消除IDAC失配所造成的差错的解决方案。阐明了如何将该电路重新装备成高侧参阅电路,以便只用一个附加组件就能彻底消除励磁电流失配和失配漂移的影响。