三维大地电磁勘探技能是以面元为单位,多重量收集站为中心,多远参阅、互参阅和密布布点为特征来取得高质量的收集数据。户外施工时,为了坚持站点间同步地进行数据收集,一般选用GPS秒脉冲信号或恒温晶振的守时信号来同步各个收集站点。前者在恶劣的施工环境下常会因为各种搅扰而产生跳变,同步作用并不抱负。后者长期存在频率漂移,相同无法坚持长期的同步收集。

为处理以上问题,本文将GPS授时信号用于校准各站点的压控晶振,之后再运用晶振分频得到守时信号来同步各收集站点。这样不只克服了GPS授时信号易受外界搅扰的缺陷,也处理了晶振频率随时刻漂移的问题,能取得较为抱负的同步信号。为了使本地晶振长期地同步于GPS体系,就需求不断丈量GPS授时信号与本地晶振的分频信号的时刻距离,再依据丈量数据来校准和同步本地晶振。因而,时刻距离丈量的精确性是确保频率校准体系作业功能的要害。本文依据FPGA集成度高、高速和高牢靠性的特色,介绍了晶振频率校准体系在FPGA中的规划办法。体系的特色是运用FPGA内部进位逻辑结构推迟线来完成时刻距离丈量,大大进步了丈量分辨率,一起运用FPGA嵌入式软核处理器PicoBlaze对体系状况进行监控,并对丈量数据进行滤波处理,充分发挥了FPGA的集成优势。

1 体系规划

1.1 体系完成计划

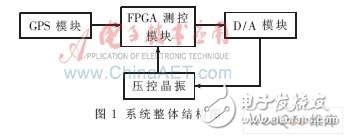

体系的原理如图1所示,首要由GPS接纳模块、FPGA测控模块、D/A转化模块和压控恒温晶振4部分组成。GPS接纳模块用于输出规范的1-pps脉冲信号,FPGA测控模块用于丈量本地晶振分频信号与1-pps信号的时刻距离,并将所测值在PicoBlaze中进行处理得到晶振输出频率相对于GPS体系的频率差错,最终将成果作为D/A转化模块的输入得到批改本地晶振频率的操控电压。

1.2 丈量原理

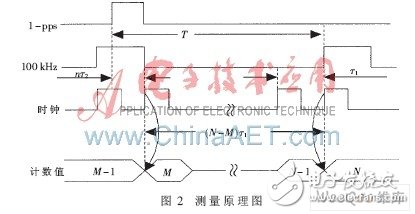

时刻距离在FPGA中的丈量的原理如图2所示,运用1-pps秒脉冲信号与本地晶振分频得到的100 kHz信号进行比对,得到的时差便是待测的时刻距离。因为只采样两者的上升沿间的时刻距离,所以用100 kHz分频信号替代1 Hz秒信号与1-pps比对,能够减小每次的丈量值,便利数据处理。需求留意的是晶振相对于1-pps的时差规模有必要在100 kHz信号的一个周期内,即该信号的频率决议了丈量量程的巨细,能够依据实践丈量需求来决议该信号的频率。

图2中T是待测的时刻距离,τ1是计数时钟周期,M是计数器在1-pps信号到来时的计数值,N是计数器在100 Hz信号到来时的计数值,nτ2是因为1-pps脉冲上升沿和计数时钟上升沿不一致所引起的丈量差错,这部分差错由内插推迟线来丈量。因为100 kHz信号由晶振分频得到,它和计数时钟同步,所以不会产生丈量差错。因而,待测的时刻距离能够表明为:

1.3 推迟线模块的规划

为了在短时刻内校准本地晶体振荡器,使之与GPS体系同步,有必要进步时刻距离的丈量分辨率,在规划中运用了时刻内插技能。其根本原理是运用多个延时单元结构推迟线,待测信号在推迟线中的传达信息便能够用来进行时刻距离丈量。推迟线的完成首要依赖于内插推迟单元延时的均匀性,内插推迟单元的单位延时决议了时刻距离丈量体系的分辨率。在FPGA中完成时刻内插,要害是在其结构的基础上运用内部已有资源结构出推迟线

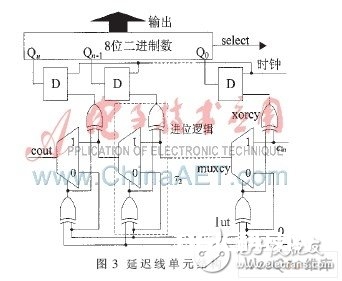

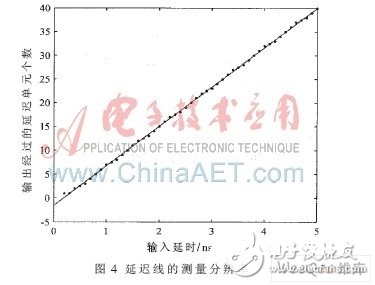

在XILINX公司FPGA的单元结构中,为了完成快速的数学运算设置了许多专用的进位逻辑资源。这些进位逻辑的延时很小,并且它们之间能够相互衔接组成进位线,能够运用这种专用的进位线作为推迟线来完成时刻内插。如图3所示,规划中运用了Spartan-3系列的FPGA中专用的进位逻辑逐一衔接组成推迟线,一个进位逻辑由查找表(LUT)、专用选通器(MUXCY)和专用异或门(XORCY)三部分构成。其整体结构上相似一个多位二进制加法器,两个输入的各位别离被置为1和0,进位信号没来时加法器各位均为1。当进位信号到来时就会沿着进位线一级一级地传输,加法器每一位输出值的改变就代表着信号的推迟信息,时钟前沿抵达时就能够将这些信息锁存入触发器中。图4是在一个时钟周期的仿真中推迟线单元输出通过的推迟单元的个数,进行直线拟合后的成果为:

所以推迟线单元的丈量分辨率约为1/8.257 4=0.121 ns.

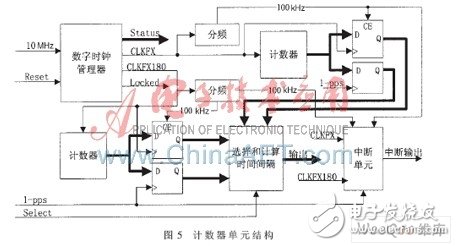

1.4 计数器模块的规划

图5简略描绘了计数器模块的根本结构。在计数器模块的规划中,运用了Spartan-3系列的数字时钟管理器,首要意图是将晶振时钟信号倍频后作为计数器的作业时钟,确保时钟周期小于推迟线的总延时。依据时序仿真所确认的推迟线单元的丈量分辨率及长度参数,将晶振频率倍频为200 MHz。

时钟前沿邻近计数器输出为亚稳态,假如1-pps信号刚好在这个时刻抵达,便会将过错的计数值锁存。为了处理这个问题,模块中运用数字时钟管理器输出相位差为180°的两路时钟,别离驱动两个计数器一起作业,这样不管任何时刻都能确保其间之一的输出为正确值,之后再对两者进行判别挑选。挑选信号由推迟线单元供给,通过核算1-pps信号通过推迟单元的个数来确认1-pps信号与时钟前沿的时差,然后输出select信号。

两个计数器进行循环计数,每个计数器都衔接着两组寄存器,其间一组将GPS秒脉冲信号作为作业时钟;另一组的时钟信号与对应计数器的时钟相衔接,且其使能端与100 kHz分频信号相连。当GPS秒脉冲和100 kHz信号到来时,便会将计数值送入相应的寄存器组。这样能够充分运用FPGA的大局时钟资源,使相应的寄存器组都运用同一时钟,确保寄存器触发的同步性。此外,运用循环计数的方法也处理了传统起停型计数器因为发动和中止信号不满足树立坚持时刻而形成计数器输出过错的问题。当1-pps信号与100 kHz信号的前沿都抵达后,中止单元将输出中止信号,用于告诉PicoBlaze软核读取丈量成果。

1.5 PicoBlaze软核规划

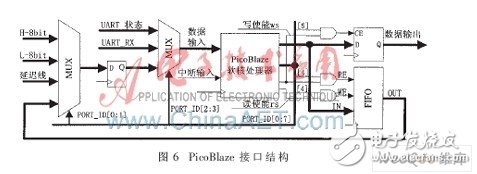

PicoBlaze是XILINX公司规划的8位微操控器软核,能够嵌入到Cool Runner II、Virtex-E、Virtex-II(Pro) 和 Spartan3(E)的CPLD以及FPGA中,规划灵敏便利。PicoBlaze的端口总线供给8位地址(PORT_ID)和读写选通讯号,最多能够完成256个输入和输出端口。接口规划如图6所示,PicoBlaze用来接纳推迟线模块和计数器模块输出的成果,一起读取异步串行操控器(UART)的数据和状况信息。其间异步串行操控器直接调用XILINX的IP核,与外部GPS模块进行串行通讯。

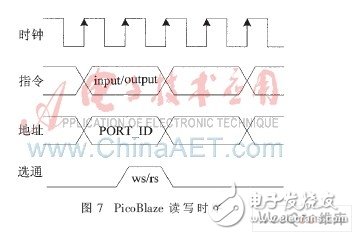

此外,为了完成对丈量数据的存储以便利数据处理,PicoBlaze衔接了一个FIFO数据缓冲,用于暂存未处理的丈量数据。如图7所示,PicoBlaze每个读写操作需求两个时钟周期,此期间地址总线一向处于有用状况,而读写使能信号仅在第二个时钟周期开端有用,所以地址总线上能够衔接恰当的逻辑电路进行地址解码。

规划中运用四路选通器别离衔接计数器模块、推迟线模块和FIFO缓冲的输出,其间因计数器模块中选用16位的计数器循环计数,为了与PicoBlaze输入匹配,须将计数值分两部分接到选通器。异步串行操控器的输出和状况信息别离接到三路选通器,剩下一路衔接四路选通器的输出。因为UART和PicoBlaze运用的时钟频率和丈量部分不同,为了进步数据传输的牢靠性,在选通器之间增加了流水线寄存器。

体系运转时PicoBlaze将对UART状况进行查询,当检测到有GPS串码数据时便开端读取其串码信息。GPS串码信息用于剖析当时GPS的状况,假如检测GPS模块现已确定卫星,则体系开端进行丈量和校准作业。

2 丈量数据处理

依据丈量到的时刻距离数据,依照公式:

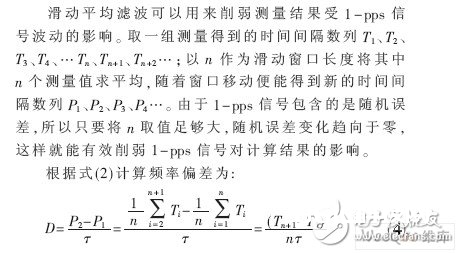

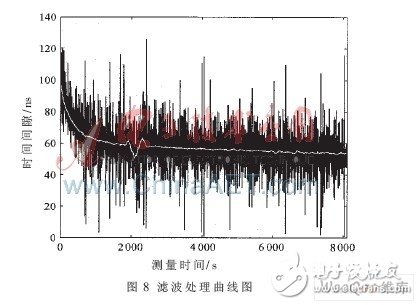

能够核算出晶振信号相对于GPS的频率差错,其间T1和T2别离是丈量部分相隔采样时刻τ前后输出的时刻距离丈量值。依据频率差错的巨细,再结合晶振的压控灵敏度,便能够完成对晶振的输出频率进行操控和批改。但GPS信号在传输过程中简略遭到外界影响,GPS模块输出的1-pps信号是一个动摇信号,其短期稳定性较差。图8的黑色曲线是运用本体系丈量得到的本地晶振相对于GPS体系的时刻距离曲线,运用这些数据核算得到的频率差错也会遭到影响而产生动摇,所以不能直接运用。

从式(4)能够看出,核算频率差错只是需求窗口的端点处的丈量值而不受窗口内的丈量值影响。在实践应用时,核算量很小并且简略,便利运用PicoBlaze软核处理器来完成。PicoBlaze衔接的FIFO数据缓冲用来存储滑动窗口中的丈量数据。当存储到达预设的窗口长度时,将从FIFO中次序读取出从前的丈量值,合作当时丈量值,依据式(3)核算出频率差错。图8的白色曲线是增加滤波处理后体系输出的时刻距离,比照能够看出滤波对颤动和较大的跳变点都有很好的抑制作用。

本文介绍的晶振频率校准体系运用GPS模块输出的规范秒脉冲信号对本地晶振频率进行校准。本规划依据FPGA内部进位逻辑资源完成了高分辨率的时刻距离丈量单元,并合作滑动均匀滤波法运用PicoBlaze处理器对丈量的时刻距离数据进行实时处理。不只能够精确地丈量本地晶振分频信号与GPS秒脉冲信号之间的时刻距离,并且降低了GPS秒脉冲动摇对丈量成果的搅扰,为校准晶振频率供给牢靠的批改数据。此外,体系测控部分彻底在FPGA中完成,利于进步丈量分辨率,减小体系体积,进步体系运转的稳定性。本体系不只能够用于大地电磁三维收集站,还能够在其他对频率精确度有要求的仪器中运用。