1 导言

HDLC(High Level Data Link Control)协议是通讯领域中运用最广泛的协议之一,它是面向比特的高档数据链路操控规程,具有过失检测功用强大、高效和同步传输的特色.目前市场上有许多专用的HDLC芯片,但这些芯片大多因寻求功用的齐备,而使芯片的操控变得复杂.实践上,关于某些特别场合的特别用处(如手持式设备),咱们只需挑选HDLC协议中最契合体系要求的部分功用,规划一种功用相对简略、运用灵敏的小型化HDLC协议操控器.另一方面,跟着深亚微米工艺技能的开展,FP-GA(Field Programmable Gate Array)芯片的规划越来越大,其单片逻辑门数已超越上百万门.一起它还具有规划开发周期短、规划制作成本低、可实时在线查验等长处,因而被广泛用于特别芯片规划中.本规划中选用Altera公司的FLEX10K芯片EPF10K20RC240-3来完结HDLC协议操控器.

2 HDLC协议简介

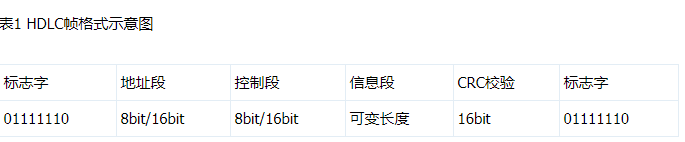

在HDLC 通讯方法中,一切信息都是以帧的方法传送的,HDLC帧格局如表1所列.

(1)标志字 HDLC协议规矩,一切信息传输有必要以一个标志字开端,且以同一个标志字完毕,这个标志字是01111110.开端标志到完毕标志之间构成一个完好的信息单位,称为一帧.接纳方能够经过查找01111110来探知帧的开端和完毕,以此树立帧同步.在帧与帧之间的空载期,可接连发送标志字来做填充.

(2) 信息段及“0”比特刺进技能 HDLC帧的信息长度是可变的,可传送标志字以外的恣意二进制信息.为了保证标志字是绝无仅有的,发送方在发送信息时选用“0”比特刺进技能,即发送方在发送除标志字符外的一切信息时(包含校验位),只需遇到接连的5个“1”,就主动刺进一个“0”;反之,接纳方在接纳数据时,只需遇到接连的5个“1”,就主动将这以后的“0”删掉.“0”比特刺进和删去技能也使得HDLC具有杰出的传输通明性,任何比特代码都可传输.

(3) 地址段及操控段地址字段为8位,也能够8的倍数进行扩展,用于标识接纳该帧的栈地址;操控字段为8位,发送方的操控字段用来表示命令和呼应的类别和功用. (4) CRC校验 HDLC选用16位循环冗余校验码(CRC-16)进行过失操控,其生成多项式为 x16+x12+x5+1 HDLC过失校验指对整个帧的内容作CRC循环冗余校验,即对在纠错范围内的错码进行纠正,对在校错范围内的错码进行校验,但不能纠正.标志位和按通明规矩刺进的一切“0”不在校验的范围内.

3 HDLC协议的FPGA完结

依据FPGA完结的HDLC协议操控器包含接纳和发送两个模块,其整体结构如图1所示. 发送端先将待发送的并行数据进行并/串转化,然后由体系主动完结CRC编码、“0”比特刺进和标志字刺进,再将处理后的数据按同步串行传输方法发送;接纳端先接纳同步串行数据,然后由体系主动完结标志字的检测、去“0”及CRC校验,再将同步串行数据转化成8位并行方法输出.整个体系收发端运用同一个大局时钟.下面分别对要害部分进行介绍.

3.1 并/串及串/并转化模块

数据发送时,为了滑润处理机和HDLC协议操控器之间的数据传输速率,发送端配有一个25×8的FIFO作为两者的接口模块,该模块可将数据总线送入的并行数据转化成串行数据输出.相同,接纳端也配有一接纳FIFO,可将接纳到的数据进行串并转化并送入数据总线.

3.2 CRC校验

HDLC协议运用循环冗余校验,在发送端对信息进行CRC编码,其生成多项式为 g(x)=x16+x12+x5+1 CRC校验模块实践为依据生成多项式所规划的编码电路.依据循环体系码编码原理,该编码电路实践上是乘x16除g(x)的电路,其示意图如图2所示.电路的作业进程如下:

(1)16级移位寄存器的初始状况全清零,门1开、门2关,然后进行移位.信息位移入编码电路后,一方面经或门输出,一方面则主动乘以x16后进入除g(x)除法电路,然后完结乘x16除g(x)的功用;

(2)信息位悉数移入编码电路后除法完结,此刻16位移位寄存器中的内容便是除法的余式的系数,即校验元;

(3)门1关、门2开,再经过16次移位后,把移位寄存器的校验元悉数输出;

(4)门1开、门2关,送入第二组信息组重复上述进程. CRC编码器的中心VHDL源代码如下:……

D0 <=din xor D(15);

for i in 0 to 3 loop

D(i+1)<=D(i)

end loop;

D(5)<=D(4) xor D(15) xor din;

for i in 5 to 10 loop;

D(i+1)<=D(i);

end loop;

D(12)<=D(11) xor D(15) xor din;

for i in 12 to 14 loop

D(i+1)<=D(i);

end loop;

……

发送端经过上述的CRC编码电路发生16比特的校验位.接纳方经过CRC译码查验该帧信息是否传送犯错.在满意体系要求的情况下,CRC译码只检错,不纠错.其功用示意图如图3所示. 输入信息经过16比特的移位寄存器后,一路作为数据信息输出,另一路流入CRC编码器对信息进行编码,并发生16比特校验位.当信息位悉数移出后,16比特移位寄存器中的信息即为发送端发送的16位CRC校验位,CRC编码器(16Bit)的内容为接纳到的信息依据生成多项式g(x)所生成的16比特校验码.然后将两个寄存器进行比较,假如内容相同,阐明信息传送正确;不然报错,丢掉该帧. 3.3 “0”比特刺进及删去模块发送端信息经CRC编码后,要进行插“0”操作,即遇到接连的5个“1”时在这以后刺进一个“0”;相同,接纳端同步树立后提取出的信息要去“0”,即遇到接连的5个“1”时要将这以后的“0”去掉. 去“0”模块的VHDL代码如下:……

if din=“1” then

if cnt=5 then

cnt:=0;

end if;

cnt:=cnt+1;

else

cnt:=0;

end if;

if cnt=5 then

zero del<=′0′;

else

zero del<=′1′;

end if;

……

去“0”模块的功用仿真波形如图4所示,其间din是提取同步后的信息,clk是信息时钟,dout是去“0”后的信息,clk out是去“0”操作后的信息时钟.从图4中可看出,去“0”前的信息为“1111101”,经过去“0”操作后,信息为“111111”,将5个“1”后的“0”去掉了.

4 完毕语

本文提出了一种依据FPGA的HDLC协议操控器规划计划,并运用Altera公司的FLEX10K芯片EPF10K20RC240-3来完结,占该芯片内部单元的70%左右.实践标明,该协议操控器操作简略、运用灵敏,能够很好地运用于各种小型通讯设备.

本体系的硬件完结选用VHDL规划,经过树立VHDL行为模型和进行VHDL行为仿真,能够及早发现规划中潜在的问题,缩短了规划周期,提高了规划的可靠性和功率.

责任编辑:gt