导言

Adaboost算法是Freund和Schapire于1995年提出的,全称为Adaptive BoosTIng.它是BoosTIng算法的改善,意为该算法经过机器练习与学习不断自适应地调整假定的错误率,这种灵活性使得Adaboost算法很容易与实践使用联系起来。2001年,微软研究院的P.Viola提出了依据Haar特征的Adaboost算法,创造性地将积分图的概念引进到人脸检测的特征核算傍边,因为此算法使用了很多尺度纷歧的矩形作用来表征人脸。而且该算法中用以检测人脸的分类器是选用的级联结构,依照由弱到强的次序安排的,其长处在于依照核算概率,在图画检测的一开端就能够将大部分不包括人脸的区域扫除在外,省去了后边核算负载更重的检测过程,以此到达检测速度进步的意图。经过实践测验,P3 700MHz的处理器对352*288的图画进行检测的速度为15帧/秒。可是假如在嵌入式渠道上运转的话,纯软件的检测速度则为2帧/秒。本规划将这种快速检测算法转化成了一种并行处理图片像素点的硬件结构,能够大幅度进步图画中的人脸检测速度。

方针渠道

Virtex5系列FPGA是Xilinx最新一代依据65nm的FPGA产品。比较上代产品,速度均匀进步30%.其改善后的六输入的查找表(LUT)和新式对角互连结构,减少了逻辑层次,增强了结构块之间的信号互连。

本文体系的完结首要用到了两类逻辑资源来优化体系功用:DSP48E Slice:25×18位二进制补码乘法器能发生48位全精度成果。此功用单元还能够完结许多DSP模块如乘累加器、桶形移位器、宽总线多路复用器等。

Block RAM:可装备成2个18 Kb或1个36 Kb的Block RAM,也能够装备为双端口RAM或FIFO,并供给了ECC校验查看功用,进步了体系可靠性。

硬件体系结构

本文选用了一种像素积分单元阵列的结构来完结对图画进行人脸检测的并行性处理[4,5]。该阵列的核算目标为Haar特征。该特征被笼统为各种尺度巨细的矩形。一系列的矩形组合起来即被用来表征人脸。是非矩形内像素的灰度值经过加权求和后即为该特征的特征值。积分图ii的界说是:

![]()

其间ii(x, y)是积分图在点(x, y)处的积分值,i(x‘, y’)是图画在点(x‘, y’)处的灰度值。使用积分图能够快速核算矩形S的灰度和,即Sum=A+D-B-C,其间A、B、C、D是积分图中矩形极点对应的积分值。

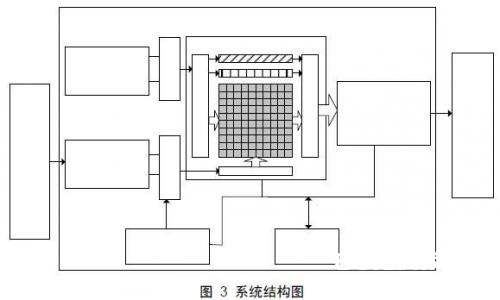

体系结构框图如图3所示,整个体系的作业流程和各模块功用论述如下:

图画输入模块:体系输入端外接一个模仿摄像头,收集到的图画信号经过板上的A/D芯片转化成ITU-R BT.656 (YCrCb 4:2:2,8位数据宽度)分辨率为352×288(CIF)的图画格局。该模块的作用为当检测操控状态机发送初始化信号后,经过I2C总线装备A/D芯片完结信号转化。别的,因为BT.656格局混合包括了视频的场信息和图画数据,因而该模块还要从BT.656信号中提取出图画数据存放到图画RAM中。针对该完结,RAM巨细为8位宽度,深度为101376.

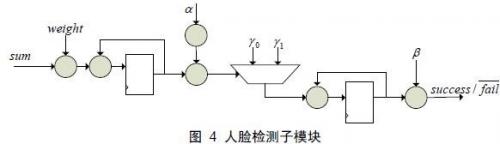

像素积分阵列:像素积分单元阵列是本体系中进行快速人脸检测的中心处理模块。在将图画进入片内RAM后,体系将选用20×20的移动窗口对整幅图画进行扫描处理。每个周期的开端阶段,检测窗口包括的一行(20像素)的灰度值由底部进入积分阵列,积分阵列上部输出按从左至右方向的行像素值的积分和,右部则输出每行按从左至右方向的像素值的平方和。阵列中的灰色方格则保存了检测窗口对应原始图画部分的像素积分值。阵列中的带竖线和右斜线的方格表明了存储特征所包括的矩形权重和特征相似度等参数的流水线。在整个扫描窗口的像素积分值都进入此阵列后经过左边编码模块的编码操控后,从阵列的右侧能够得到当时一级分类器所包括的矩形的像素灰度值。此灰度值被送到右侧的检测模块(如图4):首要会和当时一级分类器中对应特征的权重weight相乘,然后将乘积进行累加后即得到当时区域对应此特征的特征值。接着这个值会与分类器中的特征阈值a比较,然后挑选对应的特征相似度γo(大于等于a )或许γ1 (小于a ),此相似度值也将被累加,当该级分类器中所包括的悉数特征的特征相似度都累加结束后会与终究的该级的检测阈值β比较。比较后的成果显现了该窗口区域是否包括了人脸,1即为包括,0即为不包括。假如包括人脸,此模块还将把当时检测到的人脸的区域信息(包括矩形的左上角开始坐标和矩形长、宽)保存在一个专用的存储区域,以用于后边的成果输出。

人脸信息处理单元:像素积分单元阵列检测到人脸后,此单元将首要保存检测到的人脸方位信息。好像检测阶段中分类器中的特征包括的矩形表达式相同,人脸方位信息也是由开始点坐标和矩形的长、宽组成:(x, y, width, height)。接着依据此信息操控后一级的视频输出模块用以显现人脸。读取(x, y),在图画RAM中检索到对应人脸的开始点的地址,往该地址中写入像素值0.接着纵坐标不变,延x轴方向只至x+width-1的点的像素值均更新为0.然后是制作人脸的纵向鸿沟。坚持横坐标为x+width-1,y坐标顺次增1只至y+height-1,将此列对应点的像素值更新为0.后边再依照相似的办法折回完结余下的人脸鸿沟的标识。此刻存放在RAM中的检测后的图画数据被送入到视频输出模块,该模块以800×600的分辨率将最终的检测成果显现在VGA屏幕上,在屏幕显现中,被黑色方框围住的区域便是人脸。

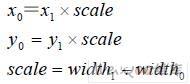

图画缩放单元:此模块用以检测图画中大于20×20像素的人脸。本文选用的是固定巨细为20×20的移动窗口,以从上至下,从左至右的方向遍历扫描整幅图画来检测人脸。对原始图画数据扫描完一遍后,能够直接检测出图画中巨细在20×20以内的人脸。然后有检测操控状态机担任发动该单元模块,以必定系数对原始图画进行缩小处理。处理办法选用的是依照缩小份额生成提取像素点的地址,并将这些像素点从头组成缩小后的图画。其核算公式如下所示,其间( x0 ,y0 )和(x1 , y1)分别为原图画和缩小后的点坐标,scale参数为查表所得:

测验成果该体系在Xilinx ML509开发板上进行测验,该开发板上选用了一块XC5VLX110T-FF1136的FPGA芯片,测验计划为:将摄像头实时收集到的图画送进体系视频输入模块,然后经过拨码开关来操控板上的AD9880芯片转化为384×288的8位灰度图送入中心检测模块检测并输出在VGA显现器上。整个体系逻辑资源占用状况如表1所示。表2为最终体系能够运转的最高频率。

定论

本文立异点在于选用了一种像素积分单元阵列结构,能够对Adaboost算法中的Haar特征进行并行处理。结合Virtex5渠道丰厚和特别结构的逻辑资源,得到了抱负的功用,乃至现已能够和高功用的PC渠道混为一谈。从成果中能够看到,本体系只使用了部分资源。经过在FPGA芯片内部例化更多的处理单元,还有进一步增大并行性以获得功用进步的空间。

责任编辑:gt