传统的模仿锁相环(APLL)有较短的确守时刻,能够确保参阅时钟源和输出时钟的稳态相差。但其中心频点受VCO的约束而规模较小,环路带宽较宽;当参阅源呈现瞬断或许参阅时钟源切换时,VCO输出时钟频率会呈现较大的相位瞬变。

跟着数字电路技能的开展,特别FPGA技能的遍及使用,选用FPGA完成全数字锁相环(ADPLL)的使用越来越多。ADPLL规划简略、使用便利。本文介绍一种选用FPGA完成的ADPLL,该ADPLL用于发生SDH设备的外同步输出时钟。该锁相环具有传统的APLL的抓获时刻短、有安稳的相差的长处,一起也具有DPLL的中心频点可编程调整、能够完成滑润源切换的长处。

1、体结构及根本作业原理

外同步输出时钟发生的全体结构框图如下图1所示:

图1 ADPLL的全体结构框图

计划的主体部分为一个ADPLL。ADPLL和传统的PLL相同,环路主要由鉴相器(PD)、滤波器(LF)、数字操控时钟输出(DCCO)3部分组成。PD将参阅时钟clk_ref和clk_div(由clk_out进行N分频得到,环路确定后频率和clk_ref一起)进行相差辨别,输出up或许down信号指示时钟相位的超前、滞后联系。LF模块将up和down,用高速时钟clk_h进行相差计数,并选用数字滤波算法,给出相位调整指示adjust。DCCO模块,由高速时钟clk_h在相位调整指示adjust的效果下进行受控分频得到。环路经过负反馈调整,完成输出时钟clk_out和clk_ref的同步。

ADPLL作业的高速时钟(即图1中的clk_h)选用SDH设备的体系时钟155.52MHz,输出的外同步时钟clk_out频率为2.048MHz,DCCO模块选用受控小数分频规划。外同步时钟依据用户需求能够从多路参阅源中任选1路,由参阅源挑选模块完成。规划中,一切参阅源的时钟频率都分频到100Hz进行鉴相,即clk_ref和clk_div的频率都为100Hz。

2、 全数字锁相环路的具体规划完成

输入的各路参阅源的相差是不确定的,当参阅源切换时,挑选后的信号clk_ref必然会呈现相位的骤变;这种相位的骤变最大或许达半个clk_ref周期,即源切换后瞬间,clk_ref和clk_div的相差最大或许达±5ms。源切换发生的相位跳变,在APLL中会导致压控电压骤变,导致输出时钟的频率骤变,无法完成滑润源切换。而在DPLL中,能够经过调整滤波算法,逐渐改动压控电压,确保输出时钟频率的缓慢改动。

这儿规划的ADPLL,咱们经过2个方面来确保滑润源切换环路:1、负反馈时钟选用初始受控分频规划,当参阅源切换时,经过受控分频确保了clk_ref和clk_div的初始相差小于半个clk_out时钟周期。2、经过环路滤波算法,逐渐改动adjust的调整频率,确保源切换时输出时钟频率滑润改动。

2.1 初始受控分频规划

当源切换时,输出至少1个clk_div时钟周期的1电平信号ref_change,指示当时参阅源进行了源切换。当ref_change为1时,clk_div信号从头由clk_out在clk_ref的受控下分频得到;一起,屏蔽掉该鉴相周期的up和down输出,防止adjust呈现误调整。

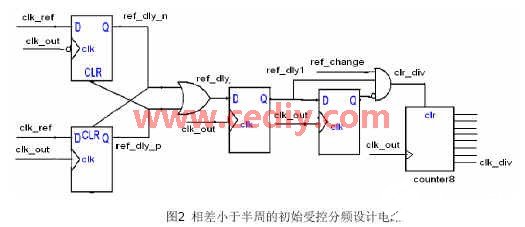

选用如下图2的电路逻辑规划初始受控分频,能够确保初始分频后,clk_div和clk_ref的相差小于半个clk_out时钟周期,即小于244ns。清零信号clr_div只在ref_change为1时使能;锁相环正常盯梢状况下,clk_div为自在分频得到。

图2 相差小于半周的初始受控分频规划电路

在参阅源切换后,clk_out与clk_ref的初始相位联系有2种或许:clk_out超前或许滞后。当clk_out相位超前时,则上图中ref_dly_n将clk_ref的沿踩中;当clk_out相位滞后时,则上图中ref_dly_p将clk_ref的沿踩中;2种状况,最终都在下同一个clk_out周期取clk_ref的上沿,然后进行受控分频。按此规划的受控分频规划,能够确保初始受控分频后,发生的clk_div和clk_ref的相差总在半个clk_out周期以内。

2.2 环路滤波规划

这儿,咱们彻底选用数字电路逻辑完成环路滤波算法。环路滤波规划中,相位调整指示adjust由频率调整操控adjust_f和相位调整操控adjust_p两部分一起组成。

频率调整操控adjust_f的发生:

1)、锁相环开端作业时的初始值adjust_f[0]=0。

2)、依据当时鉴相周期鉴出的相差phase[n](用155M时钟对up和down进行计数归纳得到),和上一个鉴相周期鉴出的相差phase[n-1]进行比较:

当(phase[n]-phase[n-1]) 》 1,则adjust_f[n]=adjust_f[n-1] – 1;

当(phase[n]-phase[n-1]) 《 -1,则adjust_f[n]=adjust_f[n-1] + 1;

其他状况,adjust_f[n]=adjust_f[n-1],坚持不变。

3)、adjust_f[n]的规模操控在±127以内。

4)、当|phase[n]-phase[n-1]|大于1000,即相差突跳了6.4us时,阐明参阅源或许呈现突跳,此刻输出源颤动指示,从头进行初始受控分频。

频率调整操控,确保了输出时钟频率和参阅源频率的一起。该滤波规划,确保了adjust_f的缓慢改动;参阅源切换后,adjust[n]的调整也是在之前基础上逐渐改动,这牢靠的确保了输出时钟频率的滑润。

相位调整操控adjust_p的发生:

1)、依据当时鉴相周期鉴出的相差phase[n]来给出相位调整操控:

phase[n] 》 0,则adjust_p[n] = -1;

phase[n] 《 0,则adjust_p[n] = 1;

其他状况,则adjust_p[n] = 0;

相位调整操控的效果下,牢靠的确保了确定状况下的稳态相差小于1个clk_h时钟周期。

adjust[n] = adjust_f[n] + adjust_p[n]。在环路正常盯梢或许源切换的过程中,|adjust[n] – adjust[n-1]|总是会小于2,即输出时钟的频率骤变小,确保了输出时钟clk_out的频率安稳。

adjust》0时,DCCO需求进行相位正调整;而当adjust 《 0时,DCCO需求进行相位负调整。需求调整的adjust,在下个鉴相周期(100Hz)中平均分配。因为adjust调整值最大不超越128,所以adjust的调整频率最大为12.8KHz。

2.3 DCCO的规划完成

155.52M为2.048M的75.9375倍,为非整数倍;一起DCCO受adjust的调整操控。即clk_out需求由clk_h进行小数受控分频得到。

注意到2.048M的76倍频为155.648M,和155.52M相差128K。所以2.048M能够这样发生:155.52M时钟在76分频的过程中,每128K时钟周期固定进行相位负调整1次。明显,固定相位调整频度远大于 adjust相位调整频度。

小数分频的固定相位调整规划和adjust的相位调整操控能够归纳起来考虑:1、每128K频率的固定相位负调整,和adjust的正调整操控信号都在128K时钟信号的上沿方位进行。当需求进行一次正相位调整时,直接去掉1次固定负调整即可到达意图。2、而adjust的负调整在128K时钟信号的下沿方位进行,和固定负调整错开,防止某一个clk_out周期进行了2次负调整。

经过这种归纳调整操控后,恣意一个clk_out时钟周期,或许为clk_h的76分频、或许75分频。这样,发生的clk_out时钟的cycle-cycle固有颤动为1个clk_h周期(p-p峰峰值),即6.4ns。

3、 实践使用及锁相环特性测验

3.1 规划实例

因为该ADPLL一起具有滑润源切换及稳态相差的长处,咱们在开发SDH设备的时钟板时,直接选用该计划规划完成2.048M外同步输出时钟。该规划中,FPGA芯片选用了Altera公司供给的EP1C4F400芯片,该ADPLL部分总逻辑资源占用约300个LE(1个LE包含1个4输入的查找表和1个D触发器)。

3.2 环路特性剖析及实践测验定论

1)、频率抓获带

也称为牵引规模。即clk_h和clk_ref频率误差到环路无法确守时的最大值。

依据环路滤波规划,每100Hz最大调整128个clk_h周期,即锁相环路最大可调整的频率为100Hz×128×6.4ns= 81.92ppm。即环路的牵引规模为±81.92ppm。

选用如下图5所示的办法进行牵引规模的测验:

SDH设备的体系155.52M时钟,经过一路APLL和时钟基准源坚持同步。环路的100Hz时钟由信号发生器发生。用示波器丈量锁相环路的clk_ref1和clk_out的确定状况;经过信号发生器逐渐改动参阅时钟clk_ref1的频偏, 调查能够确定的最大频偏。测验得到的牵引规模为±80ppm左右。

2)、稳态相差

屡次复位锁相环路后,用示波器丈量环路确定状况下图5中的clk_ref1和clk_out时钟相差,均在±12ns以内。

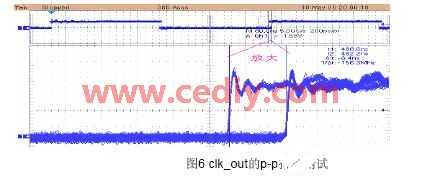

3)、输出时钟的cycle-cycle颤动

依据2.3节的剖析,输出时钟颤动的p-p为6.4ns。选用示波器测验2.048MHz输出时钟,如下图6所示,颤动的峰-峰值便是6.4ns,和剖析一起。

图6 clk_out的p-p颤动测验

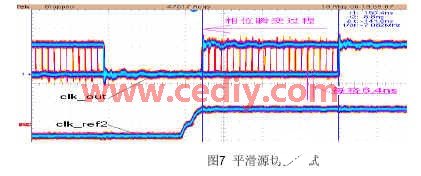

4)、滑润源切换

按图5,给锁相环路供给2路同频不同相的参阅源clk_ref1和clk_ref2。用clk_ref2作触发源,示波器设置为长余辉和快俘的形式;经过CPU接口将环路的参阅源由clk_ref1更改为clk_ref2。经过示波器能够看到参阅源切换过程中clk_out的相位瞬变如下图7所示:

从图7中能够看到,源切换过程中相位瞬变的起伏小于半个2.048M周期,这儿为140ns。瞬变过程中,输出时钟和参阅源的相差按6.4ns的粒度,逐渐调整,直到最终确定。

从上述测验成果来看,输出时钟的稳态相差较小,Cycle-cycle颤动较小,有较宽的牵引规模,能够完成滑润源切换,彻底满意SDH设备外同步输出时钟的要求。

4、 总结

本文规划的全数字锁相环独到之处在于:该锁相环具有数字锁相环的滑润源切换、牵引规模可调等长处,一起还具有模仿锁相环的快速抓获和有稳态相差等长处。经过实践验证,使用该锁相环发生的SDH设备外同步输出时钟,能够很好的完成滑润源切换,抓获时刻快,一起确保了环路的稳态相差,各项时钟目标杰出。

责任修改:gt