4.3 AD8302输出信号调度电路

该信号调度电路首要是对AD8302的输出电压进行有源低通滤波处理。有源低通滤波器除了滤除搅扰信号外,还起着信号阻抗匹配和信号电流扩大的效果。

本系统中运用了六通道的模数转化器ADS8364,其输入阻抗为20,AD8302的输出电压规模在0V~1.8V,由于ADS8364的输入电流最大体到达90mA,而AD8302的输出电流的最大值为8mA,远小于90mA,所以不能直接对AD8302的输出电压进行模数转化,需求加运放进行电流扩大。

本系统选用有源低通滤波器来完结滤波和电流扩大,图4-1中的LP3即为该有源低通滤波器。

LP3有源低通滤波器选用了运算扩大器AD8532。AD8532为窄带运算扩大器,其带宽为3MHz,能够有用的满意本系统有源低通滤波器的带宽要求;AD8532内部集成了两个运算扩大单元,运用一片即可构成两个有源低通滤波器,然后能够对AD8302的两个输出电压进行滤波;AD8532具有高达±250mA的输出电流,其后接ADS8364时,输出电压可最大为5V,能够满意电流扩大的功用要求。

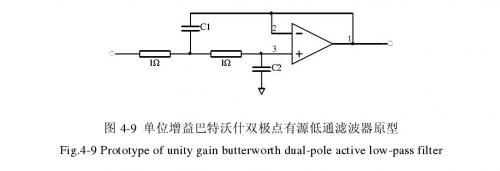

有源滤波器类型的挑选[26]首要考虑使通带坚持平整,以确保检波和鉴相的精度。因此运用了巴特沃什型有源滤波器,该巴特沃什有源滤波器的增益为1,具有双极点,其原型如图4-9所示。

图中1为单位电阻,C 1和C 2依照巴特沃什有源滤波器的查找表得:C 1 =1.414,C 2 =0.7071。

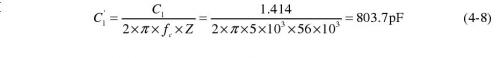

对所规划的滤波器功用好坏运用频率特性测试仪实践调查,依据调查成果改善滤波器,直至满意要求。首要,由通带为2KHz,假定-3dB带宽为f c =5KHz,选取阻抗标度系数Z=56×10 3,则图4-9中的两个电阻都为56K,由C1和C2的计算公式可得其值,见式(4-8)和式(4-9)。

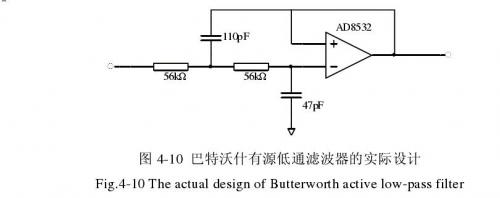

选用以上元件规划该有源低通滤波器,运用频率特性测试仪进行功用调查,发现2KHz处具有显着的衰减,故对C1、 C2需求进行调整,考虑到该低通滤波器首要是对较高频率重量进行按捺,且对带宽的要求不甚严厉,为了尽量坚持通带的平稳,可扩大其一3dB带宽,终究得该有源低通滤波器如图4- 10。

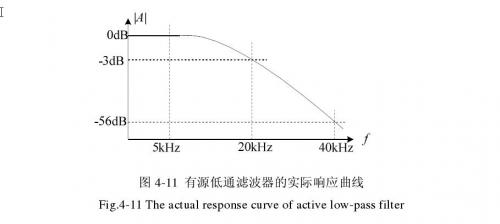

该有源滤波器的实践频率响应特性如下图4-11所示,其一3dB带宽为f c =20KHz,0~5KHz波形根本不发生改动,40KHz时的衰减可达56dB。

AD8302经过该巴特沃什有源低通滤波器后,信号得到了电流扩大和高频按捺,则能够进行模数转化。

4.4模数转化电路

模数转化电路功用是对含有输入信号巨细、起伏和相位差信息的模仿电压信号进行模数转化,并把数据交给后续电路进行数据处理。

模数转化器材的挑选需求考虑多个要素。

首要,关于ADC通道数的考虑。因要对AD8307的单路输出电压和经滤波的AD8302双路输出电压进行检测,故在只考虑运用一片ADC器材时,该ADC的通道数要不小于3个,而关于多片ADC不予考虑。

其次,关于ADC位数的考虑。因规划要求相位的分辨率不低于0.1°,增益分辨率不低于1dB,关于AD8302来讲,其增益输出电压斜率为30mV/dB,相位差输出电压斜率为10mV/度,则相位所要求的准确度更高一些,要求ADC的最小可分辩电压要低于1mV,关于参阅电压为2.5V的ADC,其位数要大于13位,而关于参阅电压为5V的ADC,其位数要大于14位,故选用16位ADC最为适宜。

再次,关于ADC速度的考虑。在扫频时,单频点持续时刻最小为50μs,那么ADC在这50μs的时刻内应收集到尽量多的数据,但考虑到快速的ADC的本钱较高,所以在该要素上要顾及到速度和本钱两要素。

本系统中运用了16位ADS8364,内部具有彼此独立的6个ADC,每个ADC的转化频率为250KHz,内部有2.5V参阅电压,并有输出数据缓冲,可支撑多种作业形式。

ADS8364的参阅电压能够为外部或内部,本系统中运用了其内部的参阅电压,但要在其REF IN引脚加滤波电容,以尽量削减噪声搅扰。器材的CLK时钟信号的规模在0.05MHz~5MHz,本系统中运用的时钟频率为5MHz。

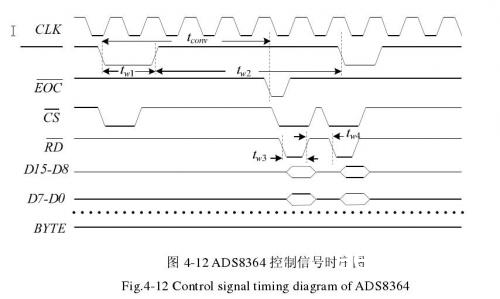

引脚A 0、A 1、A 2和ADD可用于对ADS8364的作业形式挑选。当A 2 A 1 A 0 =000~101时,表明对ADS8364内部的6个通道别离读数,例如A 2 A 1 A 0 =000表明CHA0进行读数,A 2 A 1 A 0 =001表明CHA1进行读数;当A 2 A 1 A 0 =110表明依照固定次序对ADS8364进行读数,先CHA0和CHA1,再CHB0和CHB1,最终CHC0和CHC1,如此重复;当A 2 A 1 A 0 =111时,表明对ADS8364选用FIFO方法进行读数,即先转化的通道先读取数据。而ADD能够操控读取数据时,是否读取通道的地址信息,当ADD=1时,对一个通道读数需求读两次,第一次读到的是该通道的地址,如CHA0的地址为0x8008,CHA1的地址为0x8009……CHC1的地址为0x800D,当ADD=0时没有地址数据,只需求读一次即能够把转化数据直接读出。引脚HOLDA、HOLDB、HOLDC别离操控两个ADC模块单元,本系统中运用A组和B组对AD8302的增益和相位输出电压进行不同时刻的循环采样,C组对AD8307输出电压进行采样。ADS8364的各操控信号之间的时序联系如图4-12所示。

图4-12中,CLK为ADS8364的时钟,频率为5MHz,HOLDX表明HOLDA、HOLDB、HOLDC信号中的恣意一个,tw1表明HOLDX低电平有用的最短时刻为30ns;tw2表明相邻两个HOLDX有用的最短时刻为30ns;t conv表明ADC开端转化到数据预备输出所需求的时刻为4us;EOC信号用于告诉外部器材模数转化完毕,能够进行数据读取了;CS为片选信号,tw3表明RD信号坚持低电平有用的最短时刻为40ns,CS低电平有用的时刻总是要大于t w3,tw4表明接连读信号所需坚持高电平无效的最短时刻为40ns;BYTE表明对读取数据位数的挑选,为1输出8位数据,为0输出16位数据。

在本系统中设定A 2 A 1 A 0 =111,ADD=1,运用FIFO方法读取通道地址和转化数据;BYTE=0选用16位数据的读取,并使WR为1无效,读信号RD、片选信号CS来自操控电路,收集完结信号EOC作为握手信号告诉操控电路进行数据的收集。

增益相位检测电路在辅佐检波电路的反应下,对输入信号和参阅信号进行信号功率的调整,使其满意增益相位检测器AD8302对输入信号的要求,并由有源低通滤波器对增益和相位电压进行滤波和电流扩大处理后送到模数转化器ADS8364,ADS8364把其转化为可被后续电路进行实时处理的数字量。

4.5相位极性判别电路

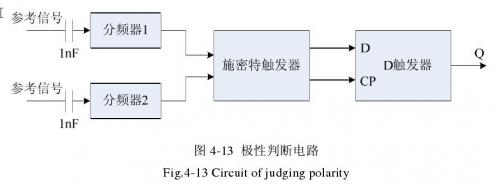

相位极性判别电路首要是判别二路输入信号的超前滞后极性,该电路首要由分频器MC12080、施密特触发器TL714C、D触发器SN74LVC74组成。如图4-13所示。1nF%&&&&&%起隔直效果。

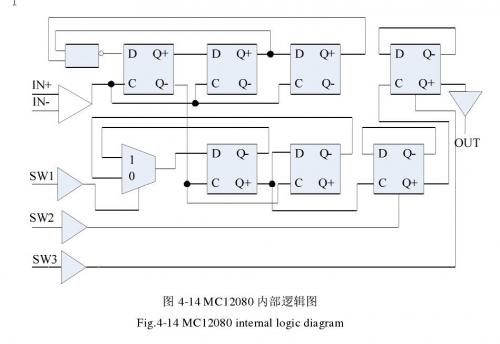

分频器MC12080具有四个分频系数,别离是10、20、40、80,由外部信号经过三个引脚操控,依据输入的频率不同,能够选用不同的分频系数,这样做的意图是便于对输入信号进行整形,由于整形电路的最高频率只能到达100MHz,所以先进行分频,使输入信号频率下降。

MC12080其内部逻辑结构图如图4-14所示。

作业电压为+5V电源,最高输入频率可达1GHz,输出电压起伏与负载电阻有关。由于它的后边接整形电路,所以整形电路的输入电阻便是分频器的负载电阻,一般整形电路的输入电阻都比较大,因此在输出端并联一1K的电阻,使其负载电阻不至于太大,这样能够确保其输出电压摆幅不会过大,本系统取820负载电阻。本系统用两片MC12080别离对两路输入信号进行分频。由相同的操控信号操控它们的分频比,所以两路信号的分频比总是相同的。

施密特特触发器的效果是将分频后的正弦波整形为方波,本系统用AD公司的高速比较器AD8612,14脚封装,其内部具有两路独立的比较器,所以用一片即可完结两路信号的整形。其最高输入频率达100MHz,传输延迟时刻只要4ns,作业电压规模是3V~5V,本系统选用单+5V供电。

D触发器是用TI公司的SN74LVC74,14脚封装,作业电压规模为1.65~3.5V,答应5V输入信号,内部有两个独立的D触发器,别离带有置位和复位功用引脚,本系统只用一个触发器,如图4-13所示,一路信号接在时钟输入引脚,另一路接在D输入引脚,SN74LVC74的时钟输入信号频率答应到达100MHz,所以能够与整形电路输出直接相接。D触发器的输出接到DSP的数据线上。