MEGAWIN系列单片机依据80C51的高效1-T结构的单芯片微处理器,每条指令需求1~7个时钟周期 (比规范8051快6~7倍),与8051指令集兼容。

1.根本特性

作业频率:24MHZ(最大,外部晶体)

有两种节能方式和8位的体系时钟分频器。

时钟源:外部晶体/时钟,内部高频/低频RC振荡器;上电后,内部高频RC振荡器(12MHZ)为默许的体系时钟源。软件能使能其它振荡器电路和经过编程AUXRA寄存器对它们进行切换。切换时钟源为外部晶体时,有必要使能外部晶体振荡器电路并等它安稳后再切换。选好时钟后,可软件制止未用的振荡器电路以削减能耗。

切换体系时钟为外部时钟:

1).使能外部时钟

IFMT=0X07;//AUXRA读操作

SCMD=0X46;

SCMD=0XB9;//此刻IFD的值=AUXRA的值

IFD |= 0X08;//设置使能外部晶体,将AUXRA的预设值写入IFD

IFMT=0X06;//AUXRA写操作

SCMD=0X46;

SCMD=0XB9;

2).切换到外部时钟

IFMT=0X07;

SCMD=0X46;

SCMD=0XB9;

IFD |= 0X03;//设置外部晶体为体系时钟

IFMT=0X06;

SCMD=0X46;

SCMD=0XB9;

3).封闭内部时钟

IFMT=0X07;

SCMD=0X46;

SCMD=0XB9;

IFD &= 0XFB;//设置将内置晶体中止

IFMT=0X06;

SCMD=0X46;

SCMD=0XB9;

有六个复位源: 上电复位、WDT复位、软件复位、外部(RST)复位、掉电检测器(brown-out)复位及不合法地址复位。

2.存储器

1)程序存储器

支撑ISP(在体系可编程)/IAP(在运用可编程);IAP空间可用作数据闪存。

IAP区域由IAPLB和ISP开端地址一起决议:IAP低鸿沟 = IAPLB * 256;IAP高鸿沟 = ISP开端地址 – 1;IAP低鸿沟地址有必要不要高于ISP开端地址或非设备界说的空间。不然,可能会导致Flash存储器中数据内容遭到损坏。

2)数据存储器

片上256字节随机存取储存器和1024字节片上扩展存储器(XRAM)

3.通用I/O口

有41个一般I/O口(GPIO),P0, P1, P2, P3, P4(P40-P46)能被装备为准双向口、上拉输出、集电极开漏输出以及高阻输入,P6.0 和 P6.1 仅可作准双向口方式及复用为 XTAL2和 XTAL1。每个端口有两个方式寄存器来挑选各端口引脚的输出类型:

nINT0/nINT1 触发类型:低电平或下降沿;

nINT2/nINT3触发类型:低电平、下降沿、高电平或上升沿

5.守时器

三个16位守时/计数器:守时器 0、守时器1及守时器2;每一个包含两个8位寄存器THx和TLx(这儿,x=0、1或2)。它们可装备为守时器或事情计数器。三个守时器输出口(T0CKO 对应P34、T1CKO对应P35、T2CKO对应P10);T0/T1/T2时钟能够挑选X12 方式。

守时器功用,TLx寄存器每12个体系时钟周期(规范C51的机器周期)或每1个体系时钟周期(是规范C51的12倍)加1,经过软件设置AUXR2.T0X12、 AUXR2.T1X12和 T2MOD.T2X12位来挑选 。每12个体系时钟周期加一,计数速率是1/12的晶振频率。

计数器功用,依据对应的外部输入引脚的下降沿T0、T1或T2寄存器加1。在这功用中,每个守时器时钟周期对外部输入信号(T0、T1和T2引脚)进行采样,当采样信号呈现一个高电平接着一个低电平,计数加1。当检测到跳变时新计数值呈现在寄存器中。

守时器2有四种作业方式:捕获、主动加载(向上或向下计数)、波特率发生器和可编程时钟输出,经过专用寄存器T2CON和T2MOD来挑选。

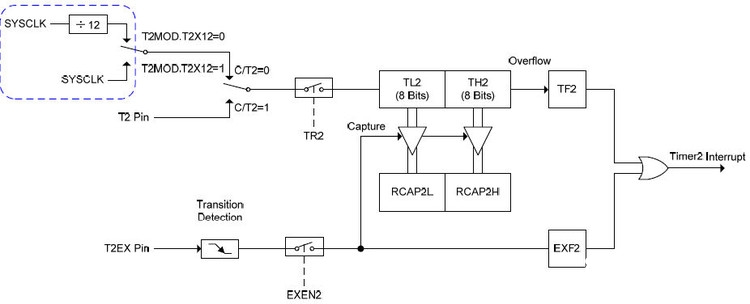

1)捕获方式

当外部输入信号T2EX由下降沿跳变时引起守时器2的寄存器TH2和TL2别离对应的捕获到RCAP2H和RCAP2L。

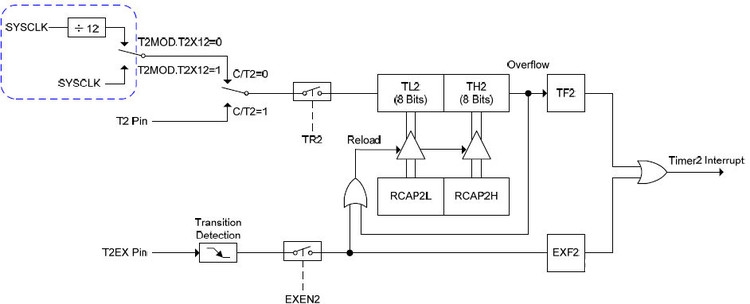

2)主动加载方式

在复位之后,DCEN=0意思是默许为守时器2向上计数。假如DCEN置位,守时器2向上或向下计数由T2EX引脚的值来决议。

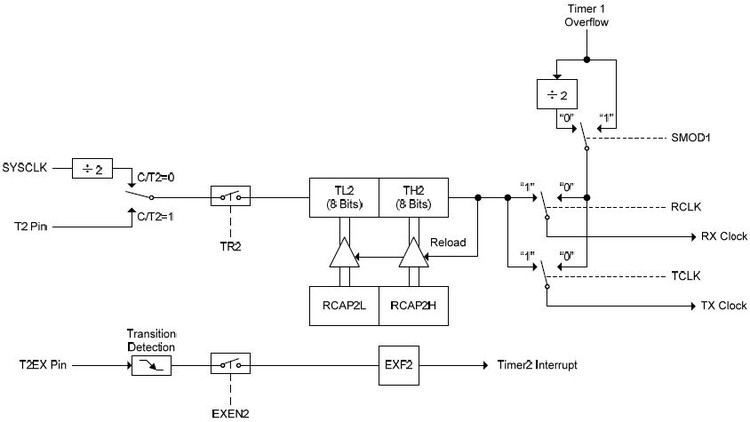

3)波特率发生器方式

T2CON寄存器的RCLK和/或RCLK位答应串行口发送和接纳波特率既可源自守时器1或守时器2。当TCLK=0时,守时器1作为串行口传送波特率发生器。当TCLK=1,守时器2作为串行口传送波特率发生器。RCLK对串行口接纳波特率有相同的功用

4)可编程时钟输出方式

CP/RL2=0且T2OE=1;守时器2作为一个输出占空比为50%的可编程时钟发生器,所发生的时钟从P1.0 引脚输出来。

输出频率=Fosc/4(65536-(RCAP2H,RCAP2L))

守时器2 的可编程时钟输出方式编程过程如下:

a.置位T2MOD寄存器的T2OE位。

b.铲除T2CON寄存器的C/T2位。

c.从公式计算出16位加载值并输入到RCAP2H和RCAP2L寄存器。

d.在TH2和TL2输入一个16位初始值。能够和重载值持平。

e.设置T2CON的TR2操控位开发动守时器。

在时钟输出方式,守时器2翻转不会发生中止

6.串行口

2个全双工串行口,功用同规范51;

串行口能够作业在四种方式:方式 0 供给同步通讯一起方式 1、2 和方式 3 供给异步通讯。异步通讯作为一个全双工的通用异步收发器(UART),能够一起发送和接纳并运用不同的波特率。

方式0:8位数据(低位先出)经过RXD0(P3.0)传送和接纳,波特率可经过SCFG寄存器的URM0X6位挑选为体系时钟频率的1/12或1/2。

方式1:10位数据经过TXD0传送或经过RXD0接纳,波特率是可变的。

方式2:11位数据经过TXD0传送或经过RXD0接纳,波特率能够装备为1/32或1/64 的体系时钟频率

方式3:11位数据经过TXD0传送或经过RXD0接纳,波特率是可变的。

除了规范操作外,UART0还能具有侦查丢掉中止位的帧过错和主动地址辨认的功用。

串口1运用独立波特率发生器,串口0可挑选运用守时器1或守时器2(T2CON的RCLK和TCLK决议),也可共用串口1的波特率(RCLK=0,TCLK=0及URTS=1)

串口1运用的寄存器SCON1、SBUF1、S1BRT需求切换到SFR页1才干运用:SFRPI=0X01;

7.可编程计数器阵列(PCA)

该功用与规范守时/计数器比较以更少的CPU占用供给了更多的守时才干。它的长处包含削减了软件复杂度并提高了精度。

PCA由一个专用守时/计数器作为一个6组比较/捕获模块的时刻根底,6组比较/捕获模块中的每一组都能够编程为如下恣意方式:

– 上升和/或下降沿捕获

– 软件守时器

– 高速输出

– 脉宽调制(PWM)输出

1)PCA 守时器/计数器

它的时钟输入能够从以下来历挑选(CPS1 和 CPS0挑选):

– 1/12 体系时钟频率

– 1/2 体系时钟频率

– 守时器0溢出,能够让低频时钟源输入到PCA守时器

– 外部时钟输入,ECI(P1.1)引脚的1-0回转

2)比较/捕获模块

6组比较/捕获模块中的每一组都有一个方式寄存器,叫做CCAPMn(n代表0,1,2,3,4,5),来挑选其作业方式。ECCFn位操控当中止标志置位时每个模块的中止敞开/封闭。

3)PCA运转方式

具体作业方式与STC同。

供给4种精度的PWM输出:8位(可主动重载)、10位、12位、16位(后3种需手动重载溢出值)

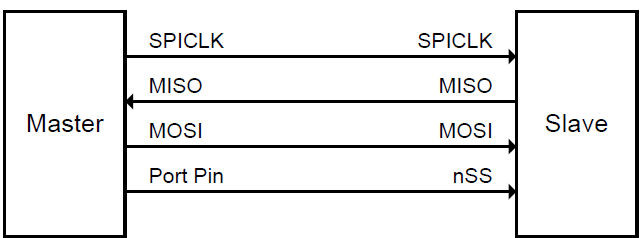

8.串行外设接口(SPI)

供给了一个高速串行通讯接口(SPI)。SPI接口是一种全双工、高速同步通讯总线,有两种操作方式:主机方式和从机方式。不管哪种方式,12MHz体系时钟时支撑高达3Mbps的通讯速度。SPI状况寄存器(SPSTAT)有一个传送完结标志(SPIF)和写抵触标志(WCOL)。

SPI接口有4个引脚:MISO (P1.6), MOSI (P1.5), SP%&&&&&%LK (P1.7) 和nSS (P1.4)。

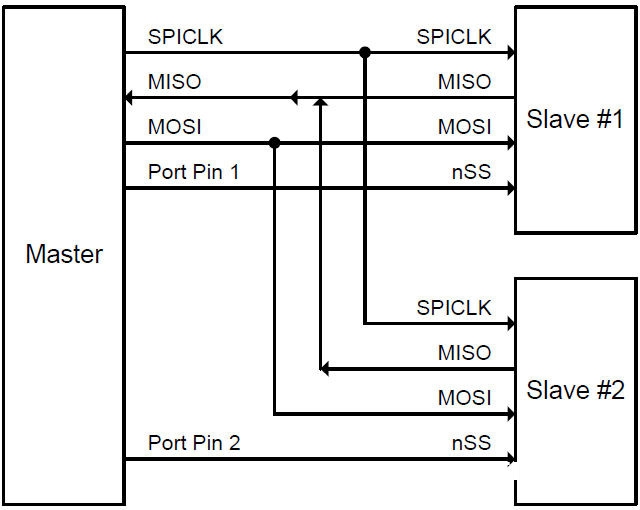

1)典型SPI装备方式:

a.单主机单从机

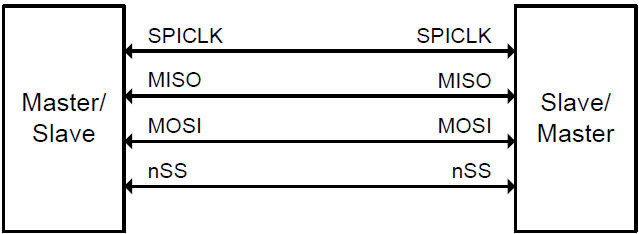

b.互为主机/从机

c.单主机多从机

2)注意事项

SPI通讯中,传输总是由主机主张 。若 SPI使能(SPEN=1)并作为主机运转,写入SPI数据寄存器(SPDAT) 数据即可发动SPI时钟生成器和数据传输器,大约半个到1个SPI位时刻后写入SPDAT的数据开端呈现在MOSI线上。

在开端传输之前,主机经过拉低相应nSS引脚挑选一个从机作为当时从机。写入SPDAT寄存器德数据从主机MOSI引脚移出,一起从从机MISO移入主机MISO的数据也写入到主机的SPDAT寄存器中。移出1字节后,SPI时钟发生器中止,置传输完结标志SPIF,若SPI中止使能则生成一个中止。主机CPU和从机CPU中的两个移位寄存器能够当作一个分隔的16位环形移位寄存器,数据从主机移到从机一起数据也从从机移到主机。这意味着,在一次传输过程中,主从机数据进行了交流。

SPI在发送方向是单缓冲的,而在接纳方向是双缓冲的。发送数据直到上一次数据发送完结后才干写入移位寄存器,数据发送过程中写入数据寄存器就会使WCOL(SPSTAT.6) 置位来标明数据抵触。这种情况下,正在发送的数据持续发送,而刚写入数据寄存器形成抵触的数据就会丢掉。WCOL运用软件向其位写入’1’来清零。

SPI时钟频率挑选(主机方式)运用SPCTL寄存器的SPR1 和SPR0 位来设置。

9.键盘中止

键盘中止功用首要用于当P2口等于或不等于某个值时发生一个中止,这个功用能够用作总线地址辨认或键盘键码辨认。

键盘中止掩码寄存器(KBMASK) 用来界说P2口哪些引脚能够发生中止;键盘方式寄存器(KBPATN)用来界说与P2口值进行比较的值,比较匹配时硬件置键盘中止操控寄存器(KBCON)中的键盘中止标志(KBIF)。

10.10位模数转化器ADC

ADC子体系由一个模仿多路器(AMUX)、一个200ksps、10逐次迫临型模数转化器组成。ADC转化时钟由ADCON寄存器的SPEED1、SPEED0两位决议的体系时钟分频而来。(补白:现在主张ADC操作时,体系时钟不要超越20MHz)

ADC转化成果=Vin*1024/Vdd;

在运用ACD功用之前,用户应:

a.设置ADCEN 位发动ADC硬件;

b.设置SPEED1 和 SPEED0位设定转化速度;

c.设置CHS2、CHS1 和CHS0挑选输入通道;

d.设置P1M0和P1M1寄存器将所选引脚设定成只输入方式;

e.设置ADRJ 位装备ADC转化成果输出方式。

一旦转化完毕,硬件主动铲除ADCS位,设置中止标志ADCI,并将转化成果依照ADRJ的设置存入ADCH和ADCL。为了取得最佳转化作用,用作ADC的引脚应当制止其数字输出和输入,能够将引脚设为只输入方式。

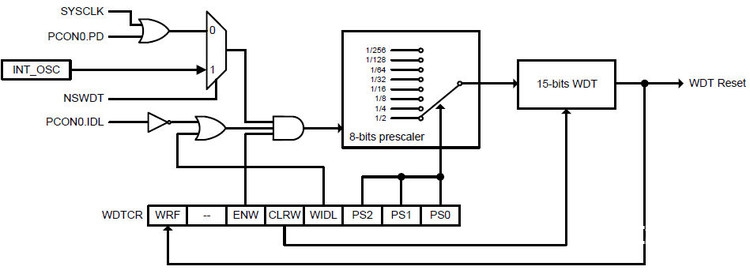

11.看门狗守时器WDT

看门狗守时器 (WDT) 用来使程序从跑飞或死机状况(比如电源噪音/动摇、静电搅扰等使CPU运转呈现紊乱或死机)康复的一个手法。软件跑飞时,WDT使体系复位来避免体系履行过错的代码。WDT由一个15位独立守时器、一个8分频器和一个操控寄存器(WDTCR)组成。

看门狗溢出时刻=12*分频值*32768/SYSCLK (体系时钟为12Mhz时,最长延时8s,时钟越高,延时越短)