RS(Reed—Solomon)编码是一种具有较强纠错才能的多进制BCH编码,其既可纠正随机过错,又可纠正突发过错。RS编译码器广泛应用于通讯和存储系统,为处理高速存储器中数据可靠性的问题,文中提出了RS编码的完成办法,并对编码进行了时序仿真。仿真成果表明,该译码器可完成杰出的纠错功用。

RS(Reed—Solomon)码是过失操控领域中的一种重要线性分组码,既能纠正随机过错,又能纠正突发过错,且因为其超卓的纠错才能,已被NASA、ESA、CCSDS等空间组织承受,用于空间信道纠错。本文研讨了RS码的完成办法,并依据Xilinx的FPGA芯片Spartan-6 XC6SLX45完成了RS编译码器的规划,一起对其进行了仿真和在线调试,并给出了功用仿真图和测验成果。时序仿真成果表明,该编译码器能完成预期功用。

1 RS编码的完成办法

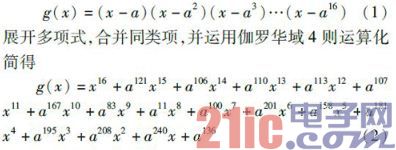

RS码是一种多进制BCH(Bose—Chaudhuri—Hocquenghem)码,在给定每个码字所具有多少冗余量的状况下,RS码具有极大的最小间隔。即RS码的最小间隔d、信息长度k以及码字长度n满意d=n-k+1。而RS(255 239)码是在伽罗华(Galois Field)GF(28)中运算得到的,编码器完成的要害是伽罗华域乘法器的规划。规划中的乘法是2个有限域中元素的指数相加与255取模。GF(28)编码参数如下:码长n=255;信息位个数k=239;校验位r=n-k=16;纠错才能t=8;码距d=17。生成多项式为

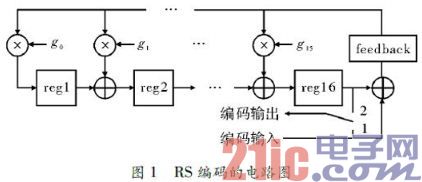

依据式(3)画出RS编码的电路图,如图1所示。

n-k级RS编码器主要由一组线性反应移位寄存器和操控电路组成,其是n-k=16级编码器,亦是线性反应寄存器的反应系数,reg16寄存器的值与当时输入的信息码元异或得到的成果即为feedback寄存器的值。

编码进程:

进程1 将一切寄存器清零,开关放到1上,则239个信息码元一边顺次进入除法电路,一边顺次输出。

进程2 当最终一个信息码进入电路后,将开关放到2上,第一个校验位输出。

进程3 校验码按时钟节拍载入寄存器,并顺次输出。当最终一个校验位输出时,编码完毕。

2 RS编码的仿真成果及剖析

规划的RS(255 239)编码器运用Verilog HDL对整个模型进行描绘,以Xilinx FPGA芯片Spartan-6XC6SLX45为硬件渠道进行完成,并使用ISim仿真东西对RS编码进行仿真。

规划的RS(255,239)编码器,信息位239位编码为0,1,2,…,238,则16位校验位的值为58,236,152,44,88,31,20,168,121,60,32,10,191,166,4,101。规划的RS(255,239)编码器的仿真图如图2所示,当DI_VAL=0时,输出239个信息位;当DI_VAL=1时,输出16个校验位。该编码器完成了预期的编码功用。

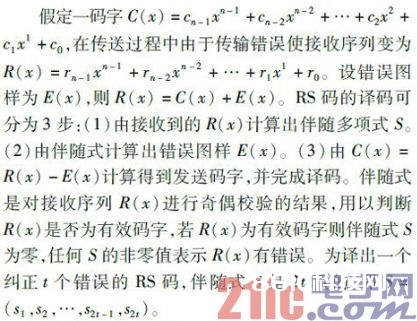

3 RS译码的完成办法

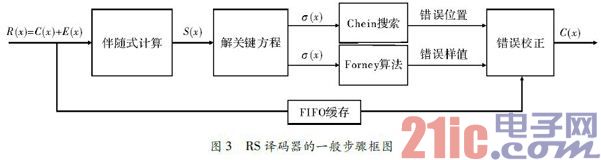

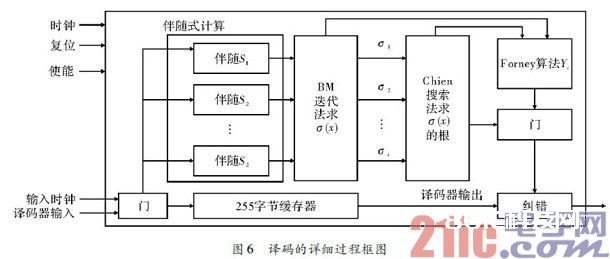

RS译码主要有时域译码和频域译码,时域译码一般选用BM迭代算法或欧式算法(Euclid’s Algorithm)。RS译码中最重要的环节是求解要害方程,欧式算法在求解要害方程时需进行多项式次数的判别,因而形成硬件电路杂乱,译码速度下降,BM迭代算法具有快速、耗费资源少、操控电路较为简略等长处。文中改善后的BM迭代原理及以该算法为根底的RS译码器的FPGA完成。RS译码可分为4步:(1)由接纳到的码组核算随同式。(2)求要害方程。(3)核算出过错图样。(4)由过错图样和接纳码组核算出或许发送的码字。图3给出了RS译码器的一般进程框图。

以上运算均可用流水线结构硬件完成。

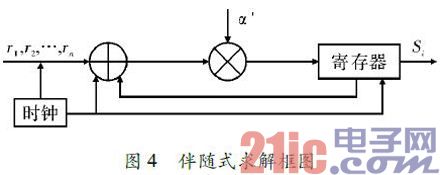

初始化时,一切寄存器置零。经255个周期,接纳完一切255个符号后,便可得到悉数16个随同式。因整个译码器选用流水线结构,所以在随同式核算完后,发生一个时钟周期有用的“sc_done”信号,用以发动后续电路进行新的核算。因为在BM模块中,用到了A(x)与S的卷积求和,因而本模块将核算出的随同式序列串行输出。

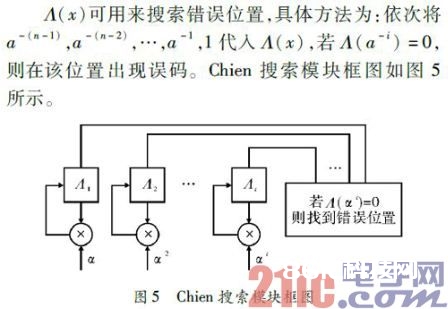

要害方程的核算选用BM算法,BM算法不仅在RS码的译码中起着要害作用,且也是现在已知的求序列线性杂乱度最快且最佳的办法之一。该算法选用规整的脉动阵列,硬件完成更为便利。通过求解要害方程,得到A0~A8,其为后续的Chien查找模块供给了参数。

该进程彻底完成流水线结构,其间包含随同式核算、要害方程求解、Chien查找、Forney算法等模块并行作业。在通过295个固有推迟后,每个时钟周期均可接连输出经校对的码字。

4 RS译码的仿真成果及剖析

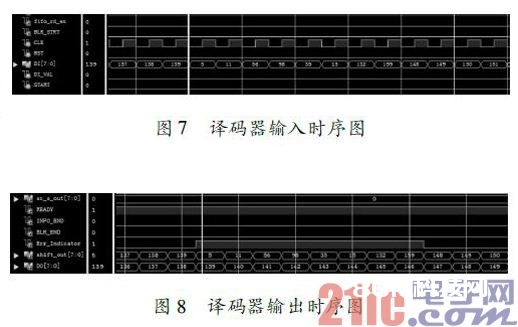

因规划的译码器最大纠错才能为8个符号,该文设定过错状况是第140位到第147位全错,正确值为140,141,142,143,144,145,146,147,过错值为5,11,56,98,35,15,132,159,图7是输入到译码器中含8个接连过错码字的255位编码序列,图8是译码器输出悉数纠错今后的编码序列,由ISim仿真波形图可知,Err_Indicator表明过错标志,规划的译码器能完成最大的纠错才能。

5 完毕语

文中论述了RS(255,239)编译码器的规划原理,并对编码器给出了在ISim中的时序仿真成果,其成果证明了该编码器规划的正确性。而在对译码器的规划中,假定呈现接连8个误码的状况,并用ISim对所规划的译码器进行验证,由时序仿真成果表明,规划的RS(255,239)译码器能完成最大的纠错才能。规划的RS(255,239)编译码器达到了预订的方针,且该编译码器可应用于数据通讯和数据存储系统的过失操控中。