摘要 提出了一种依据TigerSHARC TS201S完结的MIMO体系空时编码盲辨认办法的规划与完结,该规划可以在非协作条件下,运用空时编码在时刻分集和空间分集下,所表现出的不同时滞相关性,完结盲辨认空时编码方法。天线接纳信号经过预白化,时滞相关度核算,终究运用码字表判定输出。经验证,该体系功能安稳,易于完结,且对空时编码方法具有较高的盲辨认精度。

要害词 数字信号处理器;多输入多输出体系;空时编码;盲辨认;时滞相关

空时编码(Space—Time Block Coding,STBC)是到达或挨近MIMO无线信道容量的一种有用的编码方法。空时编码方法的盲辨认是通讯对立范畴需火急研讨的范畴,其可以为MIMO体系对立技能供给根底和技能支撑,具有重要的研讨价值。

时滞相关算法是依据不同空时编码的相关矩阵在不一起延核算下的差异性,选用逐级比照,完结对空时编码方法的盲辨认。具有核算精度高,抗频偏作用好等长处。文中提出一种依据ADI公司DSP芯片TigerSHARCTS201S的空时编码盲辨认方案规划和完结。

1 体系硬件规划

1.1 体系硬件框图

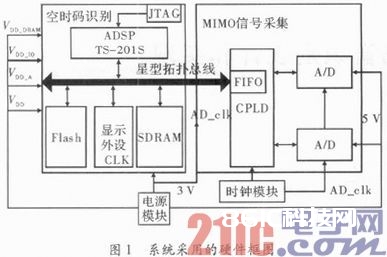

体系硬件框图如图1所示。由信号处理、信号收集、电源、时钟4部分构成,信号收集由CPLD和ADC组成,担任完结A/D转化,信号处理由TS201S芯片及其外设组成,用于存储A/D采样的数据,并进行空时码盲辨认运算处理。电源模块为其他一切模块供给正常作业所需的电压,时钟模块中由晶振和倍频芯片组成,供给体系所需时钟。

体系作业时,设备首要通电初始化,从Flash中载入用户运用程序,继而经过CPLD操控ADC进行数据收集,并运用DMA中止方法读取数据并进行编码辨认运算。

1.2 TigerSHARC TS201S简介

TigerSHARC TS201S兼有AS%&&&&&%和FPGA的信号处理功能和指令集处理器的高度可编程性与灵敏性,适用于高功能、大存储量的信号处理与图画运用。

TS201S内部分为DSP核和I/O接口两部分,经过4条总线传输数据、地址和操控信息。并供给彻底可中止的编程方法,支撑汇编和C/C++言语编程,32/40位的浮点运算及最高64位的定点运算。在600 MHz时钟速率下,可到达每秒48亿次乘加运算。

1.3 电源、时钟和总线方案规划

TS201S和AD7864对电源的要求较高,以TS201S内核时钟500 MHz为例,4个电源VDD、VDD_A、VDD_IO、VDD_DRAM的精度要求操控在5%以内。因而体系中的电源芯片选用了TPS54350,其精度可达1%。

时钟模块中,晶振发生27 MHz时钟经过倍频芯片得到54 MHz时钟后进入CPLD,一方面作为TS201S的体系时钟SCLK,另一方面在CPLD内12分频后作为AD7864的作业时钟信号AD_CLK。为避免其对体系电源发生耦合搅扰,晶振和倍频芯片的电源与本板电源之间要用电感或磁珠进行阻隔。

在体系总线负载较重的情况下,规划不妥会约束总线只能在低频下作业乃至无法读取数据。因为环形结构就任一负载的改动均会影响到其他负载的作业,规划中选用了星形总线结构,如图2所示。

1.4 信号收集方案规划

信号收集模块由CPLD和两片ADC组成,A/D转化芯片选用AD公司出产的AD7864,其转化精度12位,最高吞吐量520 ksample·s-1,转化时刻最快为1.65μs,采样坚持0.35μs,此外其单电源和低功耗特性最低可达20 Uw,其可以满意体系的要求,简化硬件规划。

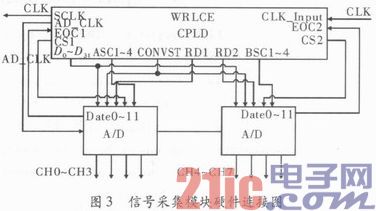

信号收集前,需对AD7864的一些输入引脚进行装备,南Alterta公司的CPLD产品MAX3256完结。如图3所示,CONVST为使能输入引脚,置位高可操控AD7864发动。CS为片选信号,低电平有用。RD为读使能,低电平有用,当CS有用且RD为低,才答应AD7864输出转化成果,此刻WR有必要为高。引脚SL1~SL4是AD7864的通道挑选输入引脚,高电平有用。H/S SEL为高时表明将经过软件方法来挑选A/D转化通道,反之表明硬件挑选。当转化完毕后,EOC引脚输入低电平。

AD7864选用分时输出方法,采样信号来自TS201S的守时/计数器,每次计数器满时TMROE引脚会发生4个总线时钟的高电平,CPLD中对此信号做反向后作为AD7864的CONVST信号,在数据传输中,片1占低位数据线,片2占高位数据线,分时可避免总线抵触。

1.5 显现方案规划

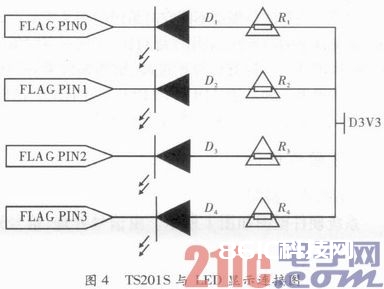

体系选用FLAG PIN外接LED做为进展显现,DSP在履行到不同的处理进展时经过改动FLAG PIN口的电平操控对应的LED导通,以指示当时数据剖析的过程。图4为外接LED的衔接图,每个FLAG PIN上的LED均不影响其他FLAG PIN接口,在LED后运用了一个上拉电阻接VCC。

体系复位时,一切FLAG PIN置高电平,ADC收集完毕触发DMA中止,从SDRAM中读取数据,并进入到预白化处理,此刻FLAG PIN1至低电平,依据算法,对白化后的数据进行时滞相关剖析,并运用码字表判定呼应码型时,并别离拉低FLAG PIN2和FLAG PIN3。

该种办法装备灵敏、软件简略,体系选用4个FLAGPIN来安置显现,DSP具有满足的IO接口运用,在规划时充分运用了硬件资源,一起运用DMA中止,有用进步了CPU的功率,也完结了资源的同享和并行处理,一起还在芯片运算过程中及时发现毛病并定位处理。

2 体系软件规划

2.1 空时编码盲辨认原理

STBC经过在时刻与空间进行联合编码到达进步体系传输功能的意图,因而在不一起刻从不同天线发送的数据具有必定的相关性,而不同空时编码之间的相关度并不同,因而可运用该相关度来区别不同的码型,从而将空时编码的方法辨认出来。

2.2 空时编码盲辨认办法

(1)预白化。预白化的意图是去除信道对接纳信号相关性的影响。白化矩阵W经过对分时相关矩阵P做特征值分化得到

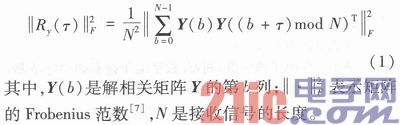

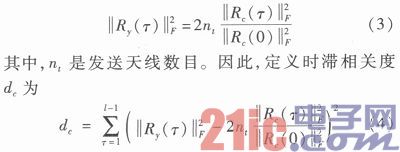

,其间A-1为特征值矩阵Λ的广义逆。W与原数据相乘便可得到解相关矩阵Y。 (2)核算时滞相关度。运用接纳信号预白化后得到的解相关矩阵Y,依据核算学公式核算时滞相关范数

空时编码矩阵的理论时滞相关特性仅与编码矩阵自身有关。因而,运用与式(1)相同的方法,可将编码矩阵不同的列进行矩阵乘加运算,并取F范数来表征。

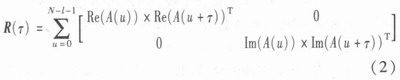

由此得出核算空时编码的时滞相关矩阵R(τ)

其间,空时编码矩阵的每一列代表不同的发射时刻,A(u)是码型A编码矩阵的第u列,l为码型分组长度。已预白化后的接纳信号矩阵与发送端编码矩阵,在时滞相关函数F范数上有如下联系

(3)判定码型。遍历候选码集,核算出接纳信号与候选码会集每一种空时码的相关度,取其间最相关的码型便为判定码型。

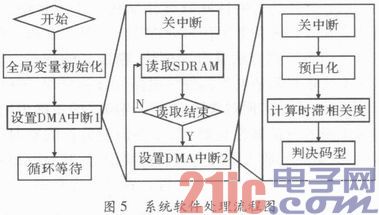

2.3 软件规划

软件体系选用模块化结构规划,程序流程如图5所示。包含体系发动、装备体系寄存器、设置全局变量和敞开中止操控等。当ADC模块将采样数据悉数写入SDRAM后,CPLD告诉DSP触发DMA中止1,将SDRAM中的数据读入DSP,读取完毕后DMA触发中止2,并对ADC采样数据进行处理:(1)预白化,去除新到对采样数据相关性的影响。(2)核算采样数据与候选会集每种码字的时滞相关度。(3)依据上述核算成果,选取使时滞相关度最小的码型为判定码型。

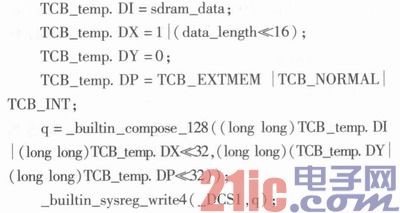

经过对DMAC寄存器的设置,可操控DMA的流向、通道和方法,典型的数据读取要害代码如下:

数据处理部分的要害函数包含白化和时滞相关量核算,数据传递选用了单维读入与多维传递的方法,行将多天线的数据依照天线次序顺次读入,但在DSP内部数据传递时,多根天线的数据依照时刻次序传递,在函数内部手动寻址,即契合算法要求,又加快了数据处理的速度。数据处理时包含很多的矩阵转置和乘加操作,在核算时优化为内积核算方法,运用ALU运算块X和Y,每个周期并行核算时滞矩阵两列之间的相关范数,这便节省了内存资源,减少了寻址次数,且加快了核算速度。

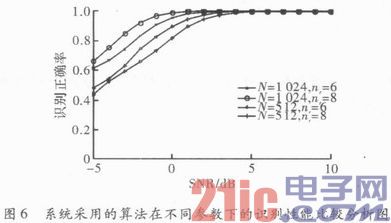

本算法在不同参数下的Matlab功能仿真如图6所示,采样数据越长,接纳天线数越多,辨认功能也越好。实践测验证明与希望相一致,验证了规划的合理性和正确性。

3 完毕语

DSP芯片具有的特别软硬件结构和指令体系,使其能高速处理各种数字信号处理算法。依据此规划的空时编码盲辨认办法具有速度快、精度高的特色。一起该体系依托简练的外部硬件电路规划和合理的软件程序规划,可以完结对常用空时编码方法的正确辨认。且该体系的可扩展性杰出,当需求辨认最新的空时编码时,只需将其放入编码方法候选会集,为其分配显现接口即可,而无需过多更改硬件设置及软件程序。