Xilinx 7系列FPGA全系内置了一个ADC,称号为XADC。

这个XADC,内部是两个1mbps的ADC,能够收集模仿信号转为数字信号送给FPGA内部运用。

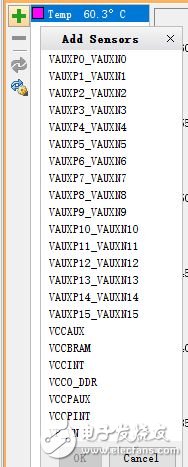

XADC内部能够直接获取芯片结温文FPGA的若干供电电压(7系列不包括VCCO),用于监控FPGA内部情况。一起供给了17对差分管脚,其间一对专用的模仿差分输入,16对复用的模仿差分输入,不运用的时分能够作为一般的User I/O。

关于XADC详细的结构,功用和各个参数的意义,请参阅相关文档。这儿不做详细描述。别的有两点需求留意。

1.关于参阅电压的设置,会影响差错规模及采样值的计算公式。

2.模仿差分输入对模仿信号幅值有要求,需求外边模仿电路进行必定程度的转化。

假定现在需求用XADC来获取几个模仿信号的信息,那么应该怎么操作呢。下面解说一种个人偏心设置办法。

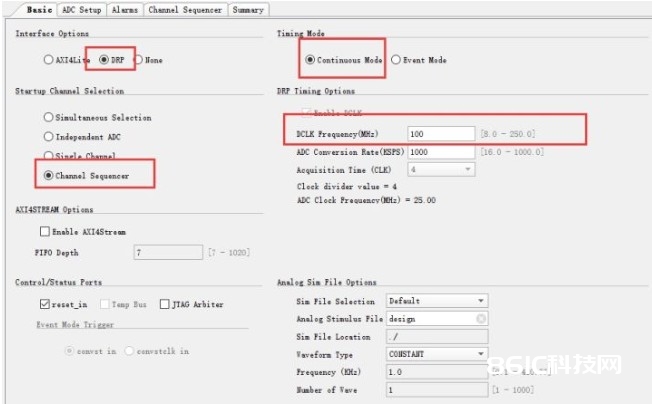

留意红框中的几点:

1.运用DRP端口获取数字信号,这样操控好像更简略一些。

2.运用接连采样形式,ADC一向作业在数据收集形式,收集后就能够进行输出。

3.运用Channel Sequencer形式,因为只要两个XADC而需求采样的数据过多,所以让XADC顺次连续进行采样。

4.设置好DRP端口的时钟频率。

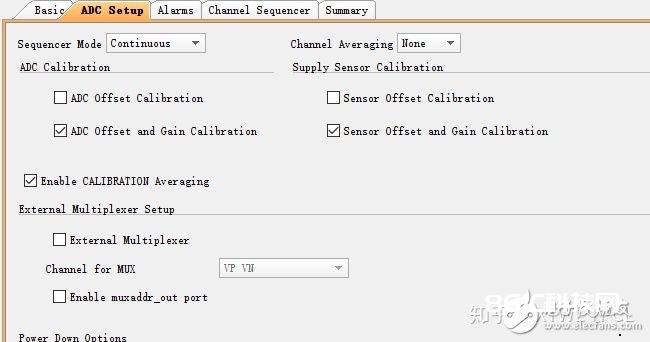

IP设置第二页,首要是设置Calibration、平均值和外部MUX。这几个能够暂时越过,等了解XADC的运用后在进行深化了解。

第三页设置告警参数,能够不必。假如需求的话,能够设置一下,便于运用。

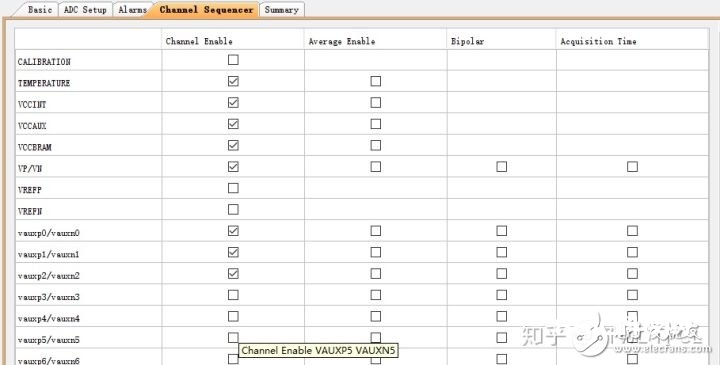

第四页设置需求运用的通道,这儿挑选温度和三个供电电压,并挑选一个专用的模仿输入通道和前三个复用的模仿输入通道。

终究一页是Summary,能够看看设置是否有问题,没有需求设置的当地。

这个时分最基本的一个多通道获取数据的XADC设置好了,至于设置中没有细说的当地,能够等娴熟运用之后进行研究,找出最合适的运用形式。

下面是怎么运用这个生成的IP。因为运用DRP端口来读取数据,所以需求规划一个DRP读写操控器。不过因为XADC自身就供给了一些信号,所以这个规划其实十分简略。

.di_in(di_in),

.daddr_in(daddr_in),

.den_in(den_in),

.dwe_in(dwe_in),

.drdy_out(drdy_out),

.do_out(do_out),

.dclk_in(dclk_in),

首要理一下DRP端口,首要7个信号。因为只是是读取数据,所以输入部分没有运用的必要。

.di_in (16‘b0),

.dwe_in (1’b0),

时钟信号衔接DRP所运用的时钟即可,留意频率需求和XADC IP中的设置相同。

.daddr_in ({2‘b00,CHANNEL_OUT}),

.den_in (EOC_OUT),

.do_out (DO_OUT),

.drdy_out (DRDY_OUT),

.eoc_out (EOC_OUT),

.channel_out (CHANNEL_OUT),

余下四个DRP端口,两个输出两个输入。两个输出直接引出来,其间do_out便是终究需求的数据。这个端口是16bit,取高12bit即可(对应XADC中声称的12位)。

XADC的IP端口中还有两个,名为eoc_out和channel_out。将eoc_out衔接到DRP端口的den_in端口,意义是当多路采样的某一路完结采样后,则发动DRP端口操作,开端进行读取数据。将channel_out补两位之后送入daddr_in作为DRP端口操作的地址信号。这样就完结了DRP的读写操作。

不过这样输出的数据,会周期性的在几个端口数据之间改变。所以通常在后端加一个过滤设置,详细行为是,当代表DRP操作完结的drdy_out拉高的时分,依据channel_out的值来判别是哪一个通道的。

always @(posedge clk)begin

if(DRDY_OUT == 1’b1 && CHANNEL_OUT ==5‘d0)begin

Temperature end else begin

Temperature end

end

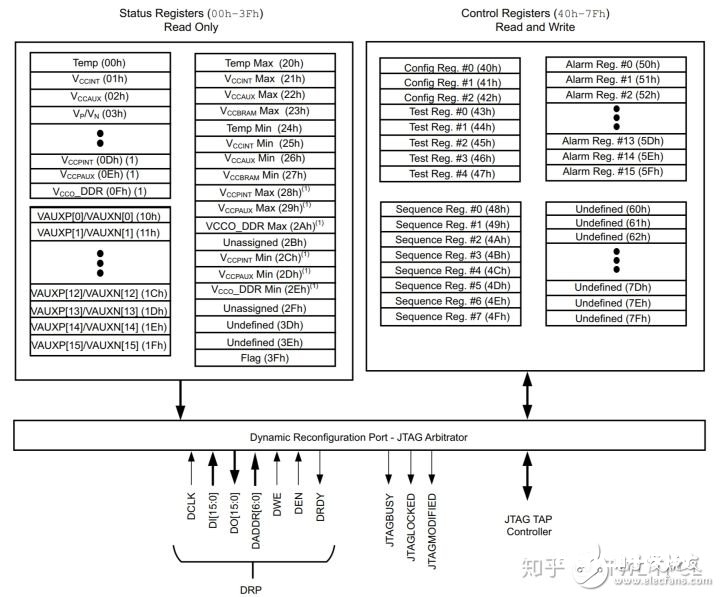

关于每个采样通道的详细地址,能够参阅手册

至于模仿差分输入Pin,直接送到顶层的相对应管脚即可。留意Vivado东西或许需求对复用的模仿Pin进行电平束缚,依据VCCO的电压值挑选相应的lvcmos即可,例如1.8V的VCCO就挑选lvcmos18即可。

这样就能够获取对应的模仿采样数据了。因为绝大部分情况下需求检测的模仿信号改变相对较慢,运用XADC是满足用于检测的。

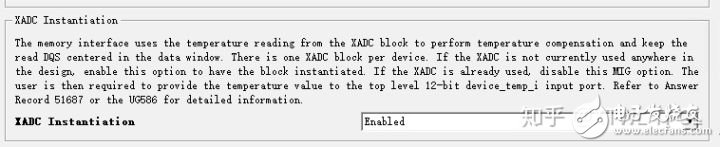

涉及到XADC的运用问题还有MIG IP。MIG是Memory Interface的IP,也便是DDR3之类的DDR存储器IP。因为此类接口一般速率过高,会需求温度信息对接口做必定的纠正。在MIG IP的装备中,会默许发动XADC。

此刻的XADC只是需求供给温度信息就能够了。当需求供给更多信息,就需求独立装备XADC,这样工程中就会生成两个XADC;或许例化了两个MIG IP,这样各自就会需求一个XADC。因为硬件中只要一个XADC模块,当发现工程中需求多个XADC模块的时分,东西就会提示犯错。

解决计划也十分简略,MIG IP中去掉XADC。然后在规划中独立例化XADC IP。依据上文的做法获取温度信息后送往MIG。MIG IP去掉XADC后会生成一个温度端口用来接纳数据。这样就不会发生冲突。

别的一个十分快捷的获取温度信息的计划便是运用Hardware Manager。在Hardware Manager中翻开XADC就能看到温度信息。

其实XADC一切通道数据都能够经过这个办法获取。