Xilinx每一个FPGA都有一个共同的ID,也便是Device DNA,这个ID相当于咱们的身份证,在FPGA芯片出产的时分就现已写死在芯片的eFuse寄存器中,具有不行修正的特点,因为运用的是熔断技能。值得阐明的是,在7系列及曾经,这个ID都是57bit的,但是在Xilinx的Ultraslace架构下是96bit。

FPGA的DNA咱们一般的运用场景是用于用户逻辑加密。一般来说,用户在逻辑上能够经过特定的接口把这个Device DNA读取出来,经过一系列加密算法之后和预先在外部Flash存储的一串加密后的字节串做比较,这个flash存储的加密后的字节串也是由该DNA经过加密后得到,fpga加载程序后能够先从flash读出该段字节做比较,假如相同,则让FPGA发动相应的逻辑,如不同,则代表该FPGA没有经过用户授权,用户逻辑上能够封闭FPGA的逻辑功用乃至能够经过一些手法让硬件损坏。

怎么获取FPGA的Device DNA呢,下面我从JTAG和调用源语两个办法阐明,并敞开中心代码供咱们参阅。

第一种,经过JTAG获取,这种办法在ISE的Impact或许vivado都能够完结,下面介绍在Vivado下怎么或许Device DNA,这个其实很简单,首要板卡经过JTAG衔接PC,在Flow Navigator -》 PROGRAM AND DEBUG 界面下,点击对应的FPGA的芯片,点击Hardware Device Properties,在search中查找dna,在REGISTER下能够找到Device DNA,在Impact下怎么获取DNA网上有相应的文章,这儿就不做进一步介绍。

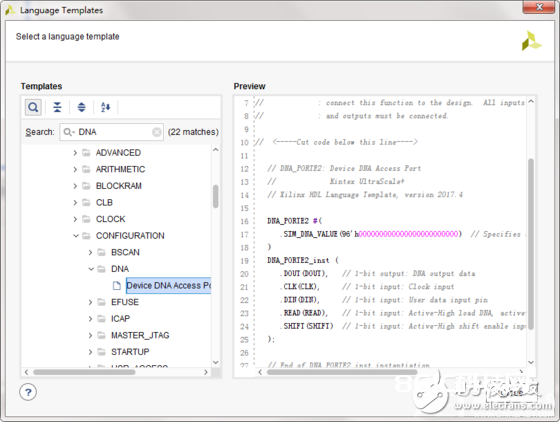

第二种,用户逻辑经过调用源语获取,至于源语是什么,这儿跟咱们共享一个技巧,一般咱们运用源语的时分,往往记不住很多的源语界说,那么怎么快速查找到咱们想要的源语呢,在Vivado中,有一个功用是Language Templates,在Flow Navigator能够找到,里边包含了根本一切的Xilinx供给的源语和一些语法用法,以DNA读取为例,咱们查找DNA,就能够找到关于DNA的源语,因为博主用的是VU9P的片子,所以用的是DNA_PORTE2这个源语,针对7系列及曾经,运用的是DNA_PORT源语,这两个源语都能够在Language Templates找到。

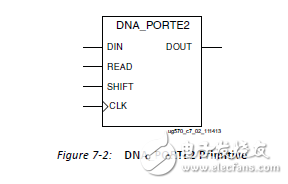

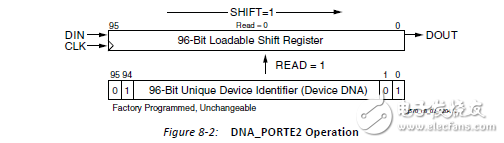

接下来说一下这个源语和源语相关的运用办法,这个源语本质上便是读取FUSE寄存器表里边的FUSE_DNA寄存器,里边还包含了一个移位寄存器,源语中的接口本质上都是操作移位寄存器,这个移位寄存器的长度和器材类型有关,是56或许96bit。源语里边的READ信号,是用于把DNA的值装载到移位寄存器里边,DIN是移位寄存器的输入,DOUT是移位寄存器的输出,SHIFT是移位寄存器的移位使能,CLK是移位寄存器的操作时钟,官方供给的源语模型和时序图如下,

关于用户来说,调用这个源语,咱们只需要依照操作移位寄存器的流程操作就好了,咱们意图是读出源语里边的移位寄存器的值,所以咱们规划的思路应该是首要拉高READ先让移位寄存器装载DNA的值,然后在时钟上升沿使能SHIFT,这姿态就能让移位寄存器里边的值移位出来,下面是中心代码:

module dna_read(

input sys_clk,

input dna_read_rdy,

output [95:0] dna_read_dat,

output dna_read_vld);

wire dna_dout;

wire dna_read;

wire dna_shift;

DNA_PORTE2 #(

.SIM_DNA_VALUE (96‘d0)

)DNA_PORTE2_inst(

.DOUT (dna_dout),

.CLK (sys_clk),

.DIN (dna_dout),

.READ (dna_read),

.SHIFT (dna_shift)

);

reg [95:0] dna_reg = 0;

reg [7:0] dna_cnt = 0;

always @ (posedge sys_clk)

begin

if(dna_read_rdy) begin

dna_cnt 《= dna_cnt + 1;

end

else begin

dna_cnt 《= 0;

end

end

// load dna data from the fuse dna register

assign dna_read = dna_cnt == 8’d63;

// for ultrascale

assign dna_shift = (dna_cnt 》= 8‘d100) && (dna_cnt 《= 195);

always @ (posedge sys_clk)

begin

dna_reg 《= {dna_dout,dna_reg[95:1]};

end

assign dna_read_dat = dna_reg;

assign dna_read_vld = dna_cnt == 8’d196;

endmodule

这是一个axis总线的模块,在dna_read_rdy拉高表明外部准备好接纳数据,这时分模块读取DNA的值,然后送出去给外部模块,外部模块收到数据和dna_read_vld信号,则拉低dna_read_rdy,完结一次dna数值传输流程。