现在干流的FPGA仍是根据查找表技能的,现已远远超出了从前版别的根本功用,并且整合了常用功用(如RAM、时钟办理和DSP)的硬核(ASIC型)模块。FPGA芯片主要由7部分完结,分别为:可编程输入输出单元、根本可编程逻辑单元、完好的时钟办理、嵌入块式RAM、丰厚的布线资源、内嵌的底层功用单元和内嵌专用硬件模块。

fpga芯片体系结构图

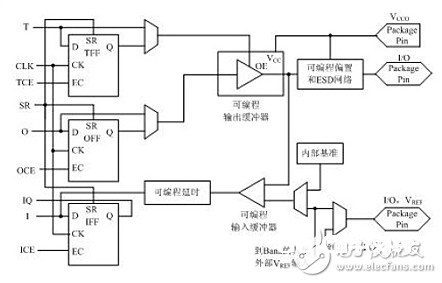

1. 可编程输入输出单元(IOB)

可编程输入/ 输出单元简称I/O 单元,是芯片与外界电路的接口部分,完结不同电气特性下对输入/ 输出信号的驱动与匹配要求,其暗示结构如下图 所示。FPGA 内的I/O 按组分类,每组都能够独立地支撑不同的I/O规范。通过软件的灵敏装备,可适配不同的电气规范与I/O 物理特性,能够调整驱动电流的巨细,能够改变上、下拉电阻。现在,I/O 口的频率也越来越高,一些高端的FPGA 通过DDR 寄存器技能能够支撑高达2Gbps 的数据速率。

IOB内部结构

外部输入信号能够通过IOB 模块的存储单元输入到FPGA 的内部,也能够直接输入FPGA 内部。当外部输入信号通过IOB 模块的存储单元输入到FPGA 内部时,其坚持时刻(Hold TIme) 的要求能够下降,一般默以为0。为了便于办理和习惯多种电器规范,FPGA 的IOB 被划分为若干个组(bank),每个bank 的接口规范由其接口电压VCCO 决议,一个bank 只能有一种VCCO,但不同bank 的VCCO 能够不同。只要相同电气规范的端口才干衔接在一起,VCCO 电压相同是接口规范的根本条件。

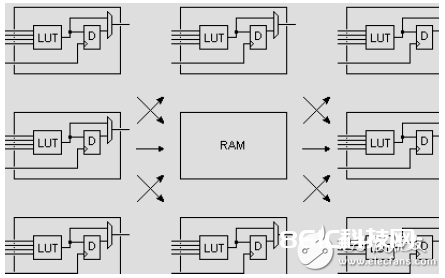

2.根本可编程逻辑单元

FPGA的根本可编程逻辑单元是由查找表(LUT)和寄存器(Register)组成的,查找表完结纯组合逻辑功用。FPGA内部寄存器可装备为带同步/异步复位和置位、时钟使能的触发器,也能够装备成为锁存器。FPGA一般依靠寄存器完结同步时序逻辑设计。一般来说,比较经典的根本可编程单元的装备是一个寄存器加一个查找表,但不同厂商的寄存器和查找表的内部结构有必定的差异,并且寄存器和查找表的组合形式也不同。

学习底层装备单元的LUT和Register比率的一个重要意义在于器材选型和规划预算。因为FPGA内部除了根本可编程逻辑单元外,还有嵌入式的RAM、PLL或者是DLL,专用的Hard IP Core等,这些模块也能等效出必定规划的体系门,所以简略科学的办法是用器材的Register或LUT的数量衡量。

3.数字时钟办理模块(DCM)

业界大多数FPGA 均供给数字时钟办理( 赛灵思公司的悉数FPGA 均具有这种特性)。赛灵思公司推出最先进的FPGA 供给数字时钟办理和相位环路确定。相位环路确定能够供给准确的时钟归纳,且能够下降颤动,并完成过滤功用。

4. 嵌入式块RAM(BRAM)

大多数FPGA都具有内嵌的块RAM,这大大拓宽了FPGA的使用规模和灵敏性。块RAM可被装备为单端口RAM、双端口RAM、内容地址存储器 (CAM)以及FIFO等常用存储结构。CAM存储器在其内部的每个存储单元中都有一个比较逻辑,写入 CAM中的数据会和内部的每一个数据进行比较,并回来与端口数据相同的一切数据的地址,因而在路由的地址交换器中有广泛的使用。除了块RAM,还能够将 FPGA中的LUT灵敏地装备成RAM、ROM和FIFO等结构。在实践使用中,芯片内部块RAM的数量也是挑选芯片的一个重要因素。

内嵌的块RAM