引 言

依据进步结构的小波改换办法,运用FPGA 可编程特性可完成多种小波改换。进步结构(LS :Lifting Scheme) 是由Sweldens 等人在近几年提出的一种小波改换办法,用它的结构结构能有效地核算DWT。关于较长的滤波器,LS 的操作次数比滤波器组的操作办法削减将近一半,更适合硬件完成。作者依据进步小波改换的结构式结构,运用FPGA 可彻底重构的特色结构不同的小波改换核,以满意不同运用场合的要求。在结构规划中选用由下至上的规划办法,每个进步进程都由一些可编程的参数来表明,确保了每个进程均可重构。这些参数包含用于表明数据的位数和每个内部数学模块的通道深度。在逻辑归纳时按不同小波的要求,改动参数可得到不同的成果。以图画处理中常用的(5 ,3)滤波器为例阐明依托FPGA 的重组特性完成滤波器的小波改换核办法。试验成果表明,运用FPGA 规划的进步小波改换核能满意不同场合和不同运转的要求。

LS 小波改换理论

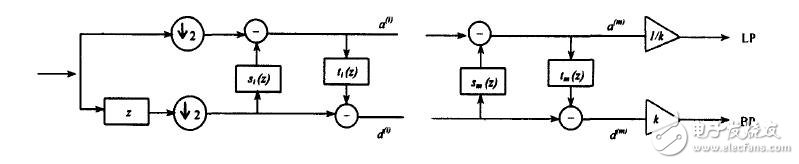

LS 改换进程如图1 所示,逆改换与正改换相同,仅仅次序相反。时刻离散的滤波器可由它的多项矩阵来表明,多项矩阵由脉冲响应的奇偶采样序列的Z 改换得到。LS 小波改换的本质是对经典小波滤波器选用Euclidean 算法的多项式进行分化。

图1 正向LS 改换

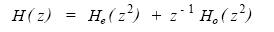

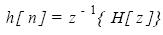

一个时刻离散的滤波器H( z ) 用多项式表明如下:

He ( z ) 和Ho ( z ) 各自从

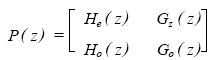

奇偶系数得到。剖析滤波器H ( z ) 和G( z ) 别离表明低通和高通,表明成多相矩阵为

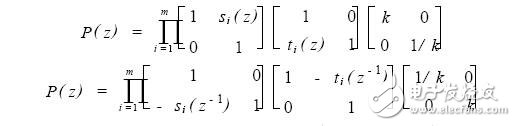

P( z ) 可被模拟为剖析滤波器。依据Euclidean算法可将P( z ) 和P( z ) 分化成:

上面的分化不是仅有的,可有几对{ si ( z ) } 和{ t i ( z ) } 滤波器,但关于核算DWT 一切的挑选是同等的。

FPGA 及进步核的完成

FPGA 及重构特性

FPGA(Field Programmable Gate Array ,现场可编程门阵列) 是超大规模集成电路(VL、SI) 技能和核算机辅助规划(CAD) 技能开展的成果。FPGA 器材集成度高、体积小、具有通过用户编程完成专门运用的功用。FPGA 一般由3 种可编程电路和1 个用于寄存编程数据的SRAM 组成。这3 种可编程电路是:可编程逻辑块CLB (Configurable Logic Block) 、输入/输出模块IOB ( I/O Block) 和互连资源IR( Interconnect Resource) 。因为依据小波的运用越来越广泛,所以运用FPGA 的灵敏结构完成可重构的进步结构小波改换核具有很高的运用价值和研讨价值。规划从根本的数学模块和逻辑模块开端,选用由下至上的规划办法,一切的库模块用VHDL 言语描绘,答应依据规划精度要求挑选每个单元的数据通道巨细。为了满意不同环境的需求,既要求能够改动独自模块的通道层深度,又要求考虑与其他设备的相容性。将进步办法与FPGA 的特性结合起来,使不同的进步小波改换在FPGA 上可满意不同运用场合的需求。

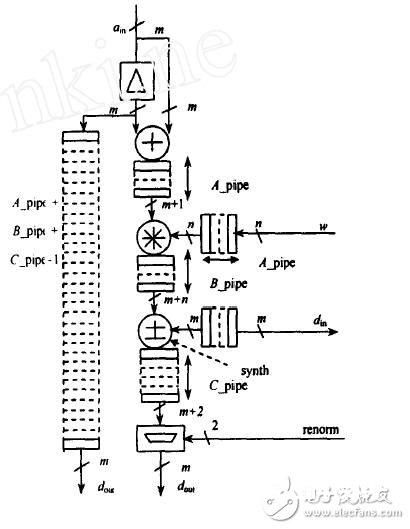

图2 进步核结构体

进步小波改换核的完成

如图1 所示,LS 改换是接连的独立的简略滤波操作进程,这个进程便是进步进程。由图1 可导出优化了的进步核结构体。近几年,选用JPEG2000 规范进行图画传输成为热门,许多文献中均提出了不同的进步小波改换结构体。

可是这些进步结构体大都只考虑可操作性,而疏忽了功耗和灵敏性。作者提出的进步核结构体(图2) 选用与以往不同的由下至上的规划办法。首要特色是指定了1 个独自的流水式的乘法单元和2个加法单元。乘法单元首要用于处理滤波器系数的对称问题,加法单元用于完成剖析或归纳的改换。

值得注意的是一切的通道层都可用所规划的库模块来摆放,因而为了确保内部IP 核数据流的同步性,有必要考虑前后穿插问题。例如,在加法输出时,现已放置了一个乘法器,答应对进步进程的成果进行归一化。选用这种规划办法,能取得最高的数据精度和最快的运转速度。此外,整数的数学单元更简单进行深层的流水操作,取得很高的数据吞吐量。图2 所提出的结构既考虑了可操作性又考虑了运用的灵敏性,因为进步了运转速度,所以下降了功耗。

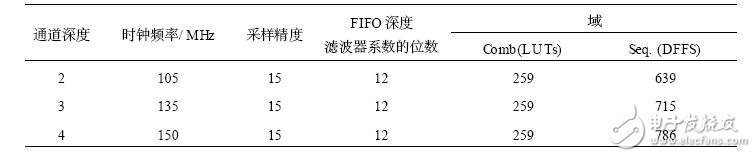

逻辑归纳成果

首要选用VHDL 言语来描绘由根本的可重构的数学模块和逻辑模块规划的改换核结构体,然后在MAX+PLUSⅡ集成环境下进行功用仿真,完成所需改换核,最终进行FPGA 逻辑归纳。在Altera1 公司的FLEX10K上规划的结构体,通过逻辑归纳得到很满意的成果,见表1 。表1 的成果直接由逻辑归纳得到,没有考虑各种客观因素引起的延时。在规划流程进程之后的安放运转进程中,可进行更准确的时序剖析。别的,为了取得完好的剖析成果,需参阅FPGA 厂家供给的目标估量功率耗费,运用时应挑选功耗小的可编程器件,更好地满意不同运用环境的要求。以(5 ,3) 滤波器为例,核算(5 ,3) 小波需求4个进步核的叠加,所提出的结构体核算正向或逆向(5 ,3)DWT ,对每帧像素1400×1400 选用15位采样数和12位组成滤波器系数,以全时钟频率运转,进行5 层分化、重构,每秒钟能处理25 帧图画,功耗为267.6 mW。

表1 进步核归纳成果

结束语

提出的可重构的进步核结构体,选用特别的即从下至上的规划办法,确保了最大极限地重复运用性和重构特性。仿真成果阐明,进步小波改换核的结构体不管在处理才能和功耗方面都取得了很好的成果,尤其在处理速度上,能满意图画处理实时性要求。将来的进一步开展是将更多的自在参数参加根本的算术模块中,确保结构体具有更好的操作性,而且使功率耗费削减,能满意不同运用场合的需求,对下降设备本钱,进步运用功率有实际意义。