导言

高精度时刻基准已经成为通讯、电力、工业操控等范畴的根底确保渠道之一。时统设备一般选用晶体振荡器作为频率规范,但都因为晶振老化和温度改变等原因导致其频率长时刻安稳度差。跟着GPS技能的开展和运用,运用GPS作为精确时刻源的优秀特性来同步本地时钟信息。但在实践中因为GPS供给的1pps信号常常遭到搅扰,如磁场搅扰,多径差错等,形成误将搅扰信号作为正常的1pps信号或GPS信号盯梢丢掉等问题,导致测控体系呈现差错过大现象,精度和安稳性难以确保。故1pps信号不能直接从GPS接纳板作为精确的同步信号,有必要经过技能处理,使其坚持高精度和作业接连安稳性。现在针对上述问题文献多运用分立器材或单片机作为主操控器,需求增加外围时刻距离丈量或鉴持平电路,不适宜用于压控晶振频率较高的场合。

本文是运用GPS供给的1pps秒脉冲信号,为处理上述问题,在FPGA(fieldprogrammablegatearray)的根底上运用搅扰秒脉冲信号消除和差错频率均匀运算等办法,削减外围电路,既消减了GPS时钟信号的随机搅扰差错,又消除了本地晶振时钟信号的累计差错,然后操控本地压控晶振输出频率,进步晶振的长时刻安稳性。

1、频率操控体系结构及作业原理

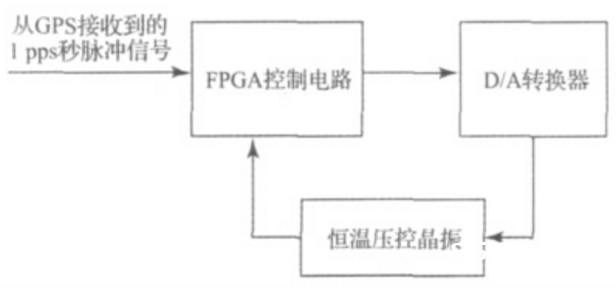

FPGA频率操控体系整体结构原理框图如图1所示。体系输入是GPS接纳机在盯梢卫星时发生的1pps秒脉冲信号,逻辑电平输出,高电平持续时刻为1.01±0.01ms,以高电平的上升沿作为秒脉冲信号输出的基准时刻[9-10]。数字操控电路为FPGA操控电路,主控芯片为EP1C6-——144TQFP,能够重复软件编程,修正电路计划,外围硬件电路少,可靠性高。该电路将丈量本地压控晶振发生同步秒脉冲与1pps秒脉冲之间的相位差,选用搅扰秒脉冲信号消除和差错频率均匀运算等办法得到同步信号所需的相对频差。D/A转化器将相对频差转化为模仿操控电压,反应到本地恒温压控晶振的操控端调整高稳晶振的频率信号,减小与1pps秒脉冲的同步相差,然后进步振荡器高频精确度和长时刻安稳性,完成数字同步时钟的征服功用。

图1 FPGA频率操控体系整体结构原理

2、体系功用规划

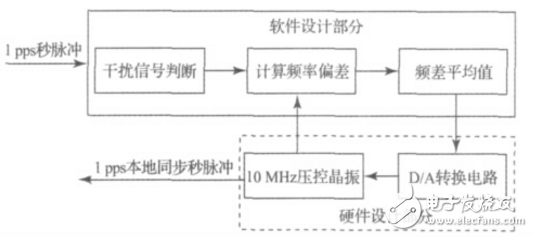

体系功用规划首要包含硬件规划和软件规划2大部分,如图2所示。软件完成部分为:以VHDL编程言语完成GPS信号对晶振的征服功用,包含怎么消除GPS搅扰信号的办法,完成GPS同步时钟的办法,丢掉GPS信号后持续对晶振频率的征服操控,以及输出本地同步秒时钟信号。硬件完成部分为:D/A转化器供给转化后的模仿操控电压,恒温压控晶振依据模仿电压校准频率,并反应回FPGA处理器。

图2 体系功用规划

2.1、搅扰信号判别及消除

1pps秒脉冲信号以方波方式输出,高电平表明有秒脉冲输出,高电平脉冲宽度不是安稳值,持续时刻约为1ms,有0.01ms的差错,这就导致在1pps信号高电平期间的晶振计数值不持平。别的因为搅扰,接遭到的1pps信号中有搅扰脉冲信号,若把搅扰脉冲上升沿作为1pps信号的上升沿开端计数,计数成果必定不精确,所测得的晶振频率值与实践值差错过大。需求软件判别出搅扰信号并作出处理。

数字电路中搅扰脉冲的高电平持续时刻多数是微秒级,很少有超越1pps秒脉冲信号高电平持续时刻的,因而以秒脉冲高电平持续时刻作为判别依据,以本地压控晶振计数来完成计时功用。晶振标称频率是10MHz,2ms的计数值理论值为20000。在晶振高频脉冲输出工作发生clk‘eventandclk=’1‘的前提下,遇到1pps信号事情sclk’eventandsclk=‘1’开端计数,一起用寄存器counter4保存计数值,如超越2ms高电平的脉冲信号为正常1pps信号,若小于2ms则认为是搅扰信号,寄存器counter4计数值回来至该信号脉冲上升沿前的计数值。

2.2、频率差错值核算

为了校准晶振输出信号频率,需求将频率差错值核算出来,核算出对应调整数值,经过D/A转化器变为模仿电压,并反应给恒温压控晶振,以此到达调整的意图。能够用一元二次回归模型对输出的晶振秒时钟与GPS秒时钟的频率差错进行剖析。

因为本地恒温压控晶振短期安稳度高,小于1&TImes;10-10/s,能够不考虑晶振秒脉冲的随机差错,只考虑累积差错发生的频率差错及线性漂移差错,晶振分频秒时刻序列的第x个秒时钟的时刻差错e(x)为:

e(x)=a+bx+cx^2(1)

式中:a为秒时刻序列的初始差错,b为频率差错的差错系数,c为频率线性漂移的差错系数。

经过一元二次回归剖析可得式(1)的晶振差错估计值遵守正态分布:

^e(x)=^a+^bx+^cx2~N(a+bx+cx2,D(^e))(2)

依据回归剖析,可得,当x=n时,秒时钟的时刻差错的方差有最大值Dmax。经过剖析上式最大方差Dmax与回归剖析样本数n之间联系得,样本数n越大,最大方差Dmax越小,也便是晶振分频秒脉冲与GPS秒时钟的差错越小。但样本数n不能取无限大,受FPGA软硬件资源的约束,一般来说,当n≥3时,调整后的晶振分频秒脉冲的时刻差错小于GPS秒时钟的差错,能够满足要求。

上述办法需求在1s内累积晶振计数值,需求有24位的寄存器存储计数值,对芯片运算处理速度要求过高,且占用较多FPGA资源,影响操控速度。在此根底上,本文选用差错频率均匀运算的办法。行将每s内晶振分频秒脉冲与GPS秒时钟差错值求出,每3个样本时刻作为操控的循环周期,3s累加内总差错值为Z=Z1+Z2+Z3,求得循环周期均匀差错值Z0=Z/3,鄙人一循环样本周期内,每秒反应给晶振,调整晶振输出频率。

晶振分频秒脉冲与GPS秒时钟差错值具体办法为:用寄存器counter1存入每s内晶振的计数值,理论计数值为1&TImes;107个晶振脉冲。寄存器counter2为秒时钟计数器,当判别1pps信号为非搅扰信号后,寄存器counter2自加1计数。正常秒脉冲频率的差错值在±128规模内,超越规模则是超差信号,不作处理,故运用寄存器counter1的低8位作为差错频率的寄存器counter3。当counter2值到达循环操控样本数3时,做均匀差错频率核算,成果存入寄存器——counter7输出。

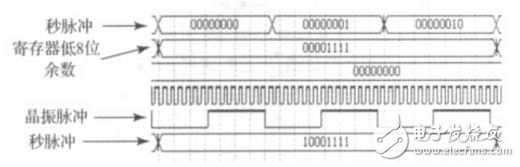

计划仿真波形如图3所示。因理论计数值较大,实践程序运算时刻过长,成果难以清楚调查,对1个秒脉冲时刻内的晶振脉冲数减小,为15个晶振脉冲。数据减小不影响计划的验证。能够看出,在counter2寄存器计数到3个秒脉冲的1个操控循环周期内,低8位的频率均匀差错为15,counter7寄存器得到的余数也为0001111。成果表明该计划能够精确得到频率差错值。

图3 计划仿真波形