1 导言

在工业进程操控设备、仪器仪表和主动测验设备中常常需求软件装备输出规模精度为16位的模拟输出。针对这种需求,提出了一种根据LTC2753的电路规划,可供给一切规范工业规模,电路规划简略、紧凑,精度高且可软件操控。

2 LTC2753简介

LTC2753-16具有软件可编程设置、低功率和准确DC功用使其适用于ATE数据收集模块。此外,该器材还具有杰出的AC功用,包含仅为2μs的安稳时刻和l nV·s的低搅扰脉冲。这对波形的发生十分要害。低搅扰下降了DAC中代码改动时的瞬态电压。快速安稳和低搅扰削减谐波失真,能够发生高效、铲除低噪声的输出波形。LTC2753选用一个双向输入/输出并行接口,完结任何片内存放器的回读以及DAC输出规模设置。

LTC2753一14和LTC2753—12分别是引脚兼容的14位和12位器材。选用7 mmx7 mm QFN一48封装,为优化终究产品性价比供给了引脚兼容和代码兼容的系列器材。

LTC2753系列器材具有以下首要特性:6种可设置输出规模:单极:0~5 V,0~10 V,双极:±5 V、±10 V、±2.5 V、一2.5~7.5 V;最大16位INL差错:±1 LSB (整个温度规模内);低电源电流(最大值为1μA);在整个温度规模内可确保单调;低搅扰脉冲1 nV/s;2.7~5.5 V单电源作业;2μs快速安稳时刻至±lLSB;具有数据和回读的并行接口;在任何输出规模内异步CLR引脚将DAC输出铲除至0 V;上电复位将DAC输出铲除至0 V;48引脚7 mmx7 mm QFN封装。

3、 典型使用

图1给出LTC2753的典型使用电路图。

3.1 输出规模

当外接5 V参阅电压时,LTC2753可供给6种输出规模。参阅电压为2 V时,输出规模为:0~2 V、O~4 V、±1 V、±2 V、±4 V和-1~3 V。除2 V和5 V之外,其他输出规模都随参阅电压呈线性改动。

3.2 数字部分

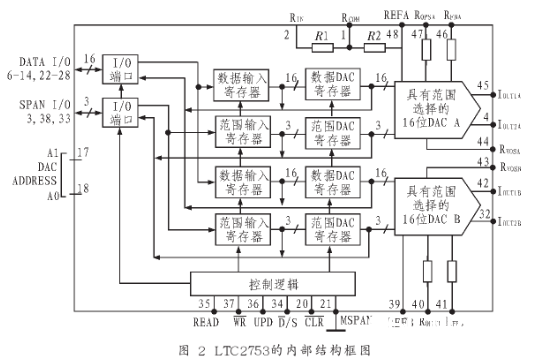

LTC2753的每个DAC都有4个内部存放器,共有8个存放器,如图2所示。每个DCC通道都有2组双缓冲存放器,一组用于存放数据,一组用于存放输出规模。双缓冲存放器具有同步更新规模和编码功用。当改动电压输出规模时,双缓冲功用使电压滑润转化,无毛刺发生。乘法DAC同步更新。每组双缓冲存放器是由输入存放器和DAC存放器组成。输入存放器为坚持存放器,当数据载入输入存放器需经过一个写操作,而DAC输出不受影响。另一方面,DAC存放器直接操控DAC输出电压或输出规模,将与其衔接的输入存放器中的内容复制到DAC存放器,改动DAC存放器内容,则需经过一个更新操作。

3.3 写和更新操作

履行一次写操作:将D/S引脚与WR引脚置低,直接经过16位微处理器总线将数据写入输入存放器。UPD引脚置高,将输入存放器贮存的数据复制到DAC存放器,完结一次更新操作。数据与规模一起更新;除非输入存放器的值先经一个写操作被改动,不然DAC存放器的值不会改动。

规模输入存放器的载入:将D/S引脚置高,WR引脚置低。除了并行位的个数不同外,规模存放器与数据存放器结构相同。规模存放器有3位,而数据存放器有12、14或16位。若要数据存放器和规模存放器在作业形式下坚持通明,则要将WR引脚置低,UPD置高,阻挠了输出搅扰脉冲的添加。限变器在UPD引脚的上升沿有用。

当WR和UPD连在一起由一单时钟信号驱动时,输入存放器和DAC存放器则以主从分配联系,或是边缘触发、装备的形式作业。在时钟的下降沿,数据位存入输入存放器,跟着时钟上升沿的到来,进入DAC存放器。

SPAN引脚S2~SO用数据LSB同享数据,一起将数据和规模操控在一个16位数据总线上,规模和数据不能一起进行写或读操作。

异步CLR引脚在任何输出规模内都可将DAC输出铲除至O V,CLR对一切数据存放器复位,而不搅扰规模存放器。

这些设备也可经过上电复位将DAC的输出电压在任何输出规模初始化至0 V。假如是软件规模装备,DAC上电至0~5 V之间;若是手动规模,DAC选用恰当编码,选用手动上电。

3.4 手动规模装备

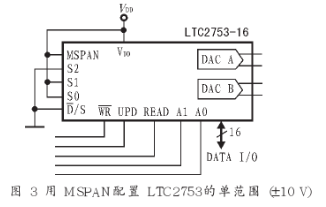

若要装备LTC2753为单规模,将MSPAN引脚置高,D/S引脚置地。一般,要求的输出规模由SPAN I/O引脚(S2~SO)设定,但经过直接接地或接电源编程设置的,如图3所示。在这个装备中,DAC的通道都能够在上电时对挑选的输出规模初始化。当设定手动规模操作时,SPAN引脚的回读功用无效。

3.5 回读功用

8个接口存放器中任一个的内容都从I/O端口回读。I/O引脚分红数据和规模两部分。数据I/0端口由引脚DO~D15组成,规模I/O口由SO~S2组成。

每个DAC通道有一组数据存放器用于操控和回读数据I/O端口,一组规模存放器操控和回读规模I/O端口。

当DAC通道和I/O端口挑选后,将READ引脚设置为逻辑高电平发动回读功用。当READ引脚置低时,I/O端口高阻抗数字输入,回读进程变成低阻抗逻辑输出。

挑选DAC通道选用地址引脚A1和A0,挑选I/O端口(数据或规模)用于回读选用D/S引脚。在回读进程中,已选的I/O口引脚用作逻辑输出,而未选用的I/O口引脚坚持高阻抗输入状况。

选用DAC通道和I/O口,READ置高,用于UPD引脚的输入和DAC存放器。UPD引脚有两个功用:当READ置低时,具有更新功用;当READ置高,更新功用无效,UPD引脚挑选输入或DAC存放器的回读。

回读功用是在输入存放器写入数据后,查看其内容,在DAC存放器更新新数据之前检测DAC存放器。已选端口的存放器是其I/O引脚的输出。

要想回读DAC存放器,坚持UPD为低,READ置高,再将UPD置高,并挑选DAC存放器,被选的DAC存放器由I/O引脚输出。假如回读后不要求更新,必须将UPD置低,再将READ置低,不然UPD引脚将会复位到之前功用并更新DAC。

3.6 体系偏移量调理

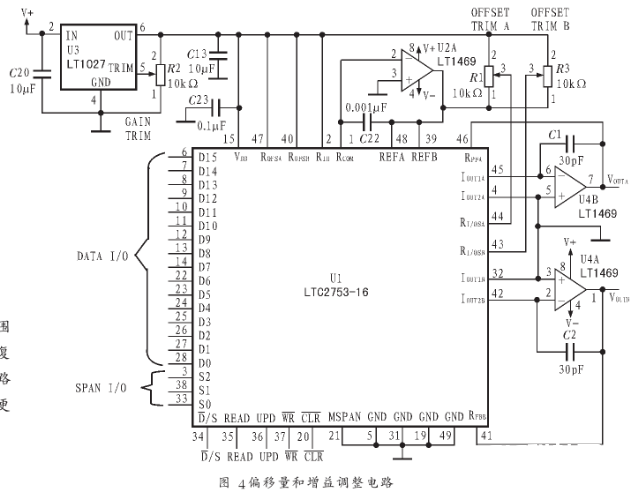

体系的RVOSA和RVOSB偏移量调整引脚是为了补偿整个体系偏移量,如图4所示。为了能够抗搅扰和轻松调整,电压操控被削弱为DAC输出,LTl027供给电源RVOSX引脚有一只l MΩ的输入阻抗。为了维护LTC2753的功用,需选用一只至少10 kΩ的等效阻抗驱动该引脚,缩短任何无用的体系偏移量调理引脚IOUT2。

3.7 作业放大器的挑选

因为LTC2753—16具有16位的高精度。因此在挑选作业放大器要慎重考虑,以期到达最佳状况。而作业放大器偏移量的INL和DNL的灵敏度相对上一代的乘法DAC已大大下降。

4、 结语

创立一个高精度、多种输出规模软件装备的16位DAC不再是一件杂乱、贵重的规划。现在一个简练的电路规划发生了更小的尺度、低成本和更高精度的报答。

责任编辑:gt